БЛОКИ ВВОДА-ВЫВОДА ПЛИС ТИПА FPGA

В наиболее типичном варианте FPGА представляет собою микросхему высокого уровня интеграции, содержащую во внутренней области матрицу функциональных блоков и систему их межсоединений, размещенную между строками и столбцами матрицы, а в периферийной области — блоки ввода/вывода.

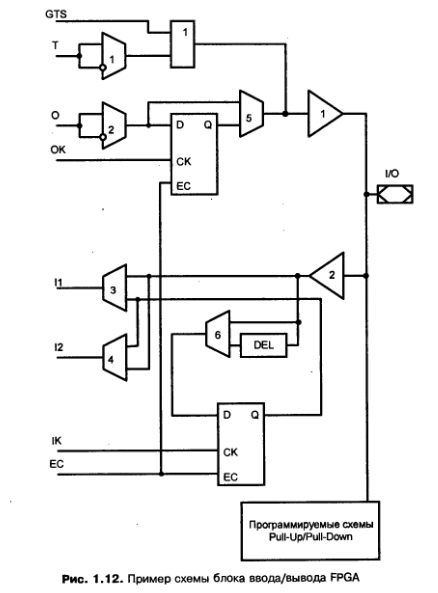

Блоки ввода/вывода на примере микросхем семейства Spartan фирмы Xilinx показаны на рисунке, обеспечивают интерфейс между выводами корпуса FPGA и ее внутренними логическими схемами. Каждому выводу корпуса придается блок ввода/вывода БВВ, который может быть конфигурирован как вход, выход или двунаправленный вывод.

Работа БВВ как выходного блока обслуживается элементами: выходным буфером 1, триггером 1, мультиплексорами 1, 2, 5 и логической схемой ИЛИ. Выводимый сигнал О можно получать в прямой или инверсной форме в зависимости от программирования мультиплексора 2. Этот сигнал может передаваться на выходной буфер непосредственно или сниматься с триггера при соответствующем программировании мультиплексоpa 5. Сигналы Т и GTS (Global Tri-Siate), согласно логике ИЛИ, управляют переводом буфера в третье состояние, причем активный уровень сигнала Т программируется с помощью мультиплексора 1.

Работа БВВ как выходного блока обслуживается элементами: выходным буфером 1, триггером 1, мультиплексорами 1, 2, 5 и логической схемой ИЛИ. Выводимый сигнал О можно получать в прямой или инверсной форме в зависимости от программирования мультиплексора 2. Этот сигнал может передаваться на выходной буфер непосредственно или сниматься с триггера при соответствующем программировании мультиплексоpa 5. Сигналы Т и GTS (Global Tri-Siate), согласно логике ИЛИ, управляют переводом буфера в третье состояние, причем активный уровень сигнала Т программируется с помощью мультиплексора 1.

Тракт ввода сигналов содержит входной буфер 2, триггер 2, программируемые мультиплексоры 3, 4, 6, элемент задержки ЭЗ и программируемые схемы задания определенных потенциалов выводу, к которому не подключен вводимый или выводимый сигнал (схемы Pull -Up/Pull -Down). Вводимый сигнал в зависимости от программирования мультиплексоров 3 и 4 или поступает непосредственно в систему коммутации FPGA по входным линиям I1 и I2, или же фиксируется триггером и с его выхода передается в эти линии. Триггеры могут конфигурироваться как тактируемые фронтом или как защелки (D-триггеры, управляемые уровнем). Выбор осуществляется присвоением триггеру соответствующего библиотечного символа. В цепи передачи сигнала на триггер 2 могут быть включены элементы задержки (при передаче сигнала через нижний вход мультиплексора 6). Включение задержки гарантирует необходимые временные соотношения между входными сигналами триггера D и глобальным сигналом тактирования. Входной буфер может конфигурироваться для восприятия входных сигналов с пороговым значением ТТЛ (1,2 В) или КМОП (0,5 Ucc ). Выходные уровни тоже конфигурируются, две глобальные регулировки входных порогов и выходных уровней независимы.

|

|

|

СИСТЕМА МЕЖСОЕДИНЕНИЙ ПЛИС ТИПА FPGA

В наиболее типичном варианте FPGА представляет собою микросхему высокого уровня интеграции, содержащую во внутренней области матрицу функциональных блоков и систему их межсоединений, размещенную между строками и столбцами матрицы, а в периферийной области — блоки ввода/вывода.

|

|

|

Для систем межсоединений FPGA организация непрерывных соединений затруднительна. Для них характерны сегментированные линии связей, составленные из отдельных проводящих отрезков — сегментов.

Для систем межсоединений FPGA организация непрерывных соединений затруднительна. Для них характерны сегментированные линии связей, составленные из отдельных проводящих отрезков — сегментов.

Сегменты соединяются в нужную цепь с помощью программируемых ключей. Выбор длины сегментов должен учитывать, что короткие сегменты затрудняют передачу сигналов на большие расстояния, а длинные сегменты неудобны для коротких связей. Поэтому система межсоединений имеет иерархический характер,и в ней сочетаются различные типы сегментов.

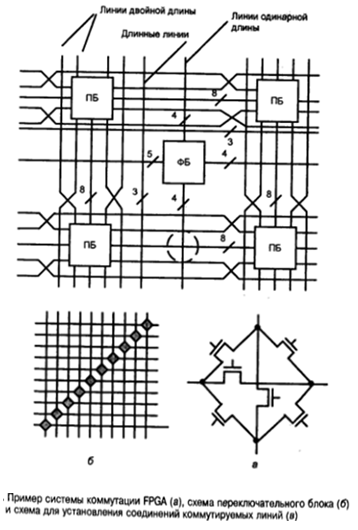

Систему межсоединений FPGA образуют сегментированные линии и переключательные блоки ПБ (PSM, Programmable Switching Matrix). Функциональные блоки имеют квадратные геометрические очертания, их выводы распределены по всем сторонам квадрата для облегчения коммутируемости. Для межсоединений функциональных блоков во внутренней области кристалла имеются три типа связей: одинарной длины, двойной длины и длинные линии. На пересечениях вертикальных и горизонтальных каналов расположены переключательные блоки.

Сигнал, поступающий в ПБ по какой-либо линии может быть направлен вверх, вниз или прямо в зависимости от того, какой транзистор будет открыт при конфигурировании FPGA. Возможна и одновременная передача сигнала по нескольким направлениям, если требуется его разветвление. Линии одинарной длины осуществляют, преимущественно, межсоединения соседних или близлежащих ФБ, линии двойной длины огибают переключательные блоки, соседние по отношению к данному, и проходят к следующим, чем облегчается установление более длинных связей. По три длинных линии, пересекающих весь кристалл по длине (ширине), реализуются сверху, снизу и по обоим бокам ФБ. Линии двойной длины сгруппированы в пары, обеспечивающих более быструю и эффективную передачу сигналов на средние расстояния. Длинные линии, рассчитанные на передачу сигналов на большие расстояния и при большой нагрузке, имеют в середине ключ, разделяющий линию на две части. Кроме системы коммутации для функциональных блоков FPGA может иметь дополнительные трассировочные ресурсы. Эти ресурсы позволяют изменять назначение вводов/выводов микросхемы. В число FPGA по принятой классификации попадают микросхемы с числом эквивалентных вентилей около 200тыс-20млн, системными частотами поддерживающими DDR3 до 1ГГц и более, числом пользовательских выводов до 2500 контактов (BGA). Лидером в производстве однократно программируемых FPGA считают фирму Actel, а в производстве FPGA с триггерной памятью конфигурации – фирму Xilinx.

|

|

|

Дата добавления: 2020-04-08; просмотров: 242; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!