ПАМЯТЬ КОНФИГУРАЦИИ ПЛИС, ПИТАНИЕ СОВРЕМЕННЫХ ПЛИС

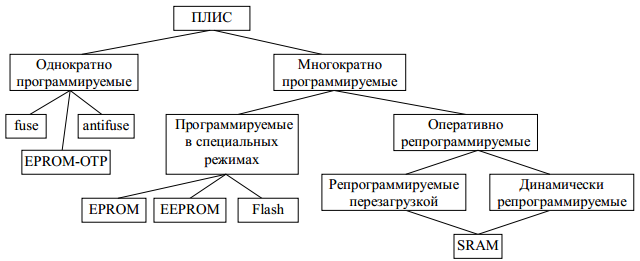

Память конфигурации ПЛИС – это память, в которую записывается конфигурация (настройка) ПЛИС. Классификация ПЛИС по типу конфигурации или же по типу используемой памяти приведена ниже:

fuse – плавкие перемычки; antifuse – пробивные перемычки; EPROM-OTP – программируемыми элементами являются однозатворные МОП-транзисторы, изначально заряда на затворе нет (проводимости транзистором также нет), после введения в затвор заряда (который сохраняется в течение десятков лет) приводит к возникновению в транзисторе проводящего канала.

EPROM – память на МОП-транзисторах со стиранием с помощью ультрафиолета; EEPROM - электрически стираемое перепрограммируемое ПЗУ; flash – «молния» - та же EEPROM в которой запись и чтение происходит целыми блоками. Рассмотренные выше однократно и многократно программируемые типы памяти являются энергонезависимыми.

В оперативно репрограммируемых ПЛИС конфигурация задается с помощью загрузки файла в "теневую" триггерную память Память конфигурации – обычная статическая (триггерная), типа SRAM, Static Random Access Memory. Загрузка памяти производится с высокой скоростью последовательным потоком битов/байтов. Элементом с программируемой проводимостью служит обычный МОП-транзистор, управляемый триггером памяти конфигурации. Триггерная память не является энергонезависимой.

Основная функция системы управления питанием ПЛИС обеспечить ПЛИС и сопряженные с ней схемы стабилизированным напряжением во всех режимах работы в точно установленных пределах изменения нагрузки. По потребляемой мощности ПЛИС значительно отличаются от других интегральных схем.

|

|

|

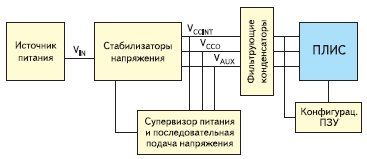

В целом структурная схема системы питания ПЛИС состоит из первичного источника питания, формирующего входное напряжение (Vin) для стабилизатора напряжения, который устанавливает последовательность подачи различных напряжений. Супервизор следит за уровнями напряжений. Цепочка шунтирующих конденсаторов вокруг ПЛИС распределяет рабочий ток между потребителями и снижает уровень высокочастотного шума. Уровни питающих напряжений ПЛИС

Для питания разных функциональных блоков ПЛИС используются различные уровни напряжения. Все ПЛИС нуждаются в источнике напряжения питания ядра, в отдельном источнике напряжения питания для блоков ввода-вывода, источнике опорных напряжений и источнике напряжения для дополнительных функций.

Для питания разных функциональных блоков ПЛИС используются различные уровни напряжения. Все ПЛИС нуждаются в источнике напряжения питания ядра, в отдельном источнике напряжения питания для блоков ввода-вывода, источнике опорных напряжений и источнике напряжения для дополнительных функций.

СЛОЖНЫЕ ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ УСТРОЙСТВА. ОБОБЩЕННАЯ СТРУКТУРА ПЛИС ТИПА CPLD

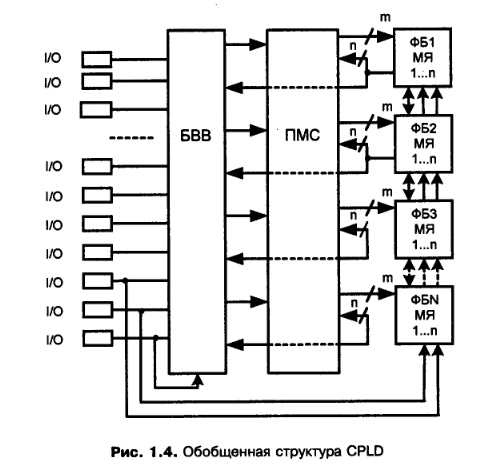

CPLD (Complex Programmable Logic Device) – сложные программируемые логические устройства. CPLD – это БИС, основными частями которой являются:

- PAL (Programmable Array Logic) подобные функциональные блоки (ФБ),

|

|

|

- система коммутации, позволяющая объединять функциональные блоки в единое устройство, выполненная в виде матрицы соединений,

- блоки ввода-вывода (БВВ).

CPLD за счёт PAL-подобной структуры идеально подходят для реализации сложных счётчиков, высокоскоростных дешифраторов адресных шин большой разрядности, коммутации-мультиплексирования потоков данных и построения разнообразных конечных автоматов. Они применяются в качестве периферии к стандартным микроконтроллерам и микропроцессорам.

Все составные части CPLD программируются. Обобщенная структура CPLD показана на рисунке.

Через ФБ (FB) обозначены функциональные блоки, число которых N зависит от уровня интеграции микросхемы. В каждом ФБ имеется n макр2оячеек МЯ. Функциональные блоки получают входные сигналы от программируемой матрицы соединений ПМС. Число таких сигналов т. Выходные сигналы ФБ поступают как в ПМС, так и в блоки ввода/вывода CPLD (БВВ). ПМС обеспечивает полную коммутируемость функциональных блоков, т. е. возможность подавать сигналы с любого их выхода на любой вход. Блоки ввода/вывода связаны с внешними двунаправленными выводами I/O, которые, в зависимости от программирования, могут быть использованы как входы или как выходы. Три нижних вывода либо специализируются для подачи на матрицу функциональных блоков сигналов GCK (Global Clocks) глобального тактирования, сигналов GSR (Global Set/Reset) глобальной установки/сброса и сигналов GTS (Global 3-state Control) глобального управления третьим состоянием выходных буферов, либо эти же выводы могут быть использованы для операций ввода/вывода.

|

|

|

Дата добавления: 2020-04-08; просмотров: 554; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!