МИКРОСХЕМЫ ТИПА ПРОГРАММИРОВАНИЯ МАТРИЧКАЯ ЛОГИКА. ИХ ОСНОВНЫЕ ПАРАМЕТРЫ

ИСТОРИЯ ПОЯВЛЕНИЯ МИКРОСХЕМ ПРОГРАММИРУЕМЫХ ЦИФРОВЫХ УСТРОЙСТВ. ПРЕДШЕВСТВЕННИКИ ПЛИС

Интегральная схема создана в 1959г. в США (Fairchild Motorola).

Первые программируемые логические устройства создавались на основе технологии биполярных программируемых ПЗУ с дополнительными логическими возможностями и свойствами. Фирма Signetics выпустила в 1972 году биполярную микросхему программируемой логической матрицы. Совершенствование архитектуры привело к созданию фирмой Monolithic Memories Inc. (MMI) в 1975–1976 годах микросхем программируемой матричной логики (PAL), монтируемых в 20- и 24-выводные корпуса и способных заменить до 20 имевшихся в продаже логических вентилей. В 1984-м фирма Altera выпустила первую микросхему CPLD содержащую 300 вентилей. И уже сегодня логическая емкость микросхем ПЛИС с конфигурационной флэш-памятью превышает 1 млн вентилей. К классу программируемых логических приборов относятся простые и сложные ПЛИС (SPLD и CPLD, соответственно), а также программируемые пользователем базовые матричные кристаллы (FPGA).

Программируемые логические интегральные схемы (ПЛИС) позволяют в сжатые сроки создавать высокоскоростные периферийные модули, шинные интерфейсы (PCI, USB), сетевые устройства, контроллеры и др.

ПЛИС - это цифровая интегральная схема с программируемой структурой.

1. однократно-программные (с плавкими перемычками, с пробиваемыми перемычками)

2. репрограммируемые (с ультрафиолетовым стиранием УПФ ПЗУ, с электрическим стиранием Flash, ЭСП ПЗУ)

|

|

|

Виды ПЛИС:

1. программируемые логические матрицы (PLA)

2. программируемая матричная логика (PAL)

3. базовые матричные кристаллы (GA)

МИКРОСХЕМЫ ТИПА ПРОГРАММИРУЕМАЯ ЛОГИЧЕСКАЯ МАТРИЦА. ИХ ОСНОВНЫЕ ПАРАМЕТРЫ. УПРОЩЕННАЯ СХЕМА

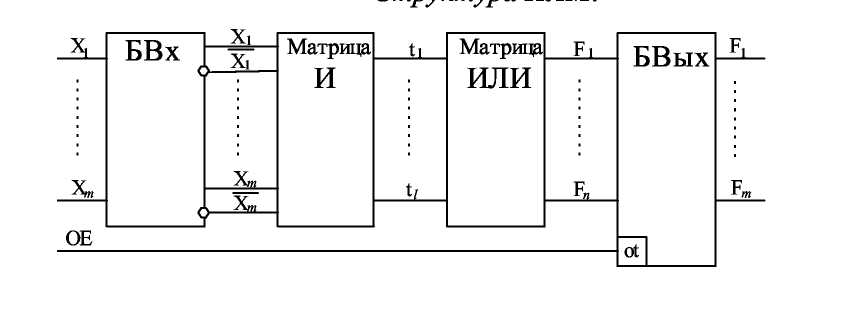

Программируемые логические матрицы (ПЛМ) появились к восьмидесятым годам. Основой служат последовательность программируемых матриц элементов «И» и «ИЛИ», а также блоки входных и выходных буферных каскадов (БВх и БВых). Вх буферные каскады преобразуют символы в парафазные, выходные обеспечивают нагрузочную способность. Структура ПЛМ (биполятная с плавкими перемычками)

Основные параметры ПЛМ:

- Число входов m;

- Число термов 1;

- Число выходов n;

- матрица И - конъюнкторы;

- матрица ИЛИ - дизъюнкторы.

Число формируемых термов равно числу коньюнкторов (И). Число дизьюнкторов (ИЛИ) равно числу вырабатываемых функций n.

ПЛМ реализует дизъюнктивную нормальную форму (ДНФ) воспроизводимых функций (двухуровневую логику).

Какие именно термы будут выработаны и какие комбинации этих термов составят выходные функции, определяется программированием ПЛМ.

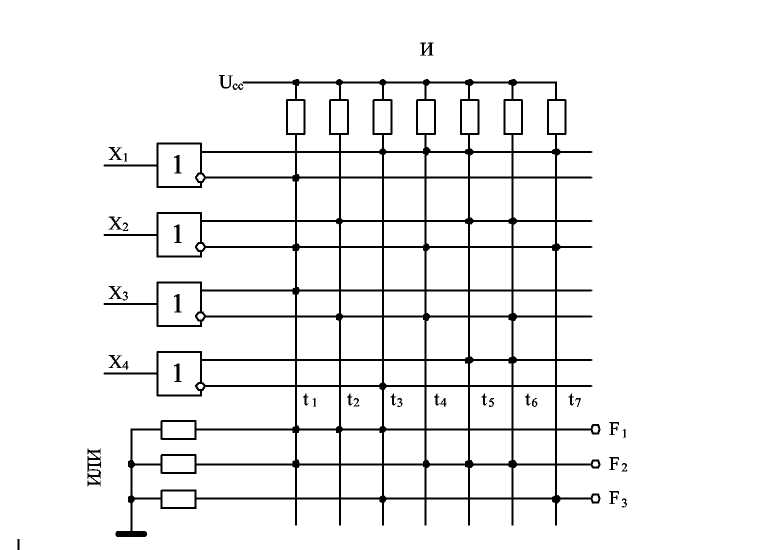

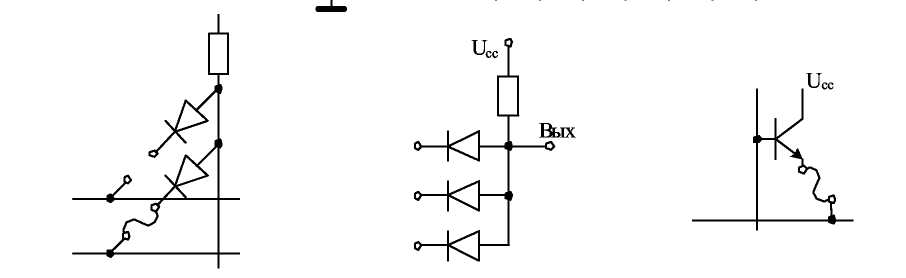

Схемотехника ПЛМ

|

|

|

Выпускаются ПЛМ как на основе биполярной технологии, так и на МОП-транзисторах. В матрицах имеются системы горизонтальных и вертикальных связей, в узлах, пересечения которых при программировании создаются или ликвидируются узлы связи. Реализуемые функции можно усложнять, вводя например один из выходов на вход. Тогда можно реализовать более сложную скобочную форму функции.

МИКРОСХЕМЫ ТИПА ПРОГРАММИРОВАНИЯ МАТРИЧКАЯ ЛОГИКА. ИХ ОСНОВНЫЕ ПАРАМЕТРЫ

Программируемая матричная логика (ПМЛ)

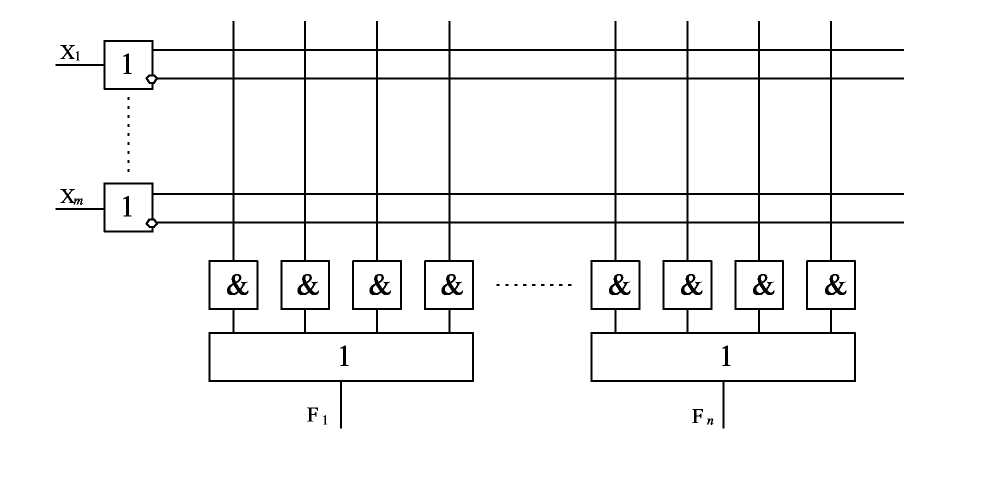

SPLD( Simple Programmable Logic Devices), т. е. простые программируемые логические устройства. По архитектуре эти ПЛИС делятся на подклассы программируемых логических матриц ПЛМ (PLA, Programmable Logic Arrays) и программируемой матричной логики ПМЛ (PAL. Programmable Arrays Logic, или GAL, Generic Array Logic).

Оба эти подкласса микросхем реализуют дизъюнктивные нормальные формы (ДНФ) переключательных функций, а их основными блоками являются две матрицы: матрица элементов И и матрица элементов ИЛИ, включенные последовательно. Такова структурная модель ПЛМ и ПМЛ. Технически они могут быть выполнены и как последовательность двух матриц элементов ИЛИ-НЕ.

В ПМЛ выработанные матрицей И термы поступают на фиксированную (непрограммируемую) матрицу элементов ИЛИ. Этоозначает жесткое заранее заданное распределение имеющихся термов между отдельными дизъюнкторами. Каждому дизъюнктору придаются свои собственные термы, и если для разных дизъюнкторов окажутся нужными одинаковые термы, придется вырабатывать их в матрице И несколько раз. Однако при этом программируемость матрицы ИЛИ исключается, что для многих задач в итоге существенно упрощает схему ПМЛ в сравнении со схемой ПЛМ.

|

|

|

Здесь выходы элементов матрицы «И» жестко распределены между элементами матрицы «ИЛИ».

В схеме ПМЛ m входов, n выходов и 4 n элементов «И», так как каждому элементу «ИЛИ» придается по 4 коньюнктора. В сравнении с ПЛМ эти ПЛИС имеют меньшую функциональную гибкость, но их изготовление и использование проще. Преимущества проявляются при проектировании несложных устройств.

4.ФУНКЦИОНАЛЬНЫЕ РАЗНОВИДНОСТИ ПЛМ И ПМЛ

SPLD, т.е. простые программируемые устройства, по архитектуре делятся на подклассы программируемых логических матриц ПЛМ (Programmable Logic Arrays) и программируемой матричной логики ПМЛ (PAL, Programmable Arrays Logic).

Оба эти подкласса микросхем реализуют дизъюнктивные нормальные формы (ДНФ) переключательных функций, а их основными блоками являются две матрицы: матрица элементов И и матрица элементов ИЛИ, включённые последовательно. Технически они могут быть выполнены и как последовательность двух матриц элементов ИЛИ-НЕ.

|

|

|

Матрицы ИЛИ для ПЛМ и ПМЛ различны. В ПЛМ матрица программируется, а в ПМЛ она фиксирована.

Программируемая матрица ИЛИ микросхем ПЛМ составлена из ИЛИ, имеющих по q входов. На входы каждого ИЛИ при программировании можно подать любую комбинацию имеющихся термов, причём термы можно использовать многократно.

ПЛМ позволяет реализовать систему из n переключаемых функций, зависящих не более чем от m переменных и содержащих не более чем q термов. Поэтому функциональные возможности ПЛМ характеризуются тремя цифрами: n, q, m.

В ПМЛ выработанные матрицей И термы поступают на фиксированную (непрограммируемую) матрицу элементов ИЛИ. Это означает жёсткое заранее заданное распределение имеющихся термов между отдельными ИЛИ. Каждому ИЛИ придаются собственные термы, и если для разных ИЛИ окажутся нужными одинаковые термы, придётся их вырабатывать в матрице И несколько раз. Однако при этом программируемость матрицы ИЛИ исключается.

ПЛМ обладают большей функциональной гибкостью, все воспроизведённые ими функции могут быть комбинациями любого числа термов, формируемых матрицей И. Это полезно при реализации систем переключательных функций, имеющих большие взаимные пересечения по термам (например, задачи формирования сигналов управления машинными циклами процессоров). ПМЛ распространены больше, чем ПЛМ, и к их числу относится большинство SPLD.

В сложных программируемых логических схемах CPLD (Complex Programmable Logic Devices) несколько блоков, подобных ПМЛ, объединяются средствами программируемой коммутационной матрицы. В CPLD могут входить сотни блоков и тысячи эквивалентных вентилей. Воздействуя на программируемые соединения коммутационной матрицы и ПМЛ, входящих в состав CPLD, можно реализовать требуемую схему.

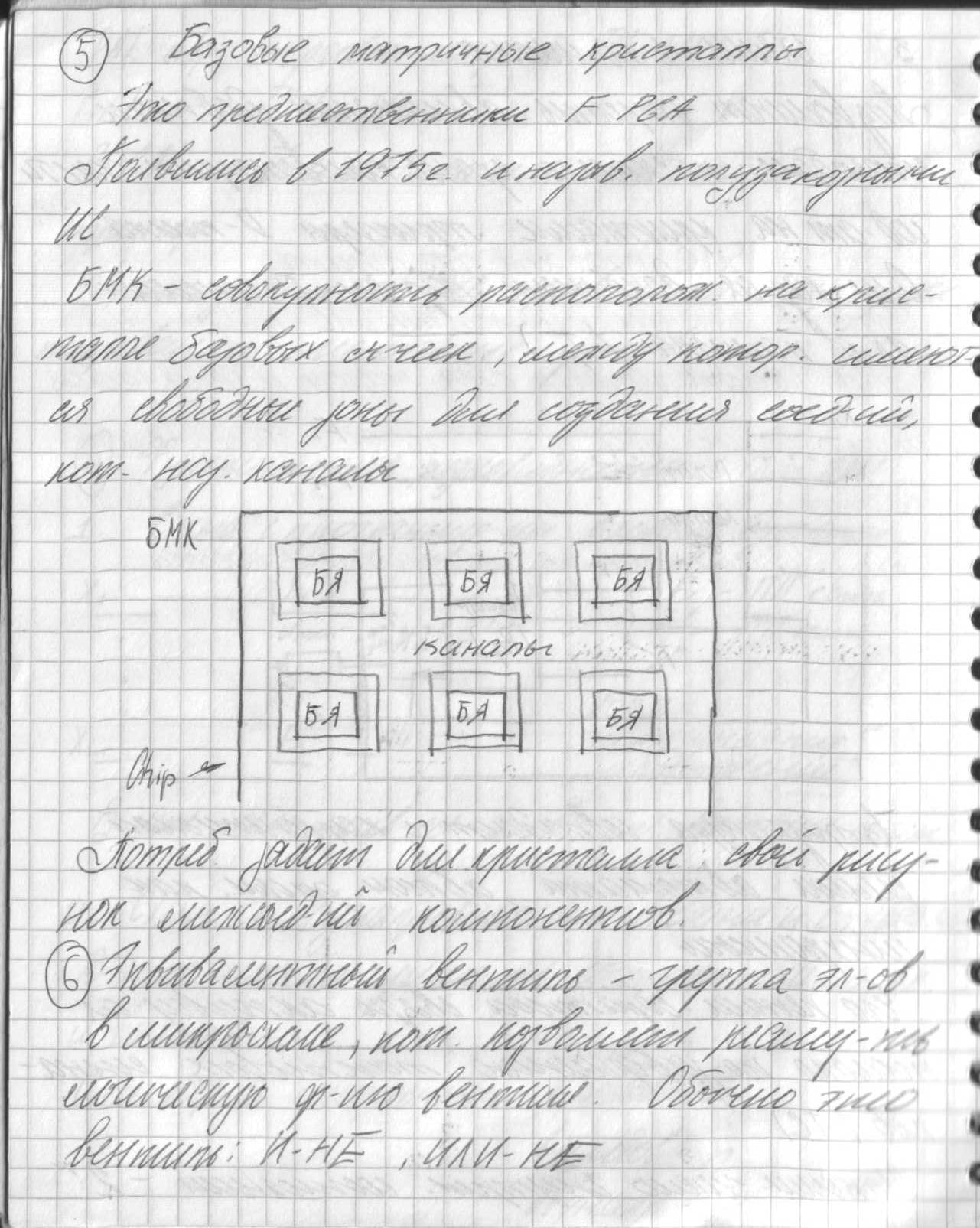

5.БАЗОВЫЕ МАТРИЧНЫЕ КРИСТАЛЫ. ИХ ХАРАКТЕРИСТИКИ. ПОЛУЗАКАЗНЫЕ И ЗАКАЗНЫЕ ИС

БМК –БИС, кот. представляют собой совокупность расположенных на кристалле базовых ячеек, между которыми имеются свободные зоны для создания соединений, которые называются каналы.(1975г)

1985-FPGA – PGA+ОЗУ памятью конфигурации

БМК-заготовки, которые преобразуют в конкретную схему путем выполнения межсоединений.

Базовая ячейка- набор некоторого количества схемных элементов, регулярно повторяющихся на площади кристалла. БЯ могут состоять из нескоммутированнных элементов или из частично оккомутированных.

Причем БЯ состоит из: матрица БЯ1, ОЗУ, ПЗУ и матрицы БЯ2.

Классификация БМК:

По архитектуре:

-канальные( для биполярных ТТП)

-бескональные(для КМОП)

-блочные

ПО виду:

-цифровые

-аналоговые

-цифро-аналоговые

По технологии:

КМОП, ТТЛШ, ЭСЛ, AsGA

Параметры БМК:

Разделяются на 4 группы:

-функциональные – число эквивалентных вентилей тип БЯ, число МБЯ, ПБЯ состав библиотеки функциональных ячеек.

-электрические – уровни напряжения логического 0 и 1, напряжения питания,задержки

-конструкторско-технологические – тип корпуса, число выводов, число уровней металлизации

-эксплуатационные – устойчивость к воздействию внешних факторов,надежность, вероятность сбоев

Полузаказные интегральные схемы на основе базовых матричных кристаллов (БМК) для разработчиков и производителей сложной электронной аппаратуры являются незаменимыми:

-когда требуется быстро разработать и начать производство изделия;

-когда объем производства изделия относительно невысок, а подходящих БИС среди выпускаемых нет;

-при создании специфичной аппаратуры с оригинальной схемотехникой;

-при переработке ранее созданной аппаратуры на новую элементную базу;

-при желании заказчика самостоятельно разработать БИС.

Под заказной понимается микросхема, проектирование и производство которой происходит по индивидуальному полному технологическому циклу, направленному на создание именно этой БИС. К заказным относятся микропроцессоры, микроконтроллеры, периферийные и масса других БИС, поставляемых как стандартные изделия.

Дата добавления: 2020-04-08; просмотров: 436; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!