ФУНКЦИОНАЛЬНЫЕ БЛОКИ ПЛИС ТИПА CPLD

CPLD (Complex Programmable Logic Device) – сложные программируемые логические устройства. CPLD – это БИС, основными частями которой являются:

- PAL (Programmable Array Logic) подобные функциональные блоки (ФБ),

- система коммутации, позволяющая объединять функциональные блоки в единое устройство, выполненная в виде матрицы соединений,

- блоки ввода-вывода (БВВ).

CPLD за счёт PAL-подобной структуры и наличия многовходовых макроячеек (до 56 входов на макроячейку) идеально подходят для реализации сложных счётчиков, высокоскоростных дешифраторов адресных шин большой разрядности, коммутации-мультиплексирования потоков данных и построения разнообразных конечных автоматов. Они применяются в качестве периферии к стандартным микроконтроллерам и микропроцессорам со следующими выполняемыми функциями: дешифрация адреса, поступающего от процессора, выборка соответствующего порта ввода-вывода, преобразование формата данных, формирование прерываний и т.д

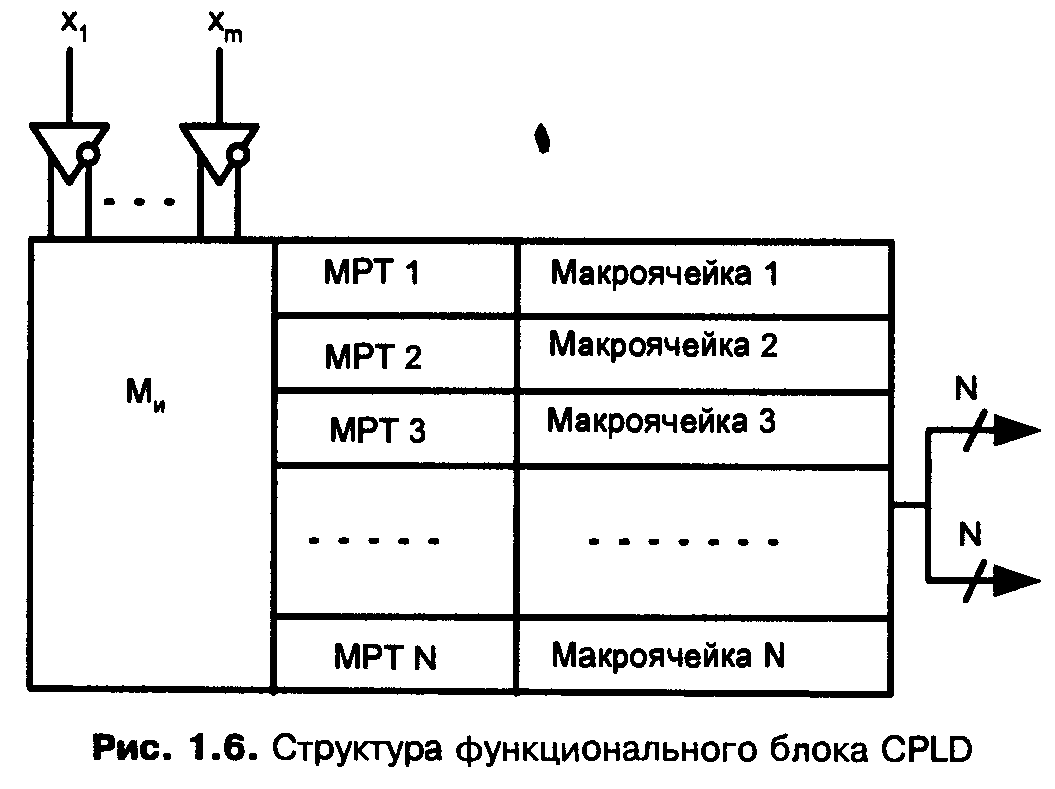

Обобщенная структура функционального блока CPLD:

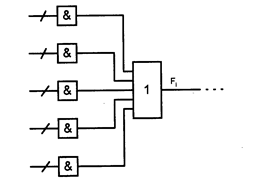

Основными частями функциональных блоков CPLD являются программи руемая матрица элементов И (Ми), матрица распределения термов МРТ и группа из нескольких ( N ) макроячеек. По существу, каждый ФБ представляет собою PAL-подобную структуру с некоторыми отличиями от вариантов, используемых в простых PLD (ПМЛ). Как и в классических PLD, в блоке имеется многовходовая (Wide) матрица Ми,. В классических PLD типа ПМЛ термы жестко распределяются между ИЛИ, формирующими выходные функции в форме ДНФ. Совокупность ИЛИ образует фиксированную (не программируемую) матрицу элементов ИЛИ. На рисункепоказан один из ИЛИ (для канала с номером i), вырабатывающий функцию, в которую может входить не более 5 термов.

|

|

|

В CPLD матрица элементов ИЛИ чаще всего не является полностью фиксированной, и благодаря введению в схему матрицы распределения термов МРТ, возможно варьирование числа термов в вырабатываемой функции F . При этом термы заимствуются у других каналов выработки функций или отдаются им.

14. ПРОГРАММИРУЕМАЯ МАТРИЦА СОЕДИНЕНИЙ ПЛИС ТИПА CPLD

CPLD (Complex Programmable Logic Device) – сложные программируемые логические устройства. CPLD – это БИС, основными частями которой являются:

- PAL (Programmable Array Logic) подобные функциональные блоки (ФБ),

- система коммутации, позволяющая объединять функциональные блоки в единое устройство, выполненная в виде матрицы соединений,

- блоки ввода-вывода (БВВ).

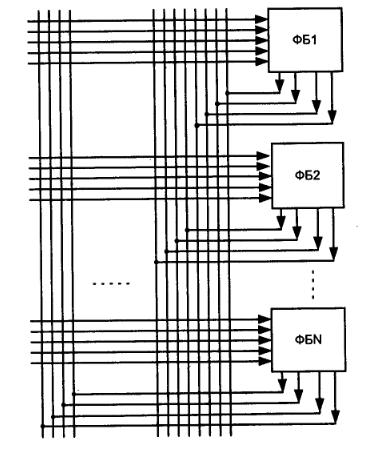

В программируемой матрице соединений ПМС выходы функциональных блоков ФБ подключаются к вертикальным непрерывным линиям, причем каждому выходу соответствует своя линия. Входы ФБ связаны с горизонтальными линиями, пересекающими все вертикальные линии. На пересечениях горизонтальных и вертикальных линий имеются программируемые точки связи, так что любой вход ФБ может быть подключен к любому выходу, чем обеспечивается так называемая полная коммутируемость блоков.

|

|

|

Достоинством ПМС рассмотренного типа является малая и предсказуемая задержка коммутируемых сигналов.Программируемые матрицы соединений эффективны в схемах с относительно небольшим числом коммутируемых блоков. При большом их числе, характерном, например, для FPGA, подобные ПМС были бы чрезмерно сложны.

15. МАТРИЦА РАСПРЕДЕЛЕНИЯ ТЕРМОВ ПЛИС ТИПА CPLD

CPLD (Complex Programmable Logic Device) – сложные программируемые логические устройства. CPLD – это БИС, основными частями которой являются:

- PAL (Programmable Array Logic) подобные функциональные блоки (ФБ),

- система коммутации, позволяющая объединять функциональные блоки в единое устройство, выполненная в виде матрицы соединений,

- блоки ввода-вывода (БВВ).

Терм в формальной логике — интуитивно определённое выражение формального языка (системы).

Благодаря введению в схему матрицы распределения термов (МРТ) возможно варьирование числа термов в вырабатываемой функции F. При этом термы заимствуются у других каналов выработки функций или отдаются им. Проще всего организовать коммутацию термов между соседними каналами. Через соседние каналы путём образования цепочечных связей можно собирать в одном канале много термов (в пределах одного функционального блока).

|

|

|

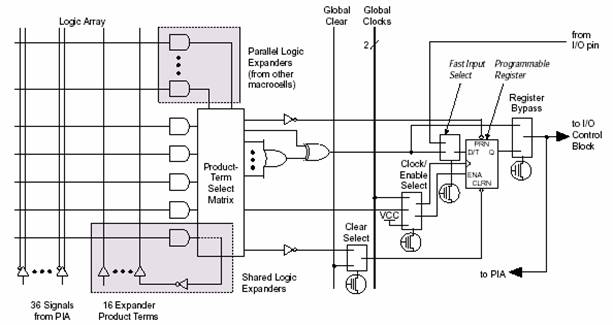

Схемотехнически в операциях распределения термов по каналам ФБ задействованыкак непосредственно цепи коммутации между входами и выходами МРТ, так и логические расширители последовательного и параллельного типов. Последовательные логические расширители создаются подачей инвертированного значения терма из МРТ данного канала обратно на один из вх1одов матрицы M (рисунок 1). Переданный в матрицу М терм становится доступным для использования во всех каналах данного ФБ. Параллельный расширитель позволяет передавать термы одного канала другому. Способность принимать в свой канал термы от соседнего канала обычно означает и возможность приёма через него термов и более далёких каналов с образованием цепочки для сбора термов от нескольких каналов (например, в пределах целого функционального блока). Можно и отдавать собственные термы или их часть другим каналам (в частности, соседним, а через них и более далёким).

Схемотехнически в операциях распределения термов по каналам ФБ задействованыкак непосредственно цепи коммутации между входами и выходами МРТ, так и логические расширители последовательного и параллельного типов. Последовательные логические расширители создаются подачей инвертированного значения терма из МРТ данного канала обратно на один из вх1одов матрицы M (рисунок 1). Переданный в матрицу М терм становится доступным для использования во всех каналах данного ФБ. Параллельный расширитель позволяет передавать термы одного канала другому. Способность принимать в свой канал термы от соседнего канала обычно означает и возможность приёма через него термов и более далёких каналов с образованием цепочки для сбора термов от нескольких каналов (например, в пределах целого функционального блока). Можно и отдавать собственные термы или их часть другим каналам (в частности, соседним, а через них и более далёким).

|

|

|

Термы от МРТ поступают далее на часть ФБ, называемую макроячейкой (МЯ). Она содержит в качестве основы программируемые триггеры и формирует группы выходных сигналов ФБ в нескольких их вариантах.

Матрица распределения термов формирует функцию OR или XOR из термов, которые поступают из логического массива. Функция может состоять из 5 основных термов, количество которых можно увеличить за счёт использования параллельных расширителей.

МАКРОЯЧЕЙКА ПЛИС ТИПА CPLD

CPLD (Complex Programmable Logic Device) – сложные программируемые логические устройства. CPLD – это БИС, основными частями которой являются:

- PAL (Programmable Array Logic) подобные функциональные блоки (ФБ),

- система коммутации, позволяющая объединять функциональные блоки в единое устройство, выполненная в виде матрицы соединений,

- блоки ввода-вывода (БВВ).

МЯ может быть запрограммирована на сброс или предустановку по включению питания. Регистр МЯ может быть сконфигурирован как D -триггер, Т-триггер, регистр-защелка или не задействован, если МЯ необходима для реализации комбинаторной функции. Каждый из указанных выше триггеров может тактироваться от любого из восьми источников сигнала или его инверсии. К этим источникам тактового сигнала относятся: 2 глобальных тактовых сигнала, выбранные из четырех глобальных сигналов, поступающих напрямую от контактов микросхемы; общий сигнал синхронизации (терм от одного из ФБ кристалла); локальные термы управления (из данного ФБ) - LCT[4:7]; терм синхронизации РТС. В МЯ существует две мультиплексные связи с переключающей матрицей ZIA. Один мультиплексор выбирает либо выход мультиплексора VFM, либо выход регистра. Другой мультиплексор выбирает либо выход регистра, либо сигнал с контакта микросхемы. Когда контакт ввода-вывода исполь зуется как выход, выходной буфер задействован, линия обратной связи МЯ может быть использована для реализации обратной связи внутри МЯ. Когда контакт ввода-вывода используется как вход, выходной буфер переведен в третье состояние и соединение контакта ввода-вывода с переключающей матрицей осуществляется через линию обратной связи ячейки ввода-вывода. Если контакт микросхемы используется как регистровый вход, то соединение контакта и входа регистра осуществляется по линии прямой связи, что обеспечивает минимальное время установки сигнала. Если регистр МЯ сконфигурирован как регистр-защёлка, вход разрешения тактирования регистра МЯ не функционирует.

Дата добавления: 2020-04-08; просмотров: 551; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!