Режим 2 внешнего тактирования.

Когда активирован режим внешнего тактирования, счетчик таймера будет обновляться в моменты детектирования активных перепадов сигнала, поступающего на вход ETR таймера. Для некоторых таймеров определенных семейств STM32 вход ETR не может быть выведен наружу из корпуса микроконтроллера.

Для некоторых ETR вход не отображается на выводы IO микроконтроллера как альтернативная функция. В некоторых других таймерах вход ETR таймера мультиплексируется со входом канала 1 таймера.

Главное достоинство использования режима 2 внешнего тактирования (external clock-source mode 2) в сравнении с режимом 1 в том, что предоставленный внешний сигал может быть равным или даже больше, чем внутренняя частота тактирования ядра таймера (такая как частота шины APB). Это не означает, что счетчик таймера может быть обновлен с частотой выше, чем частота ядра таймера (например, частота инкремента, если таймер сконфигурирован для счета вверх).

Только у входа ETR таймера каскад пред делителя находится перед каскадом ресинхронизации. Этот каскад пред делителя полностью асинхронен, и может поделить асинхронную входную частоту на коэффициент до 8 раз.

Сигнал на выходе каскада пред делителя с именем ETRP передается в каскад ресинхронизации перед подачей его в счетчик таймера. Выход схемы ресинхронизации называется сигналом ETRF. Сигнал ETRP имеет то же самое ограничение, которое накладывается на любые асинхронные сигналы, подаваемые на таймер, т. е. его частота должна быть в 3 раза меньше, чем внутренняя частота тактирования ядра таймера.

|

|

|

Режим 2 внешнего тактирования представляет большой интерес во многих случаях практического применения. Например, нужно подсчитывать количество импульсов, приходящих от определенного датчика, но частота на выходе этого датчика больше, чем частота тактирования ядра таймера. В этом случае пред делитель должен быть сконфигурирован таким образом, чтобы снизить частоту входного сигнала с определенным коэффициентом, чтобы частота стала совместима с ограничением каскада ресинхронизации, накладываемым на его входную частоту сигнала. При интерпретации подсчитанного количества импульсов нужно учитывать коэффициент деления, который был внесен пред делителем.

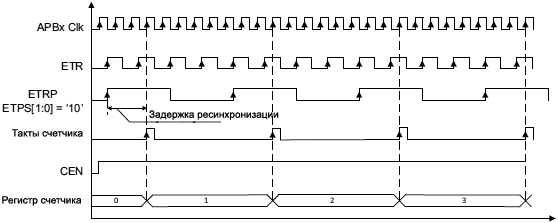

Рис. 14 показывает пример, где таймер сконфигурирован в режиме 2 внешнего тактирования, и где сигнал тактов поступает на таймер через вход ETR. В этом примере сигнал внешних тактов выше, чем внутренняя частота тактирования ядра таймера (частота шины APB). Асинхронный пред делитель ETR был сконфигурирован для деления входного сигнала на 4 путем установки битового поля ETPS = 10 в регистре TIMx_SMCR.

|

|

|

Рис. 14. Инкремент счетчика таймера (external clock mode 2).

Также рис. 14 показывает задержку между выходом пред делителя (сигналом ETRP) и сигналом тактов таймера CK_CNT, используемым для обновления счетчика таймера. Эта задержка вставляется перед каскадом ресинхронизации.

Ниже показана типовая и рекомендуемая последовательность для конфигурирования таймера в external clock-source mode 2:

1. Вычислить максимальную частоту входного сигнала тактов, и выбрать коэффициент деления асинхронного пред делителя. Если частота внешнего сигнала в 3 раза меньше, чем внутренняя частота ядра таймера, то использование пред делителя необязательно, и он может не использоваться. В случае, когда асинхронный пре делитель не используется, битовое поле ETPS должно быть сброшено (это состояние по умолчанию после сброса).

2. Если необходимо, активировать каскад фильтрации, чтобы вырезать импульсы тактов, длительность которых меньше определенного порога. Для дополнительной информации о том, как настроить функцию фильтрации, см. секцию "Каскад фильтрации" выше в этой статье.

3. Сконфигурировать активный перепад внешнего тактового сигнала. Бит ETP устанавливает, на какой перепад будет реагировать счетчик в external clock-source mode 2. По умолчанию после сброса ETP = 0, что определяет активный фронт нарастания уровня внешнего сигнала тактов (т. е. перепад лог. 0 -> лог. 1 внешних тактов приведет к срабатыванию обновления счетчика таймера).

|

|

|

4. Разрешить external clock-source mode 2 установкой бита разрешения внешнего тактирования ECE =1.

5. В завершение нужно обязательно установить бит разрешения счетчика в регистре TIMx_CR1.

Примечание: вход ETR может использоваться также как вход для внешнего тактового сигнала, когда сконфигурирован external clock-source mode 1. Можно одновременно активировать external clock-source mode 1 и external clock-source mode 2, и одновременно использовать их для входа ETR. В этом случае приоритет отдается external clock-source mode 2, и он будет использоваться для подачи тактов на счетчик таймера.

Дата добавления: 2020-01-07; просмотров: 374; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!