Отличия режима 1 и режима 2 внешнего тактирования.

На первый взгляд кажется, что функционал режимов 1 и 2 внешнего тактирование одинаковый, однако тщательное изучение их различий позволяет выделить из специфической характеристики, которые делают каждый режим больше подходящим для специальных случаев применения.

Ниже показаны основные отличия между режимами 1 и 2:

• Можно использовать external source clock mode 1 для обновления счетчика таймера по обоим перепадам внешнего сигнала. Для external clocksource mode 2 это невозможно.

• При использовании external clock-source mode 2, можно подавать такты на таймер от внешнего источника. При этом все еще можно одновременно конфигурировать таймер в одном из совместимых slave-режимов. Например, если требуется считать количество импульсов, генерируемых определенным датчиком в заданный период времени, с повторениями:

– один из таймеров, наподобие TIMy, настраивается на подсчет импульсов в external clock-source mode 2, генерируемых датчиком.

– второй таймер, наподобие TIMz, настраивается на генерацию выходного сигнала триггера (trigger-out signal, TRGO), повторяя его через заданный период времени.

– первый таймер (TIMy) также должен быть сконфигурирован в slave reset mode, и использовать сигнал TRGO второго таймера (TIMz) в качестве триггера для сброса.

Есть только один способ настроить таймер на генерацию выходного импульса TRGO в регулярные интервалы времени - установить регистр таймера TIMx_ARR в определенное значение, чтобы генерировалось периодическое событие обновления (update event).

Событие "update event" может выдать импульс на сигнал таймера TRGO, если установлен master-mode таймера на "update value" (например, в регистре TIMx_CR2 поле бит MMS[2:0] установлено в значение 010).

Таймер может быть сконфигурирован в slave-режиме сброса путем установки правильного значения в поле бит управления подчиненным режимом (slave mode selection, SMS) в регистре TIMx_SMCR (например SMS[2:0] = 100).

Выбор правильного триггера для slave-режима сброса обеспечивается правильным значением управляющего битового поля выбора триггера TS[2:0]. Значение для записи в TS[2:0] зависит от того, какой вход ITR первого таймера (TIMy) соединен внутри кристалла с выходом TRGO второго таймера (TIMz). Руководство пользователя по каждому микроконтроллеру STM32 перечисляет все внутренние соединения между периферийными устройствами таймера.

ШИМ-регулирование с использованием входа break

ШИМ (Широтно-Импульсная Модуляция (PWM — Pulse Width Modulation))

— импульсный сигнал постоянной частоты и переменной скважности (отношение длительности импульса к периоду его следования). С помощью задания скважности можно менять среднее напряжение на выходе ШИМ.

Т.е. хоть мы и работаем с цифровым устройством, которое понимает только 1 и 0 (высокий уровень напряжения +3..+5V (HIGH) и низкий уровень напряжения 0..+2V (LOW)), но мы всё же можем получить напряжение отличное от данных изменяя скважность импульсов. Другими словами – получаем аналоговый сигнал цифровыми методами.

Ниже представлен вид сигнала на выходе при разных параметрах функции analogWrite().

Функция Break доступна в продвинутых таймерах, таких как TIM1 и TIM8, а также в облегченных таймерах наподобие TIM15, TIM16 и TIM17. Функция Break используется в основном для защиты выходного каскада силового инвертора, который управляется от выходов таймера; функция запрещает эти выходы, или переводит их в заранее определенное безопасное для драйвера состояние, когда что-то пошло не так в силовом блоке или с самим микроконтроллером.

Для детектирования внешних запросов остановки (на входе break), сгенерированных силовым каскадом, функция break связана с выделенным входом (например, BKIN или BKIN2), который отображен как альтернативная функция на одну из нескольких ножек IO микроконтроллера. Будучи разрешенной, функция break запрещает выходы PWM, или переводит их в безопасное состояние, когда было детектировано событие break, даже если не присутствует тактирование. Например, можно асинхронно деактивировать выходы управления силовым мостом.

Руководство пользователя содержит больше информации о том, как конфигурировать безопасное предопределенное состояние для выходов таймера.

Как только определено достоверное событие break, асинхронно очистится управляющий бит MOE в регистре TIMx_BDTR. Он действует только на тех каналах таймера, которые сконфигурированы в режим вывода. Чтобы возобновить нормальное рабочее состояние выходов канала таймера, программа должна установить бит MOE, или установить бит AOE, чтобы выходы таймера перешли в рабочее состояние и начался новый цикл ШИМ.

Некоторые семейства микроконтроллеров STM32 (например, семейство STM32F303) имеют встроенные таймеры, у которых есть два входа break: BKIN и BKIN2. Для таких таймеров вход BRK2 имеет меньший приоритет, чем вход BRK. Входы BKIN и BKIN2 могут запретить выходы канала таймера только принудительным переводом их в состояние отключено (Hi-Z), и они не могут перевести их в предопределенное безопасное состояние.

Сравнение входов Break с использованием OCxRef-clear. Как было упомянуто выше, основное использование входа break - управлять выходами канала таймера так, чтобы предотвращать аварийные ситуации. Благодаря гибкому дизайну вход break также может использоваться в других случаях, наподобие регулирования тока в каждом такте. Концептуально регулирование тока в каждом периоде ШИМ выполняется функцией OCxRef-clear таймеров STM32.

В некоторых случаях невозможно использовать функцию OCxRef-clear для управления регулированием тока в каждом цикле ШИМ. Это вследствие того, что вход таймера ETR, используемый этой функцией, может быть конкурентным с другой функцией таймера (например, внешняя синхронизация таймера использует вход ETR для подачи внешнего сигнала тактов). В такой ситуации может быть полезным использовать функцию Break для поддержки регулирования тока в каждом периоде ШИМ.

С одной стороны, функция OCxRef clear действует на выходах канала таймера (что также относится к функции Break); с другой стороны, функция OCxRef может быть активирована на каждом канале по отдельности (например, активация функции OCxRef clear осуществляется поканально через установку соответствующего управляющего бита OCxCE для регулируемых каналов). В этой второй ситуации функция Break действует на всех выходах каналов (например, нет способа управлять, на какой канал влияет событие break).

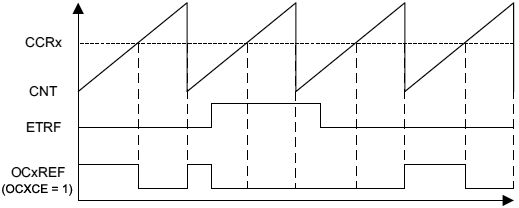

Концепция поциклового регулирования тока основана на факте, что как только регулируемая величина тока станет больше заданного порога, сигнал PWM (ШИМ) станет низким до начала следующего цикла PWM. Это поведение изначально поддерживается функцией OCxREf-clear, что иллюстрируется на рис. 15.

Рис.15 Тайминг очистки OCxREF таймера TIMx.

Для функции Break аналогичное поведение управляется битом AOE. Если бит AOE удерживается в своем состоянии по умолчанию (состоянии после сброса), то как только регулируемый ток пересечет заданный порог, выходы таймера перейдут на низкий уровень. Таймер продолжит находиться в этом состоянии, пока бит MOE не будет установлен программно, что отличается от типичного поведения логики поциклового регулирования.

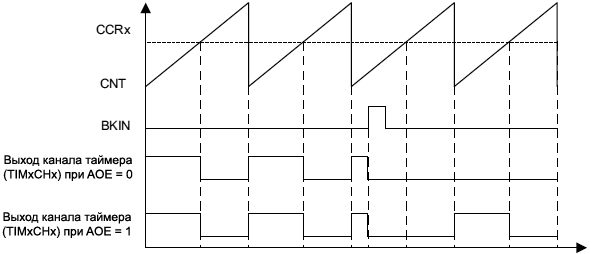

Установка бита управления AOE перед активацией функции регулирования с помощью Break автоматически установит управляющий бит MOE на начале каждого нового цикла PWM. Ранее описанное поведение функции Break по сравнению с конфигурацией бита управления AOE иллюстрировано на рис. 16, где построена форма сигнала на одном выходе канала таймера.

Рис. 16. Тайминг функции Break.

Также рис. 16 показывает разницу в поведении выхода таймера между этими двумя конфигурациями бита управления AOE.

• Если AOE = 0, то выход PWM будет запрещен даже если вход break больше не активен (аналогично срабатыванию защиты, которую нужно сбросить принудительно).

• Если AOE = 1, то выход PWM разрешается на следующем событии обновления, если вход break не активен (соответствует поцикловому ШИМ-регулированию тока, т. е. ограничению тока с помощью уменьшения скважности периода ШИМ).

Дата добавления: 2020-01-07; просмотров: 337; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!