Тактирование таймера STM32 от внешнего источника .

Таймер STM32 может тактироваться от внешнего источника тактирования, но это не означает, что не нужно тактировать шину APB (advanced peripheral bus). Таймер STM32, синхронизирован внешним тактовым сигналом со своей собственной частотой ядра (которая является тактами APB). Результирующий синхронизированный сигнал тактов поступает на пред делитель таймера, который после пред делитель идет на счетчик.

Таймер STM32 требует 2 источника сигнала, чтобы постоянно обновлялась временная база (см. рис. 10). Период внешнего сигнала тактов — это единица времени, используемая для обновления базы времени таймера.

Рис. 10. Синхронизация таймера внешним тактовым сигналом.

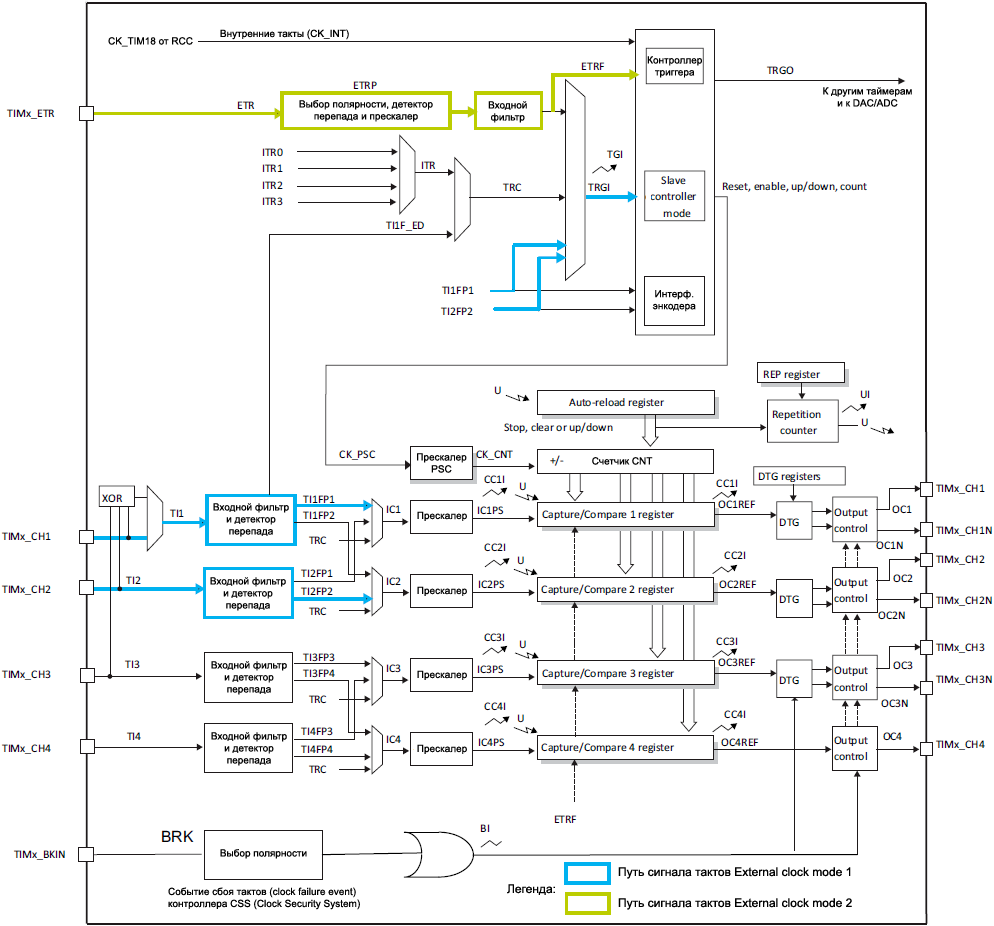

Есть два способа синхронизации (или внешнего тактирования) таймера STM32:

• Режим 1 внешнего тактирования: внешний тактовый сигнал поступает на один из входов канала таймера TIx.

• Режим 2 внешнего тактирования: внешний тактовый сигнал поступает на вход ETR (если это реализовано в таймере и доступно).

Рис. 11 показывает прохождение тактового сигнала для обоих этих режимов.

Рис. 11. Распространение тактов для режимов внешнего тактирования.

Блок синхронизации.

Перед введением в режимы синхронизации таймера внешним сигналом важно сначала показать механизм синхронизации, реализованный в таймере STM32, когда аппаратура STM32 работает с внешними сигналами. Внешние сигналы — это такие сигналы, когда сигнал поступает извне таймера. Этот сигнал может быть, как синхронизирован с тактовым сигналом, так и может быть полностью асинхронным.

|

|

|

Таймер должен обрабатывать внешние сигналы, которые могут быть полностью асинхронными, и соответствующим образом подстраивать выходное состояние формируемых сигналов. Таймер также должен быть способен информировать программное обеспечение о метках времени, на которых сигнал определенного таймера меняет свое состояние (например, переключение сигнала).

Чтобы обработать полностью асинхронный сигнал, периферийное устройство таймера сначала нуждается в том, чтобы пересинхронизировать свой собственный сигнал тактов. Его может понадобиться пересинхронизировать, например, с тактовым сигналом логики ядра перед тем, как передать результирующий синхронизированный сигнал в разные блоки таймера. Это действие защитит логику ядра таймера от проблем мета стабильности.

Рис. 12 показывает синоптическую диаграмму для схемы синхронизации, используемой для синхронизации внешних сигналов, поступающих на входы таймера. Схема синхронизации составлена главным образом из двух соединенных каскадом D-триггеров, которые тактируются сигналом ядра таймера. Внешний сигнал приходит на вход первого каскада D-триггера, и синхронизированный сигнал получается на выходе второго каскада D-триггера. Этот блок синхронизации вводит задержку как минимум 2 такта ядра таймера и максимум 3 такта.

|

|

|

Рис. 12. Блок синхронизации.

В таймере реализована “первоначальная синхронизация” на всех входах, кроме ETR, где первым идет пред делитель, после него сигнал синхронизируется.

Как показано формулой ниже, частота входного сигнала должна быть в 3 раза меньше, чем частота тактирования ядра.

FreqTIMCLK ≥ 3 x Freqinputsignal

Дата добавления: 2020-01-07; просмотров: 241; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!