Прерывистый режим опроса каналов

Ещё одна возможность, предоставляемая модулями ADC, — прерывистый режим (discontinuous mode). Для обычной и инжектированной групп этот режим задаётся отдельно битами DISCEN и JDISCEN соответственно (в библиотеке StdPeriph для этого есть функции ADC_DiscModeCmd и ADC_InjectedDiscModeCmd). Прерывистый режим позволяет разделить каждую группу каналов на подгруппы и по событиям триггера по очереди выполнять оцифровку этих подгрупп. Размер подгруппы для обычной группы задаётся битами DISCNUM[2:0] регистра ADC_CR1 (в библиотеке StdPeriph — функцией ADC_DiscModeChannelCountConfig), для группы инжектированных каналов размер подгруппы равен 1 (то есть просто все каналы перебираются по очереди). Чтобы было понятнее как это устроено — приведу примеры из официальной доки:

· 1. Оцифровка обычных каналов. Пусть у нас в регистрах ADC_SQRx прописаны каналы 0, 1, 2, 3, 6, 7, 9, 10, длина списка обычных каналов установлена равной 8, выбран прерывистый режим (discontinuous mode), а размер подгуппыподгруппы установлен равным 3. В этом случае каждое срабатывание триггера группы обычных каналов будет запускать оцифровку очередной подгруппы:

o 1 срабатывание триггера: оцифровываются каналы 0, 1, 2. После оцифровки каждого канала устанавливается бит EOC.

o 2 срабатывание триггера: оцифровываются каналы 3, 6, 7. После оцифровки каждого канала устанавливается бит EOC.

o 3 срабатывание триггера: оцифровываются каналы 9, 10 (в этой подгруппе всего 2 канала, поскольку на этом заканчивается общий список). После оцифровки каждого канала устанавливается бит EOC.

|

|

|

o 4 срабатывание триггера: оцифровка списасписка каналов начинается сначала, снова оцифровываются каналы 0, 1, 2. После оцифровки каждого канала устанавливается бит EOC.

· 2. Оцифровка инжектированных каналов. Пусть у нас в регистре ADC_JSQR прописаны каналы 1, 2, 3, длина списка инжектированных каналов установлена равной 3 и выбран прерывистый режим (discontinuous mode). В этом случае каждое срабатывание триггера для группы инжектированных каналов будет запускать оцифровку очередной подгруппы:

o 1 срабатывание триггера: оцифровывается канал 1.

o 2 срабатывание триггера: оцифровывается канал 2.

o 3 срабатывание триггера: оцифровывается канал 3. После оцифровки канала устанавливаются биты EOC и JEOC.

o 4 срабатывание триггера: оцифровка списасписка каналов начинается сначала, снова оцифровывается канал 1.

Режим калибровки

Все модули ADC имеют режим автоматической самокалибровкисамо калибровки, которую рекомендуется проводить каждый раз после включения питания. Делается это очень просто:

· Сначала нужно очистить регистры калибровки, установив в единицу бит RSTCAL регистра ADC_CR2 (в библиотеке StdPeriph для этого есть функция ADC_ResetCalibration). После окончаниия процедуры сброса бит RSTCAL аппаратно сбросится в ноль.

|

|

|

· Далее нужно запустить самокалибровкусамо калибровку, установив в единицу бит CAL в регистре ADC_CR2 (в библиотеке StdPeriph для этого есть функция ADC_StartCalibration). После окончаниияокончания процедуры калибровки бит CAL аппаратно сбросится в ноль.

Процедуру калибровки нельзя запускать ранее чем через два такта после включения модуля ADC. После окончания калибровки в регистре ADC_DR сохраняется калибровочный код (калибровочное значение).

Предельный компаратор

В каждом модуле ADC есть такая штука как предельный компаратор (analog watchdog). Он может отслеживать, не выходит ли результат оцифровки за установленные границы. Если результат получился больше верхней границы или меньше нижней границы, то компаратор автоматически устанавливает бит AWD в регистре ADC_SR. Границы компаратора задаются в специальных регистрах — ADC_HTR и ADC_LTR (в библиотеке StdPeriph для этого есть функция ADC_AnalogWatchdogThresholdsConfig). Для компаратора не важно как настроено выравнивание результата оцифровки, он в любом случае использует для сравнения только 12 значащих бит.

Предельный компаратор можно настроить для отслеживания результата преобразования одного или сразу группы каналов. Режим работы определяется битами AWDSGL, AWDEN и JAWDEN (в StdPeriph для этого есть функция ADC_AnalogWatchdogCmd). Ниже приведена таблица различных режимов.

|

|

|

Двойной режим подробно описывать не буду, и так статья получается очень длинной. Лучше как-нибудь потом отдельно про это напишу, тем более там тоже много всяких подрежимов. Скажу только, что в двойном режиме можно различными способами синхронизировать работу сразу двух АЦП для ускорения оцифровки большого количества каналов.

Регистры

ADC_SR — регистр статуса. Младшие 5 бит этого регистра позволяют отслеживать состояние и различные события модуля ADC. Все эти биты устанавливаются аппаратно, а сбрасываются программно, записью в них нуля.

ADC_ CR1 — регистр настройки.

ADC_CR2 — регистр настройки.

ADC_SMPR1, ADC_SMPR2 — регистры настройки времени сэмплирования для каждой линии ввода.

ADC_JOFRx (x=1..4) — регистры смещения для инжектированных каналов. Записанные в эти регистры значения будут вычтены из сырых результатов оцифровки перед записью результатов в регистры данных.

ADC_HTR — регистр верхней установки предельного компаратора.

ADC_LTR — регистр нижней установвки предельного компаратора.

|

|

|

ADC_SQRx — регистры задания списка каналов для обычной группы, а также определения размера этой группы.

ADC_JSQR — регистр задания списка каналов для инжектированной группы, а также определения размера этой группы.

ADC_JDRx — регистры данных каналов инжектированной группы. Младшие 16 бит каждого регистра содержат выровненные к старшему или младшему биту результаты оцифровки. Поскольку для инжектированной группы каналов результаты вычисляются вычитанием смещения из сырых значений, то они могут быть как положительными, так и отрицательными. В связи с этим, для каждого канала этой группы результат занимает 13 бит (старший бит результата отводится под знак).

ADC_DR — регистр данных каналов обычной группы. Младшие 16 бит этого регистра содержат выровненные к старшему или младшему биту результаты оцифровки обычного каналаобычного канала, обработанного последним. Результат беззнаковыйбез знаковый и занимает 12 бит выровненных влево или вправо. Если включен двойной режим, то старшие 16 бит регистра данных ADC1 содержат результат работы ADC2.

Таймер

Таймер – одна из самых полезных вещей в микроконтроллере и основная его задача – отсчитывание точных интервалов времени. На отладочной плате STM32F4 Discovery установлен микроконтроллер STM32F407VG, который имеет следующие таймеры:

· Basic timers (TIM6, TIM7) – самый простой таймер, который умеет только генерировать прерывания в заданный промежуток времени, но при этом очень легко настраивается и управляется.

· General-purpose timers (TIM2-TIM5, TIM9-TIM14) – более продвинутый таймер, позволяющий генерировать ШИМ, считывать состояние ног, обрабатывать данные от энкодера и т.д.

· Advanced-control timers (TIM1, TIM8) – самый продвинутый таймер, может использоваться как трехфазный ШИМ генератор.

· 3 таймера общего назначения (TIM2, TIM3, TIM4).

· 2 WDT (WatchDog Timer)

· 1 SysTick Timer

Таймеры имеют 4 независимых канала, которые могут использоваться для:

§ Захвата сигнала

§ Сравнения

§ Генерации ШИМ

§ Генерации одиночного импульса

Таймеры 16 битные (то есть могут считать до 65535), умеют работать с инкрементальными энкодерами и датчиками Холла, несколько таймеров можно синхронизировать между собой. Есть прерывания на разные события, а именно:

§ Переполнение

§ Захват сигнала

§ Сравнение

§ Событие-триггер

При наступлении любого из этих событий таймеры могут генерировать запрос к DMA (DMA – прямой доступ к памяти. Теперь немного подробнее о каждом из режимов работы таймеров.

Режим захвата сигнала. Очень удобно при работе таймера в этом режиме измерять период следования импульсов. Смотрите сами: приходит импульс, таймер кладет свое текущее значение счетчика в регистр TIM_CCR. По-быстрому забираем это значение и прячем в какую-нибудь переменную. Сидим, ждем следующий импульс. Импульс пришел, таймер снова перносит значение счетчика в TIM_CCR, и нам остается только вычесть из этого значения то, которое мы предварительно сохранили. Это, наверное, самое простое использование этого режима таймера, но очень полезное. Отлавливать можно как передний фронт импульса, так и задний, так что возможности довольно велики.

Режим сравнения. Тут просто подключаем какой-нибудь канал таймера к соответствующему выводу, и как только таймер досчитает до определенного значения (оно в TIM_CCR) состояние вывода изменится в зависимости от настройки режима (либо выставится в единицу, либо в ноль, либо изменится на противоположное).

Режим генерации ШИМ. В этом режиме таймер генерирует ШИМ!

Режим Dead-Time. Суть режима в том, что между сигналами на основном и комплементарном выводах таймера появляется определенная задержка. За таймеры несут ответственность файлы – stm32f10x_tim.h и stm32f10x_tim.c.

Давайте рассмотрим, какие есть таймеры на процессоре. В процессоре 14 таймеров — 12 — 16ти битных и два 32 битных.

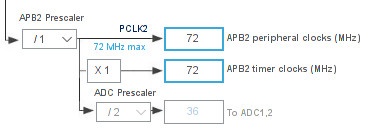

К шине АРВ1 подключены таймеры TIM2, TIM3, TIM4, TIM5, TIM6, TIM7, TIM12

А к шине АРВ2 — TIM1, TIM8, TIM9, TIM10, TIM11.

TIM1

На рис. 4 блок-схемы таймера TIM1 показаны его четыре основных блока:

1. Блок контроллера master/slave.

2. Блок базы времени.

3. Блок каналов таймера.

4. Блок функции Break.

Рис. 4 Блок – схема внутреннего устройства таймера TIM1.

Пример таймера №1

Первый источник тактирования: Clock Source ⇨ Internal Clock — в данном случае источник будет внутренний — частота от шины APB2.

Второй источник тактирования: ETR2. Если указать ETR2, тогда источником будет служить какой-то внешний сигнал. пред делитель не используем — 0, переполнение будет 10. Раздел Trigger Output пока не нужен.

У каждого таймера есть четыре независимых канала, которые могут подключаться к физическим пинам микроконтроллера, то есть работать как внешние входы/выходы, а могут и не подключаться, и работать как внутренние входы/выходы для взаимодействия с другими таймерами. У некоторых МК, например, у F303, есть доп. каналы (5 и 6) не имеющие выхода наружу.

Продвинутые таймеры (TIM1 и TIM8) оснащены механизмом Break (защитное отключение выходных каналов таймера), который приводится в действие по сигналу от внешнего входа (TIMx_BKIN) или в случае обнаружения сбоев в системе тактирования микроконтроллера. С помощью этого механизма можно мгновенно перевести каналы в заранее определённое состояние. При этом сам по себе таймер продолжает работать.

У канала, настроенного на выход и выдающего сигнал Output Compare или PWM Generation, есть опорный сигнал, который называется OC1REF (цифра определяет номер канала). На схеме это выглядит так

Сигнал OC1REF проходя жёлтый квадратик (это генератор dead time) расщепляется на два сигнала — прямой и инвертированный, а потом эти сигналы проходя через механизм включения/отключения каналов (голубенький квадратик) попадают на пины микроконтроллера.

Так вот, если включить ETR as Clearing Source, и на пин TIM1_ETR (PA12) подать кратковременный сигнал HIGH, то OC1REF тут же переключится в LOW, и будет оставаться таким до тех пор пока таймер не переполнится, то есть пока не произойдёт событие обновления. Если не убирать сигнал ETR, то OC1REF будет оставаться в LOW.

Дата добавления: 2020-01-07; просмотров: 234; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!