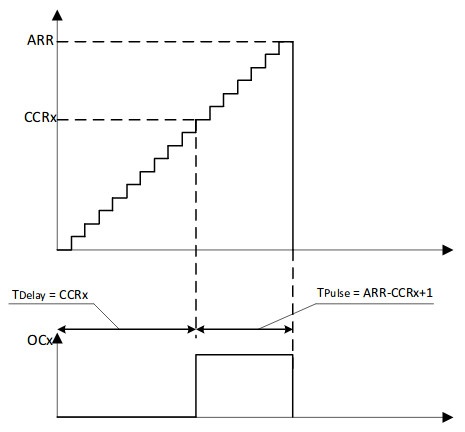

Подача единичного импульса на примере ШИМ

ARR — регистр переполнения.

CCRx — регистр захвата/сравнения (х — номер канала).

OCx — выходной импульс.

Блок контроллера master/slave.

Блок master/slave предоставляет блок базового времени, отсчитывающий импульсы тактов (например CK_PSC), а также сигнал управления направлением счета. Этот блок в основном предоставляет управляющие сигналы для блока базового времени.

Контроллер master/slave применяет правильную конфигурацию счета для блока базового времени, основываясь на конфигурации master/slave; он также оценивает реальный статус счета.

Например, если таймер сконфигурирован в одном из режимов энкодера путем записи в управляющее битовое поле SMS регистра TIMx_SMCR, то сигнал подсчитываемых импульсов и сигнал управления направлением счета будет вычисляться на основе состояния входных сигналов фаз энкодера TI1FP1 и TI2FP2.

Контроллер master/slave обрабатывает синхронизацию между таймерами. Этот блок может быть сконфигурирован для вывода сигнала синхронизации (сигнал TRGO) рядом с определенным внутренним событием таймера. Он может быть сконфигурирован также для управления счетчиком базового времени в функции внешних событий (наподобие внутренних событий других таймеров или внешних сигналов).

Можно сконфигурировать один slave-таймер для инкремента своего счетчика, базируясь на событиях master-таймера, таких как его обновление. В этом примере событие master-таймера сигнализирует блок контроллера master/slave. Этот управляющий блок использует сигнал выхода master-таймера TRGO. Сигнал выхода master-таймера TRGO подключается как входной сигнал slave-таймера TRGI. Блок контроллера master/slave slave-таймера конфигурируется для использования входного сигнала TRGI в качестве источника тактов для инкремента счетчика таймера slave-таймера.

|

|

|

Не у всех таймеров STM32 есть функция контроллера master/slave. В таймере TIM1, который дан для примера, встроен полный функционал master/slave; в сравнении с ним базовые таймеры TIM6 и TIM7 имеют самый простой контроллер master/slave. У контроллера master/slave таймеров TIM6 и TIM7 нет управляющего поля бит.

Для таймеров TIM6 и TIM7 счетчик базы времени всегда считает вверх, без сброса содержимого по внешним событиям. Нельзя их тактировать ни от другого источника тактов, ни от внутренних тактов.

Блок базы времени.

Блок базы времени сделан на основе счетчика вместе с каскадом пред делителя и счетчиком повторений. Тактовый сигнал поступает в блок базы времени, проходя через каскад пред делителя перед тем, как достичь счетчика базы времени.

В зависимости от содержимого регистра пред делителя таймера TIMx_PSC, частота считаемых импульсов может быть снижена перед тем, как достичь стадии счетчика. Сигнал на выходе прескалера является тактовым сигналом счета, который поступает на каскад счетчика.

|

|

|

Счетчик таймера управляется двумя регистрами:

• TIMx_CNT, используется для чтения и записи содержимого счетчика таймера.

• TIMx_ARR, содержит значение для автоматической перезагрузки счетчика таймера.

Автоматическая перезагрузка счетчика работает следующим образом. Если счетчик таймера считает вверх, и достиг значения содержимого регистра TIMx_ARR, то счетчик таймера сбрасывается и начинается новый цикл счета. Если счетчик считает вниз, и достиг нуля, то в счетчик загружается значение из регистра TIMx_ARR, и начинается новый цикл счета.

Каждый раз, когда начинается новый цикл счета, срабатывает "событие обновления" таймера, пока счетчик повторений (repetition counter) равен 0. Если счетчик повторений не равен 0, то событие обновление не сработает, но перезапустится новый цикл счета, и содержимое счетчика повторений уменьшится на 1. Когда содержимое счетчика повторений достигнет нуля, произойдет событие обновления, и в счетчик повторений загрузится значение, сохраненное в регистре TIMx_RCR.

Не у всех таймеров STM32 есть счетчик повторений. Если его нет, то таймер ведет себя так, как если бы счетчик повторений был всегда равен 0.

|

|

|

Блок канала таймера.

Каналы таймера — это рабочие элементы таймера, с помощью них таймер взаимодействует с внешним аппаратным окружением. В целом каналы таймера отображаются на внешние выводы микроконтроллера STM32, с некоторыми исключениями, такими как каналы 5 и 6 таймера TIM1 семейства микроконтроллеров STM32F30x. Канал таймера, отображенный на вывод микроконтроллера STM32, может использоваться либо как вход, либо как выход.

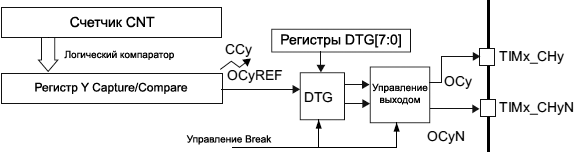

Когда вывод сконфигурирован как выход, канал используется для генерации сигналов. Пока канал сконфигурирован в режиме выхода, содержимое регистра канала TIMx_CCRy сравнивается с содержимым счетчика таймера. На основе этого постоянного логического сравнения и сконфигурированного подрежима выхода (наподобие PWM1 mode или Inactive mode), канал таймера либо устанавливает, либо сбрасывает флаг OCyREF, и его значение поступает на каскад выхода канала. Каскад выхода применяет набор уточняющих операций к сигналу OCyREF, базируясь на наборе сконфигурированных параметров (наподобие полярности канала или генерации интервала dead-time, и других параметров).

Выходной сигнал каскада выхода отображается на выводы микроконтроллера как их альтернативная функция порта. Обратите внимание, что некоторые каскады выхода каналов таймера, как показано на рис. 5, могут быть организованы как два комплементарных сигнала (это используется для управления плечами силового моста).

|

|

|

Рис. 5. Блок-схема канала таймера, когда он сконфигурирован на вывод.

Управляющие битовые поля для такого выходного каскада обеспечивают средства настройки каждого выходного сигнала по отдельности (наподобие разрешения/запрета сигнала на выходе или настройки полярности).

Когда канал сконфигурирован на вход, он может использоваться для запоминания меток времени в моменты переходов уровня внешнего сигнала - либо по его нарастанию уровня, либо по спаду, либо по обоим перепадам. Для поддержки этой функции вход канала отображается на один из выводов микроконтроллера.

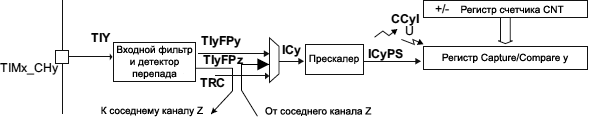

Некоторые входы канала таймера также могут отображаться на некоторые внутренние сигналы чипа, например, на выход генератора - с целью калибровки частоты. На вход канала таймера TIy обрабатывается схемой кондиционирования сигнала, что показано на рис. 6. Схема кондиционирования включает каскад фильтрации и детектор перепада. Каскад фильтра вырезает импульсы, длительность которых меньше сконфигурированной. Детектор перепада определяет, присутствует ли на нужном входе после фильтрации активный перепад уровня.

Рис. 6. Блок-схема канала таймера, когда он сконфигурирован на ввод.

Конфигурация активного перепада устанавливается путем настройки битовых полей полярности в регистре TIMx_CCER. Схема кондиционирования выводит два сигнала:

• TIyFPy: входной сигнал таймера TIy, который был отфильтрован, и у которого был детектирован активный перепад в зависимости от полярности канала таймера “y”.

• TIyFPz: всегда входной сигнала таймера TIy, который был отфильтрован, но на котором был определен активный перепад в зависимости от полярности канала таймера “z”.

Сигнал TIyFPz перенаправляется на вход прескалера канала “z”, где сигнал TIzFPy перенаправляется на вход прескалера канала “y”, как показано на рис. 3 выше. Перекрестное переключение фильтрованных входных сигналов очень полезно для фиксации моментов времени как для нарастания уровня, так и для спада уровня входного сигнала (применяется для реализации приложений оценки ШИМ).

Каждый канал таймера может быть сконфигурирован в один из трех возможных режимов. Каждый входной режим соответствует одному из возможных трех входов мультиплексора прескалера, подключенного к прескалеру канала таймера. Битовое поле CCyS влияет на поведение таймера, если он сконфигурирован в режиме вывода (наподобие CCyS[1:0] = 00), или если он сконфигурирован в одном из режимов ввода (когда биты CCyS[1:0] отличаются от 00).

Те же самые регистры таймера TIMx_CCMRn (n может быть любым числом, но обычно это 1 или 2) используются для конфигурирования каналов таймера на ввод или вывод. Некоторые управляющие битовые поля регистров TIMx_CCMRn по-разному интерпретируются в зависимости от конфигурации канала, режимов ввода или вывода.

Прескалер канала таймера может быть сконфигурирован для снижения частоты активных перепадов, детектированных на входе таймера TIy. Детектирование активного перепада на выходе прескалера приводит к переносу содержимого счетчика таймера в регистр “y” канала таймера TIMx_CCRy.

Содержимое регистра “y” канала таймера TIMx_CCRy это метка времени последнего детектированного активного перепада на выходе прескалера канала “y”. Это метка времени последнего детектированного активного перепада на входе таймера TIy, если прескалер канала “y” сконфигурирован не снижать частоту входного сигнала (например, когда коэффициент деления прескалера = 1 и сигнал проходит через прескалер без изменений, т. е. прескалер отключен).

Блок функции Break.

Функция Break встроена только в те таймеры, у которых есть комплементарные выходы. Другими словами, только те таймеры, у которых как минимум один канал снабжен комплементарными выходами, имеет функцию Break.

Функция Break действует на выходном каскаде каналов таймера в режиме вывода. Как только на входе break детектирован активный перепад, выходы каналов таймера, сконфигурированного в режиме вывода, либо выключаются, либо переводятся в предопределенное безопасное состояние. Функция Break обычно используется для реализации безопасного отключения силового моста в инверторах блоков питания в случае появления каких-то технических аномалий (например, перегрузки по току).

Каскад фильтрации.

Входы таймера (наподобие входа ETR или входов каналов) снабжены каскадом фильтрации, который может быть активирован для отбрасывания внешних импульсов сигнала, длительность которых меньше желаемого порога.

Максимальная длительность фильтруемых импульсов зависит от двух параметров:

• Конфигурация каскада фильтрации относительно определенного входа таймера. Например, каскад фильтрации входа ETR конфигурируется битами ETF[3:0] регистра TIMx_SMCR. Конфигурация каскада входной фильтрации подразумевает выбор источника тактов для оцифровки входных импульсов, установки частоты выборки тактов и установки минимального времени длительности допустимого импульса в единицах тактов уже сконфигурированной частоты оцифровки входного сигнала.

• В случае источника тактов FDTS в качестве тактовой частоты оцифровки, каскад фильтрации настраивается на минимально допустимую длительность проходящего импульса записью значения в поле бит CKD[1:0] регистра TIMx_CR1. Тактовый сигнал FDTS получается из тактового сигнала таймера, и поле бит CKD[1:0] устанавливает соотношение между этими двумя тактовыми сигналами.

Может использоваться один из двух источников тактов в качестве частоты оцифровки входного сигнала для фильтрации, либо сигнал таймера FCK_INT, либо источник тактов FDTS.

Рис. 7 показывает практический пример, где каскад фильтрации активируется для входа таймера ETR. Для этого демонстративного примера настроены следующие параметры:

Частота тактов таймера FCK_INT = 1 МГц.

• CKD [1:0] = 01. Это означает, что частота тактового сигнала FDTS в 2 раза меньше тактовой частоты сигнала таймера: Fdts = Fck_int/2 = 500 кГц.

• ETF [3:0] = 0100. Это означает, что выбран сигнал тактов FDTS в качестве частоты оцифровки для фильтра, пониженной в 2 раза. Также это означает, что допустимый импульс, который пройдет через фильтр, должен быть как минимум быть длительность 6 тактовых импульсов оцифровки.

Для этого примера любой импульсный сигнал на входе таймера ETR, который короче 6 x Tsampling = 6 x 1 / 250 кГц = 24 мкс, будет отброшен.

Рис. 7. Фильтрация входного сигнала (ETF [3:0]= 0100): FSAMPLING = FDTS/2, N=6.

Дата добавления: 2020-01-07; просмотров: 306; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!