Настройка регистров адреса контроллера DMA

Регистр адреса памяти в контроллере DMA используется для конфигурирования места назначения в памяти, когда DMA конфигурируется в режиме передачи из регистров периферийного устройства (в нашем случае в качестве периферийного устройства работает таймер) в память. Также регистр адреса контроллера DMA используется как адрес ячейки памяти источника, когда DMA сконфигурировано для передачи из памяти в регистры периферийного устройства.

Контроллер DMA должен обновлять содержимое серии регистров таймера содержимым из буфера памяти. Адрес, на который указывает регистр адреса DMA, должен быть сконфигурирован на пост-инкремент контроллером DMA для каждой транзакции данных.

Регистр управления DMA-burst таймера

Регистр управления машиной состояний функции таймера DMA burst, TIMx_DCR, используется для конфигурирования количества порций данных во время однократной burst-транзакции. Также он используется для идентификации целевого регистра таймера или источника первой транзакции данных во время первой передачи.

Поле бит DBL [4:0] устанавливает количество порций во время одной burst-передачи, которое должно быть равно количеству регистров таймера, вовлекаемых в процесс (записи или чтения) burst-транзакции. Содержимое поля бит DBA [4:0] идентифицирует начальный регистр, вовлеченный в burst-передачу следи других регистров таймера.

Поле бит DBA[4:0] может идентифицировать до 32 регистров таймера, потому что оно имеет длину 5 бит. Идентификационный номер регистра получается путем деления относительного адреса регистра в карте памяти на 4. Например, у регистра TIMx_CR1 относительный адрес на карте памяти процессора 0x00, поэтому его идентификационный номер 0.

|

|

|

Чтобы сделать burst-транзакцию с началом из регистра TIMx_CR1, поле бит DBA[4:0] должно быть установлено в 0. Чтобы сделать burst-транзакцию с началам из регистра TIMx_ARR, битовое поле DBA[4:0] должно быть установлено в 11 (десятичная форма числа), потому что относительный адрес регистра TIMx_ARR 0x2C, что в десятичной форме равно 44. Делением 44 на 4 получим 11, что будет идентификационным индексом регистра TIMx_ARR для использования в транзакции DMA.

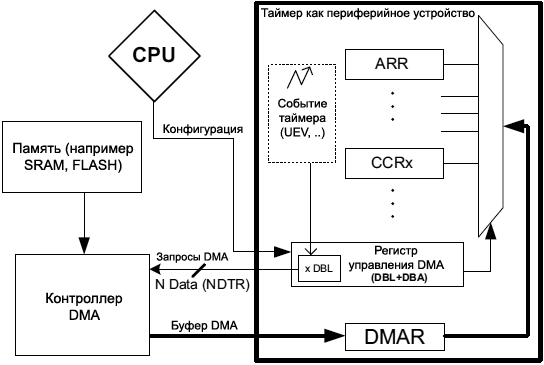

Чтобы завершить одну последовательность транзакции DMA-burst таймера, как показано на рис. 17, должны совместно работать контроллер DMA и аппаратура таймера. Значения данных, используемые для обновления регистров таймера, должны быть сохранены где-нибудь в памяти микроконтроллера. Они могут быть сохранены в памяти SRAM, если шаблон сигнала ШИМ должен обновляться в процессе генерации ШИМ, или в постоянной памяти FLASH, если шаблон рассчитан так, что он не обновляется.

Рис. 17. Конфигурация для последовательности DMA-burst таймера.

|

|

|

Программа микроконтроллера должна сконфигурировать DMA для указания на буфер данных в качестве источника данных для транзакции таймера; также программа должна указать регистр таймера TIMx_DMAR в качестве места назначения передачи данных. И наконец, программа приложения должна сконфигурировать функцию DMA-burst таймера путем записи правильных настроек в регистр таймера TIMx_DCR.

Параграфы выше давали подробное описание того, как конфигурировать функцию DMA burst таймера. Как только правильная конфигурация установлена, вслед за разрешением счетчика таймера должен быть разрешен поток DMA или канал, используемый для передачи данных.

Будучи разрешенным, счетчик таймера будет периодически изменяться либо инкрементированием, либо декрементированием. Через некоторое время, в зависимости от разрешенных запросов DMA таймера, аппаратура таймера может привести к внутренней генерации запроса DMA. Запрос DMA перенаправляется внутри чипа на таймер с помощью логики управления DMA-burst таймера.

На основе значения, сконфигурированного полем длины DMA-burst (DBL[4:0], это битовое поле находится в регистре TIMx_DCR таймера), запрос DMA посылается в контроллер DMA однократно или несколько раз. Если содержимое DBL[4:0] нулевое, то запрос DMA посылается как есть; иначе количество запросов DMA умножается на значение DBL + 1.

|

|

|

Если содержимое битового поля DBL[4:0] равно 2, то как только сгенерируется запрос DMA таймера, логика управления DMA burst таймера пошлет первый запрос DMA в контроллер DMA. Контроллер DMA перешлет содержимое памяти в регистр таймера; место в памяти указывается в регистре источника TIMx_DMAR таймера. Затем указатель источника инкрементируется контроллером DMA, и для таймера подтверждается запрос DMA.

Как только принято первое подтверждение DMA, управляющая логика DMA-burst таймера посылает второй запрос DMA. Этот запрос DMA снова обрабатывается контроллером DMA, и снова таймеру посылается подтверждение запроса.

После получения второго подтверждения DMA, логика управления DMA-burst таймера посылает третий запрос DMA. Этот третий запрос снова обрабатывается контроллером DMA.

Как только таймер получил третье подтверждение от контроллера DMA, последовательность транзакции считается успешно завершенной. После этого логика управления DMA-burst таймера готова к новой последовательности транзакции DMA.

Для ранее описанной последовательности передачи данных регистр назначения передачи, указанный для контроллера DMA, остается тем же самым во время всей последовательности перемещения данных. Тогда этот регистр остается равным регистру таймера TIMx_DMAR.

|

|

|

Логика управления DMA-burst таймера каждый раз перенаправляет доступ на запись в регистр TIMx_DMAR на правильный физический регистр таймера.

Для предыдущего примера, и если поле базового адреса DBA[4:0] регистра TIMx_DCR установлено в 11 (десятичное значение), обратите внимание на следующее:

• Первый DMA-доступ на запись в регистр таймера TIMx_DMAR перенаправляется в регистр таймера TIMx_ARR. Регистр таймера TIMx_ARR выбран базовым адресом для burst-транзакции.

• Второй доступ к регистру TIMx_DMAR таймера со стороны DMA перенаправляется в регистр TIMx_RCR таймера (предполагается, то таймер, используемый для этого примера, оборудован регистром TIMx_RCR).

• Третий доступ DMA к регистру TIMx_DMAR перенаправляется в регистр TIMx_CCR1 таймера.

• По окончании третьего доступа DMA к регистру TIMx_DMAR, управляющая логика DMA-burst таймера возвращает обратно машину состояний перенаправления доступа. Она указывает снова на сконфигурированный базовый регистр для burst-транзакции (регистр TIMx_ARR таймера в этом примере).

Для каждого нового внутреннего запроса DMA, сгенерированного таймером, описанная выше последовательность операций повторяется.

Для использования DMA burst таймера с целью периодического чтения содержимого регистров таймера в определенный буфер в памяти, описанная выше последовательность будет также достоверна. Изменятся только направление транзакции DMA, адрес источника и адрес назначения.

Дата добавления: 2020-01-07; просмотров: 258; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!