ИССЛЕДОВАНИЕ ЦИФРОВЫХ СЧЁТЧИКОВ

Цель работы: Овладеть навыками построения и работы с цифровыми счетчиками

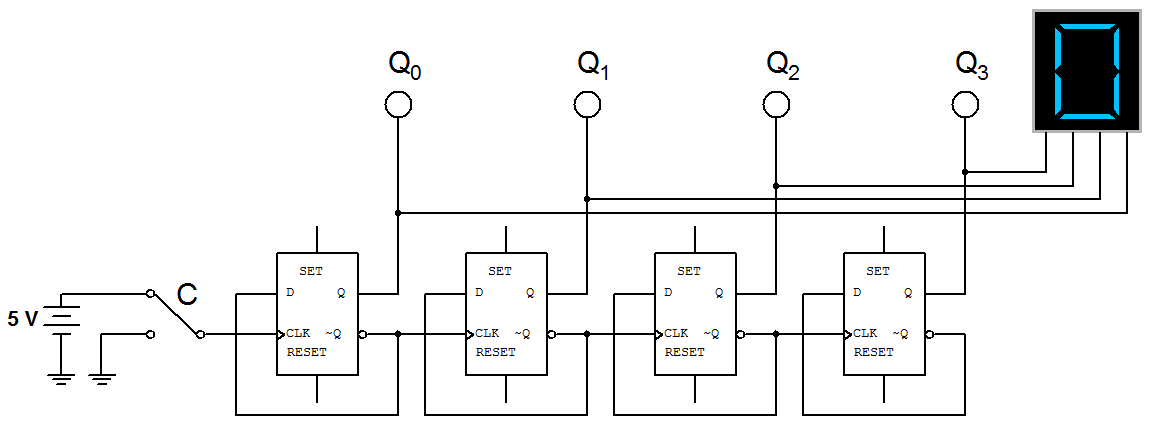

1. В среде Multisim соберите схему, представленную на рисунке 1

Рисунок 1 – Суммирующий счетчик с последующим переносом

2. Соберите схему простейшего суммирующего счётчика с последовательным переносом по рисунку6. Для этого следует воспользоваться синхронизируемыми положительным фронтом D-триггерами (D_FF) из группыMiscDigital, семейства TIL.Для индикации состояния счётчика в виде десятичного числа используется семисегментный индикатор (DCD_HEX) из группыIndicators, семействаHEX_DISPLAY. Спланируйте эксперимент и постройте временные диаграммыQi = f(C) для этой схемы.

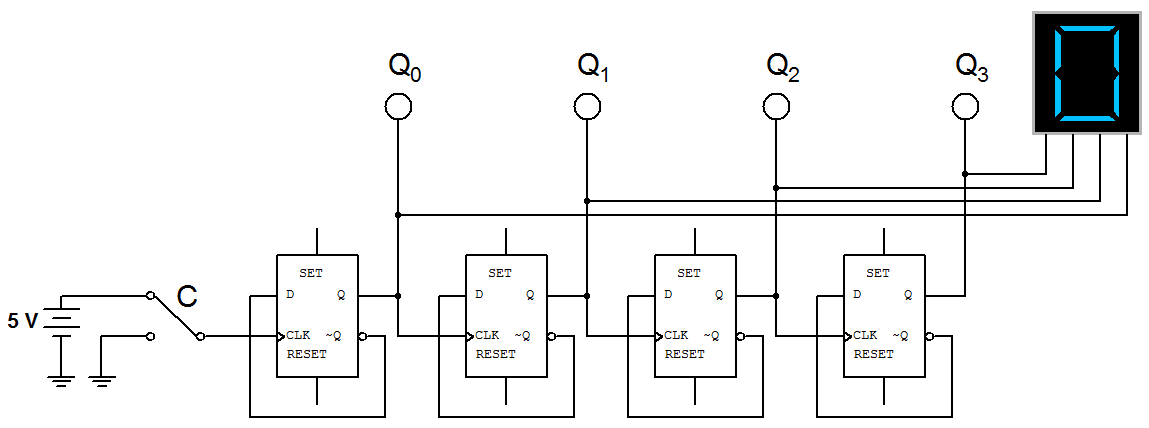

3. Соберите схему простейшего вычитающего счётчика (рисунок 2), отличие которого от схемы на рисунке 6 в том, что входы синхронизации С1 у 2-го, 3-го и 4-го триггеров соединены не с инверсными, а с прямыми выходами 1-го, 2-го и 3-го триггеров. Спланируйте эксперимент и постройте временные диаграммы Qi = f(C) для этой схемы.

Рисунок 2 – Вычитающий счетчик с последовательным переносом

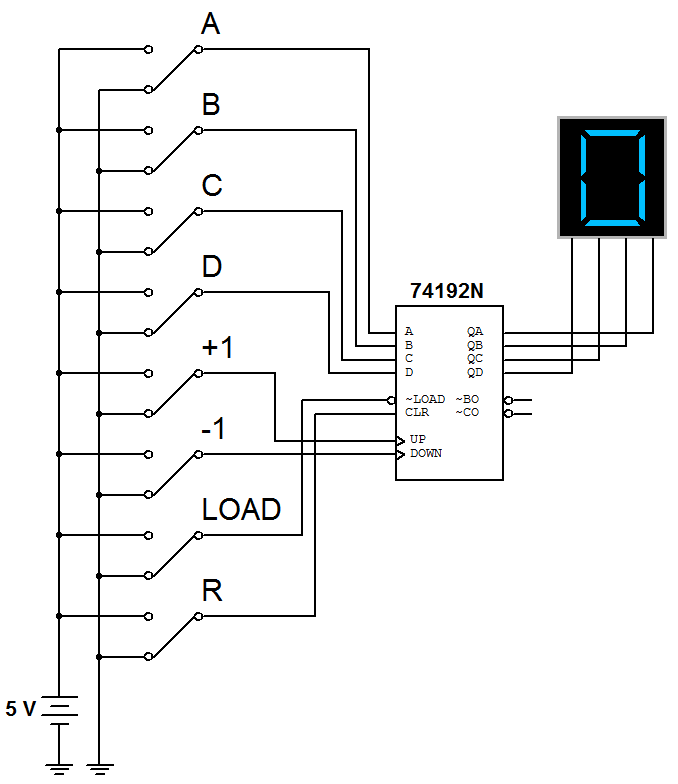

4. На рисунке 3 приведена схема для исследования универсального двоично-десятичногосчётчика. Соберите эту схему, используя счётчик 74192Nиз группыTTL, семейства 74STD. Для индикации состояния счётчика в виде десятичного числа используется семисегментный индикатор (DCD_HEX) из группыIndicators, семействаHEX_DISPLAY.

5. Спланируйте эксперимент и постройте временные диаграммыдля различных режимов работы этого счётчика: установка в 0–(R), параллельная запись – (Load), +1 и -1. Постройте графы переходов для счётчика, установленного в начальные состояния 10–(А), 11–(В), 12–(С), 13–(D), 14–(Е), 15–(F) при сигналах +1 и -1.

|

|

|

Рисунок 3 – Исследование универсального двоично-десятичного счетчика

На рисунке 3 использованыобозначения:

A, B, C, D – входы для параллельной записи в счётчик двоичного числа;

LOAD – (инверсный сигнал) – синхронизация параллельной записи числа в счётчик;

R – установка счётчика в состояние 0000;

+1 – прибавление к содержимому счётчика единицы (положительный фронт);

–1 – вычитание из содержимого счётчика единицы (положительный фронт).

6. Получите у преподавателя задание на проектирование счётчика с параллельным переносом на D-триггерах и нетрадиционным порядком счёта:

1 вариант: счёт – 1,3,7,4,0;2 вариант: счёт – 0,3,6,4,0;

3 вариант: счёт – 1,3,7,4,8;4 вариант: счёт – 7,5,3,1,0;

5 вариант: счёт – 0,3,1,4,2;6 вариант: счёт – 5,7,3,2,0;

7 вариант: счёт – 3,2,1,5,7;8 вариант: счёт – 2,3,4,1,5.

Соберите схему спроектированного счётчика и исследуйте её на соответствие вашему варианту задания. Постройте граф переходов.

Лабораторная работа № 14

|

|

|

ИССЛЕДОВАНИЕ СХЕМ СУММАТОРОВ И АЛУ

Цель работы: исследовать работу схем сумматоров и арифметико-логических устройств.

Краткая теория

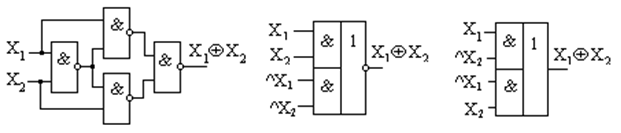

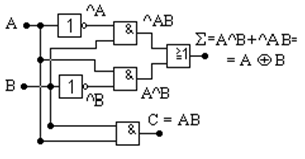

Сумматор по модулю 2 – цифровой узел с m входами и одним выходом, работающий в соответствии со следующим правилом: сигнал 1 появляется на его выходе всякий раз, когда в наборе входных сигналов содержится нечётное число 1. Поэтому этот узел ещё называют схемой проверки на чётность. В частном случае при числе входов равном 2, сумматор по модулю 2 выполняет функцию логического элемента «Исключающее ИЛИ»: на выходе 1 будет только при 1 на одном из входов. Функциональные схемы двухвходовых сумматоров по модулю 2 приведены на рисунке 1. Реализуемая здесь логическая функцияS= А*^В v ^А*В, где символ «^» есть признак инверсии.

а) б) в)

Рисунок 1 – Сумматор по модулю 2:

а) функциональная схема на элементах И-НЕ;

б) на элементах И-ИЛИ-НЕ;

в) на элементах И-ИЛИ

При суммировании двух одноразрядных чисел имеем: 0 + 0 = 0, 1 + 0 = 1, 0 + 1 = 1 и 1 + 1 = 10. В последнем случаечисло 10 (в десятичной записи это 2) оказалось двоичным двухразрядным. Появившаяся в старшем разряде суммы единица называется единицей переноса.

|

|

|

К схеме «Исключающее ИЛИ» несложно добавить выход переноса, т.е. генератор старшего разряда. Для этого оба суммируемых одноразрядных числа следует подать на схему И, выход которой даст необходимый старший разряд переноса 1 * 1 = 1. На рисунке 2 показана реализация схемы суммированиядвух одноразрядных чисел, состоящая из элементов «Исключающее ИЛИ» и «И». Схема имеет два выходных сигнала: суммы S и переноса С. Такая схема называется полусумматором. Таблица состояний полусумматора показана – таблица 1.

Рисунок 2 – Полусумматор

Таблица 1 – Таблица состояний полусумматора

| Слагаемое | Результат | ||

| A | B | Сумма ∑ | Перенос Cn+1 |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

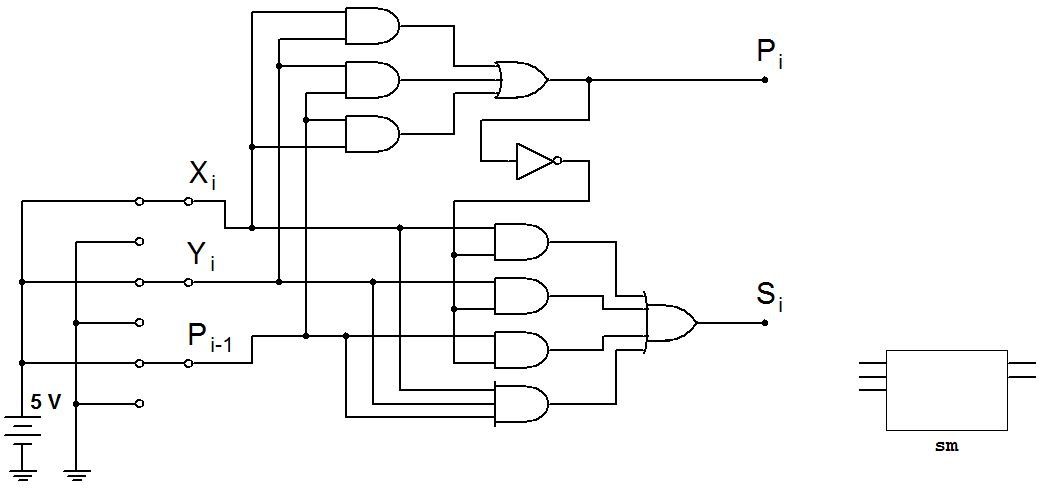

Полный сумматор должен иметь вход для сигнала переноса Сn от соседнего младшего разряда. Схема полного сумматора двух одноразрядных слов показана на рисунке 3, а таблица истинности – таблица 2. В последнем столбце таблицы результаты суммирования даны в десятичной форме. В присутствии входной единицы переноса Сn сумма чисел А и В увеличивается на единицу.

Рисунок 3 – Полный сумматор

|

|

|

Таблица 2 – Таблица состояний полного сумматора

| Слагаемые | Результат суммирования | ||||

| Cn | A | B | Двоичный код | Десятичное число | |

| ∑ | Cn+1 | ||||

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 | 1 | 2 |

| 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 | 2 |

| 1 | 1 | 0 | 0 | 1 | 2 |

| 1 | 1 | 1 | 1 | 1 | 3 |

Полные сумматоры многоразрядных чисел составляются из одноразрядных и могут складывать многоразрядные числа с двумя способами переноса: параллельным или последовательным. При параллельном переносе реализуется одновременное поразрядное сложение слов, при последовательном переносе - формирование сигналов переноса для старших разрядов происходит после выполнения операции сложения в младших разрядах. Поэтому время выполненияоперации сложения N-разрядных чиселравно N*T3, где T3 – задержка на одном одноразрядном сумматоре.

Методика выполнения

2.1. Включите необходимое программное обеспечение.

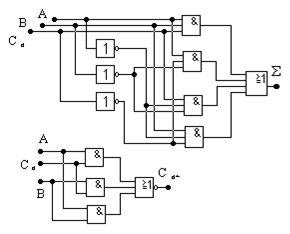

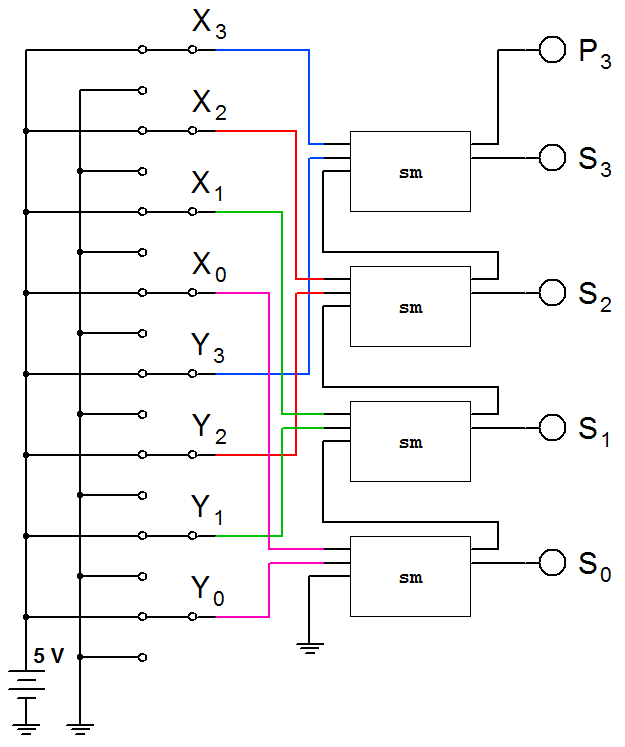

2.2. Соберите схему одноразрядного сумматора по рисунку 4,а, экспериментально получите таблицы истинности для суммы Si и переноса Pi. Создайте из схемы рисунка 4,а субсхемуsm одноразрядного сумматора по рисунку 4,б.

а) б)

Рисунок 4 – Одноразрядный сумматор:

а)функциональная схема;

б)субсхема

Рисунок 5 – Четырехразрядный сумматор

2.3. Соберите схему четырёхразрядного сумматора по рисунку 5 на базе субсхемыsm и исследуйте его работу приразличных значениях двоичных чисел X и Y. Результаты оформить в виде таблицы 3.

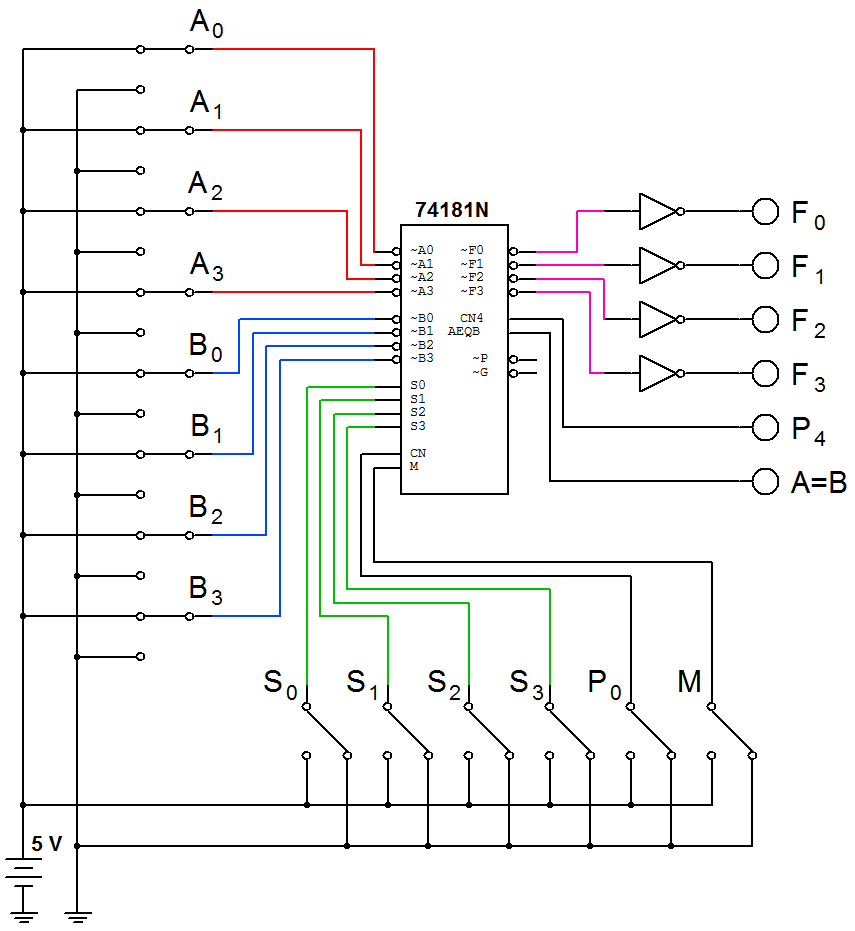

2.4. Соберите схему для исследования работы арифметико-логического устройства АЛУ по рисунку 6. Для этого следует выбрать из группыTTL(семейство74STD) микросхему74181N–арифметико-логическое устройство. Это АЛУ выполняет поразрядные логические операции (при М = 1) над четырёхразрядными словами А и В, а так же арифметические операции (при М = 0). На результатлогических операций не оказывает влияния значение Р0 –перенос от младших разрядов. Код выполняемой операции задаётся значениямиS3S2S1S0.

Обратите внимание на то, что входы АЛУ для операндов А и В – инверсные. Поэтому на переключателях Аi, Вi значению логической единицы в АЛУ соответствуют верхние положения ключей. ВыходыF3F2F1F0– также инверсные. Для удобства исследования АЛУ выходы подключены к индикаторам через инверторы.

Рисунок 6 – Схема для исследования арифметико-логического устройства

Рисунок 6 – Схема для исследования арифметико-логического устройства

По клавише «F1» можно раскрыть таблицу истинности для АЛУ. В этой таблице 4 все выражения записаны для прямых значений операндов А, В и результата F.В столбце«LOGICFUNCTIONS» символом «+» обозначена поразрядная логическая операция «ИЛИ», символом «+» обозначена поразрядная логическая операция «ИСКЛЮЧАЮЩЕЕИЛИ». В столбцах «ARITHMETICOPERATIONS»словами «PLUS» и «MINUS» обозначены соответствующие арифметические операции. Символами «H», «L»в таблице 4 обозначены логические «1»и «0».

2.5. Задайте М = 1.Из имеющихся 16 логических операций проверьте правильность реализации любых 4 для двух произвольных комбинаций операндов A и B в каждой из них. Из восьми наборов операндов А и В в двух случаях эти операнды должны совпадать для проверки истинности сигнала А = В на выходе АЛУ. Составьте таблицу 5 результатов проверки, в которой укажите теоретические значения выходных величин для заданной логической функции и их экспериментальные значения. Сделайте вывод.

2.6. Задайте М = 0 при отсутствии переноса (Р0 = 0). Затем повторите действия п. 2.5. для проверки реализации арифметических операций, сведя результаты в таблицу 6. Сделайте вывод.

2.7. Задайте М = 1 при наличии переноса (Р0 = 1). Затем повторите действия п. 2.5.для проверки реализации арифметических операций, сведя результаты в таблицу 1. Сделайте вывод.

Рисунок 7 – Таблица истинности АЛУ 74181N

Дата добавления: 2018-04-05; просмотров: 1242; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!