ИССЛЕДОВАНИЕ СТАТИЧЕСКИХ ТРИГГЕРОВ

Цель работы: исследовать статические триггеры и их виды.

Краткая теория

Триггер представляет собой электронное устройство с двумя состояниями устойчивого равновесия, что и делает его удобным для хранения информации в двоичной системе счисления. Бистабильный триггер имеет два выхода, причём информация на одном из выходов ^Q представляет собой инверсию информации на другом выходе Q (^– знак инверсии логической переменной). Запись информации в триггер обычно осуществляют через схему управления.

Триггеры классифицируют по ряду признаков. По функциональным возможностям выделяют:

а) триггер с раздельной установкой 0 и 1 (RS-триггер);

б) триггер с приёмом информации по одному входу (D-триггер), другое название – триггер задержки;

в) триггер со счётным входом (T-триггер);

г) универсальный триггер (JK-триггер).

Таблица 1–Таблица истинностидля триггера как элемента памяти

| Такт n | Такт n+1 | Режим | ||

| Qn | R | S | Qn+1 | |

| Qn | 1 | 0 | 0 | Reset – уст. 0 |

| Qn | 0 | 1 | 1 | Set – уст. 1 |

| Qn | 0 | 0 | Qn | хранение |

| Qn | 1 | 1 | н/о | запрет |

Рисунок 1 –Карта Карно для триггера, как элемента памяти

По способу приёма информации триггеры подразделяют на асинхронные (нетактируемые) и синхронные (тактируемые). Первые реагируют на информационные сигналы в момент их появления на входах триггера. Вторые реагируют на информационные сигналы при наличиисигнала синхронизации на специальномвходе С. Синхронные триггеры подразделяют на триггеры, синхронизируемые импульсом (реагируют при подаче на вход С уровня 1 для прямого С-входа или 0 для инверсного С-входа),и синхронизируемые фронтом (реагируют на информационные сигналы в момент изменениясигнала на С-входе от 0 к 1 – положительный фронт или от 1 к 0 – отрицательный фронт).

|

|

|

Основой любого триггераявляется элемент памяти. Чаще всего в статических триггерах эту роль выполняет бистабильная ячейка памяти (простейший асинхронный RS-триггер), котораяфункционирует в соответствии с таблицей истинности, приведённой на рисунке 1,а. Исходное остояние триггера характеризуется сигналом на прямом выходе Qn , а новое состояние Qn+1 определяется комбинацией входных сигналов (н/о– не определённое состояние). Например, для установки триггера в состояние 0необходимо на его входы подать такую комбинацию сигналов, при которой на прямом выходе сигнал будет иметь уровень логического 0, т. е. Qn+1 = 0, а ^Qn+1 = 1.

Из таблицы истинности и карты Карно следует, что поведение такого элемента памяти описывается следующим характеристическим уравнением:

| Qn+1=Sv ^R*Qn | (1) |

Если воспользоваться правилом, что двойное отрицание не меняет значение логической функции, то выражение (1) можно записать в следующем виде:

|

|

|

| Qn+1 = ^^( Sv ^R * Qn) | (2) |

и в соответствии с формулами де-Моргана

| Qn+1 = ^ ( ^S* ^( ^R * Qn ) ) | (3) |

Здесь знаки^^(…) или ^(…) означают двойную или одинарную инверсию выражения в скобках.

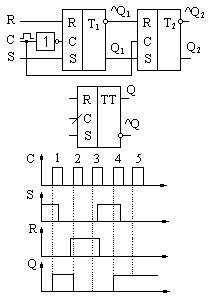

Выражения (2) и (3) определяют два варианта построения элемента памяти –RS-триггера, функционирующего в соответствии с таблицей 1. Первый строится на логических элементах (ЛЭ) ИЛИ-НЕ, а второй – строится на элементах И-НЕ.На рисунке 2 приведены функциональные схемы, условные обозначения и временные диаграммы асинхронныхRS-триггеров, построенных на ИЛИ-НЕ (рисунок 2,а) и на И-НЕ (рисунок 2,б).

Для RS-триггера на ЛЭ ИЛИ-НЕ активным является уровень логической 1. По временной диаграмме (рисунок 2,а) видно, что единичный сигнал на S-входе устанавливает триггер в состояние “1” (на его выходе Q = 1). По окончании действия сигнала S = 1 на входах триггерасигналы S = R = 0 (режим хранения). Сигнал R = 1 устанавливает триггер в состояние “0” (Q = 0). Пунктиром отмечен интервал времени одновременного появления на R- и S-входах логической 1, что является запрещённым состоянием для триггера этого типа. Состояние выходного сигнала Q в этот интервал времени не определено (пунктирная линия). После сброса до 0 сигнала на R-входе Q = 1 за счёт действия логической 1 на S-входе. Прекращение действия сигнала на S-входе и состояние S = R = 0 устанавливает режим хранения для Q = 1.

|

|

|

а) б)

Рисунок 2 – Функциональные схемы, условные обозначения и временные диаграммы RS-триггера на ИЛИ-НЕ (а) и И-НЕ (б)

Рисунок 3 – Функциональная схема тактируемого RS-триггера, условное обозначение и временные диаграммы

Для RS-триггера на ЛЭ И-НЕ активным является уровень логического0. По временной диаграмме (рисунок 2,б) видно, что состояние S = R = 1 обеспечивает режим хранения, поддерживая Q = 0. Логический 0 на S-входе устанавливает Q = 1, сохраняющийся и при возвращении S-входа к уровню 1. Отрицательный импульс на R-входе устанавливает Q = 0. Затем в течение короткого интервала времени R = S = 1 (режим хранения Q = 0), и установка 1 (при S = 0, Q = 1), что и сохраняется в дальнейшем при R = S = 1.

Большее применение находиттактируемый RS-триггер, переключение которого происходит при наличии импульса синхронизации С. Поэтому его характеристическое уравнение

| Qn+1 = C*( Sv ^R* Qn ) v ^C* Qn | (4) |

Для построения функциональной схемы устройства, реализующего данное уравнение, применим по аналогии с (2) и (3) двойное инвертирование уравнения (4) и формулы де-Моргана. Тогдаимеем

|

|

|

| Qn+1 =^^(C*S v C*^R*Qn v ^C*Qn)=^^(C*S v Qn *(C*^R v ^C)=^^(C*S v Qn*(^R v ^C))=^(^(C*S)*^(Qn* ^(R*C))) | (5) |

Это уравнение определяет функциональную схемуRS-триггера, синхронизируемого импульсом С (рисунок 3). Здесь же приведены его условное обозначение и временные диаграммы работы.

По временным диаграммам рисунка 3 видно, что появление высокого уровня Q выходного сигналатриггера происходит при наличии первого импульса на С-входе (S = 1). Это состояние сохраняется и после окончания действия импульса на S-входе за счёт второго тактового импульса С-входа. Установка триггера в «0» (R = 1) происходит только при появлении третьего синхроимпульса, и состояние Q = 0 поддерживаетсяв течение времени действия третьего синхроимпульса и паузы между третьим и четвёртым синхроимпульсами. Одновременное действие S = R = 1 при четвёртом синхроимпульсе и последующей паузе является запрещённым состоянием, поэтому выходной сигналне определён (пунктирная линия) и установление Q = 1 за счёт S = 1 происходит только при пятом синхроимпульсе. Далее это состояние Q = 1 сохраняется ( режим хранения S = R = 0).

Недостатком синхронизируемого импульсом RS-триггера является возможность изменения его состояния в течение всего времени действия синхроимпульса. Это обстоятельство устранено в RS-триггере, синхронизируемом фронтомимпульса С.

На рисунке 4 приведены функциональная схема RS-триггера, синхронизируемого передним фронтом импульса, его условное обозначение и временные диаграммы работы. Синхроимпульс подаётся на C-вход триггера T1 через инвертор. Поэтому при C = 0 Т1 реагирует на изменения сигналов на входах R и S, нужным образом устанавливая Q1 и ^Q1. В момент изменения синхроимпульса C от 0 к 1 Т1 перестаёт реагировать на изменения R и S, а его последнее состояние Q1 и ^Q1 запоминается на Т2, так каксинхроимпульс на его С-входе равен 1. Далее при C = 1 Т1 не реагирует на изменения R и S ,Q1 и ^Q1 постоянны. Второй триггер T2 сохраняет свое состояние.

Рисунок 4 – Функциональная схема, условное обозначение и временные диаграммы синхронизируемого передним фронтом RS-триггера

Двухступенчатое запоминание информации в этом триггере отображаетсядвумя буквами T в условном его обозначении. Реакция схемы на передний фронт идентифицируется отрезком под углом 45о на линии ввода сигнала в С-вход.

Временные диаграммы работы триггера на рисунке 4 показывают переход ТТ в единичное состояние за счёт S = 1 по переднему фронту первого синхроимпульса и возвращение Q = 0 по переднему фронту второго синхроимпульса ввиду R = 1. Четвёртый импульс вновь устанавливает Q = 1 за счёт S = 1, и далее при S = R = 0 реализуется режим хранения состояния Q=1. Такое схемотехническое построение триггера существенно повышает его устойчивость к воздействию различных помех.

Аналогично рисунку 4 может быть построена схема RS-триггера, синхронизируемого задним фронтом синхроимпульса. Для этого инвертор должен быть включён в цепь на С-вход второго триггера. На условном обозначении управляемого задним фронтом RS-триггера отрезок на линии С-входа размещается под углом в 135о (рисунок 5).

Рисунок 5–Условное обозначение управляемого задним фронтом RS-триггера

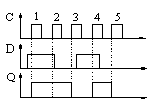

D-триггер имеет один информационный вход (D-вход) и вход для синхронизирующего импульса. Его функционирование реализуется в соответствии с таблицей истинности (таблица 2), из которой можно записать характеристическое уравнение для D-триггера:

| Qn+1 =C*Dv ^C*Qn | (6) |

D-триггер строится на базе RS-триггера. Если у RS-триггера, работающего согласно уравнению Qn+1= C*(Sv ^R * Qn) v ^C* Qnна вход Sподать значение D (S = D), а на вход R подать значение ^D (R = ^D), то получим характеристическое уравнение D-триггера:Qn+1= C*(DvD * Qn) v ^C *Qn=C*Dv ^C*Qn(рисунок 6,а). Здесь же на рисунке 6 показано условное обозначение D-триггера (б) и временные диаграммы его работы (в). СинхронизацияD-триггера производится по переднему(для рисунка 6) или заднемуфронту тактирующего импульса.

Таблица 2– Таблица истинности D-триггера

| Q | Qn | D | Qn+1 | Режимы |

| 0 | Qn | x | Qn | хранение |

| 1 | x | 1 | 1 | set–уст. 1 |

| 1 | x | 0 | 0 | reset – уст. 0 |

а) б)

в)

Рисунок 6 – Функциональная схема (а), условное обозначение (б) и временная диаграмма (в) D-триггера

Т-триггер – это триггер с одним так называемым счётным входом, изменяющий своё состояние с приходом каждого входного импульса. Функционирование триггера должно идти в соответствии с таблицей истинности (таблица 3), на основании которой можно записать характеристическое уравнение в виде

| Qn+1=C*Qnv ^C*Qn, | (8) |

а на основании последнего получить Т-триггер из D-триггера, положив D = ^Qn. Функциональная схема Т-триггера показана на рисунке 7.

Таблица 3 – Таблица истинности T-триггера

| T | Qn | Qn+1 |

| 0 | Qn | Qn |

| 1 | Qn | ^Qn |

Рисунок 7 – Функциональная схема T-триггера

Таблица 4 – Таблица истинности для JK-триггерапри C = 1

| Qn | J | K | Qn+1 | Режим |

| Qn | 1 | 0 | 1 | set–уст. 1 |

| Qn | 0 | 1 | 0 | reset – уст. 0 |

| Qn | 0 | 0 | Qn | хранение |

| Qn | 1 | 1 | ^Qn+1 | счетчик |

Рисунок 8– Карта Карно для JK-триггерапри C = 1

Большими логическими возможностями обладает ТV-триггер, имеющий два логических входа Т и V , первый из которых является счётным, а второй – разрешающим. ТV триггер при V = 1 выполняет функции Т-триггера; если на входе V действует запрещающий сигнал 0, состояние триггера не меняется. Характеристическое уравнение, описывающее логические возможности ТV-триггера, определяется соотношением: Qn+1=Qn(^Tv ^V) v ^QnT*V).

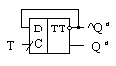

JK-триггер имеет два информационных входа: J и K, а так же вход для тактовых импульсов C. Правило работы JK-триггера определяется его таблицей истинности (таблица 4) и картой Карно (рисунок 8), на основании которых можно записать следующее характеристическое уравнение:

| Qn+1 = C* (J*^Qnv ^K*Qn) vC*Qn, | (9) |

на основании чего можно составить функциональную схемуJK-триггера (рисунок 9,а). Этот триггер строится на базе RS-триггера введением обратных связей с прямого и инверсного выходов на два входных элемента И, объединяющие сигналы обратной связис сигналами управления J и K.На рисунке 9,б приведено условное обозначение триггера этого типа, временные диаграммы (в) иллюстрируют его работу. В момент совместного действия логических 1 на входах J и К передний фронт третьего синхроимпульса вызывает срабатывание триггера в счётном режиме, изменяяQ с величины 0 на значение 1.

а) б) в)

Рисунок 9 – Функциональная схема (а), условное обозначение (б) и временные диаграммы (в) JK-триггера при C = 1

При отсутствии синхроимпульсов, т.е. С = 0 JK-триггер работает в режиме хранения. На базе JK-триггера можно получить схемы всех остальных триггеров, что и приведено на рисунке 10.

а) б) в)

Рисунок 10–Использование JK-триггера для получения триггеров других типов: а) T-триггер;б) D-триггер;в) JK-триггер

Методика выполнения

2.1. Включите необходимое программное обеспечение.

2.2. Соберите на монтажном столе схему асинхронного статического триггера по рисунку 2,б. Убедитесь в её работоспособности, спланируйте эксперимент и результаты запишите в виде таблицы истинности Qn+1 = f(S, R, Qn). Логические переменные R и S на входах задавайте с помощью переключателя кнопочного на два положения (SPDT) из группыBasic, семейства SWITCH,подключённые одним выводом к источнику +5 вольт, а другим выводом – к земле. Индикацию состояния выходов триггера обеспечьте индикаторами (PROBE) из группыIndicators, семействаPROBE. Составьте характеристическое уравнение RS-триггера.

2.3. При исследовании схем с триггерами перед началом эксперимента необходимо установить триггера в определённое состояние (например, в логический 0), так как моделирующая программа не можетразрешить противоречие: неизвестны значения Qn и ^Qn, аS = R = 0, т.е. задан режим хранения, а состояние Qn – неизвестно. Поэтому во всех схемах этой работы первым шагом моделирования должна быть установка триггеров в определённое состояние (логический 0). Для этого в схему синхронизируемого импульсом RS-триггера на рисунке 3 в логическом элементе 4 введён переключатель с задержками во времени (TD_SW1) из группыBasic, семейства SWITCH, у которого TimeOn = 100 nc, а TimeOff = 10000 c. (рисунок 11) .Этот переключатель в момент начала моделирования включается и подаёт логический 0 на дополнительный входстатического элемента памяти и устанавливает его в состояние логического 0, а через 100 nс отключается и подаёт на этот вход логическую 1. С этого момента времени элемент памяти может нормально функционировать в моделирующей программе.

а) б)

Рисунок 11 – RS-триггер, синхронизируемый импульсом C (а), и субсхемаRST-CIна его основе (б)

Соберите схему синхронизируемого импульсом RS-триггера по рисунку 11,а. Убедитесь в её работоспособности, спланируйте эксперимент и результаты запишите в виде таблицы истинности Qn+1 = f(S,R,Qn) при С = 1. Составьте характеристическое уравнение. Убедитесь, что в начале моделирования триггер устанавливается в состояние 0. Поместите эту схему в субсхемуRST_CI (рисунок 11,б).

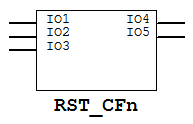

2.4. Используя субсхемуRST_CI, соберите RS-триггер, синхронизируемый отрицательным фронтом импульса синхронизации по рисунку 12,а. Спланируйте эксперимент по исследованию схемы. С помощью логического анализатора из моделирующей программы продемонстрируйте преподавателю временные диаграммы зависимостей Q1 и Q2 от R, S и C. Поместите RS-триггер с синхронизацией от отрицательного фронта импульса в субсхемуRST_CFn (рисунок 12,б), убрав предварительно индикацию состояний Q1, ^Q1.

а)

б)

Рисунок 12 – RS-триггер, синхронизируемый отрицательным фронтом импульса (а), и его субсхема (б)

2.5. Соберите схему D-триггера по рисунку 13,а. Убедитесь в её работоспособности, спланируйте эксперимент и результаты запишите в виде таблицы истинности Qn+1 = f(D,C,Qn). Составьте характеристическое уравнение для D-триггера. Поместитесхему в субсхемуDT_CFn (рисунок 13,б).

а)

б)

Рисунок 13 – D-триггер, синхронизируемый отрицательным фронтом импульса (а), и его субсхема (б)

2.6. Соберите схему JK-триггера по рисунку 14,а. Убедитесь в её работоспособности, спланируйте эксперимент и результаты запишите в виде таблицы истинностиQn+1 = f(J,K,C,Qn). Составьте характеристическое уравнение для JK-триггера. Поместите эту схему в субсхемуJKT_CFn (рисунок 14,б).

а)

б)

Рисунок 14 – JK-триггер, синхронизируемый отрицательным фронтом импульса (а), и его субсхема (б)

Для использования созданных субсхем в новых схемах (в отдельных файлах) необходимо поместить их в контейнер HierarchicalBlock (иерархический блок) через буфер обмена и сохранить.

Иерархическийблоксоздается командой«Place → NewHierarchicalBlock…», в открывшемся окне нужно будет ввести название блока и число входных и выходных разъемов.

Иерархическийблок сохраняется как отдельный файл, с названием совпадающим с именем блока. Вставка существующего иерархического блока в новый файл осуществляется командой «Place → HierarchicalBlockfromFile…».

Лабораторная работа №12

ИССЛЕДОВАНИЕ РЕГИСТРОВ

Цель работы: Исследовать простейший сдвигающий регистр на D-триггерах, используя триггеры из группыMiscDigital, семейства TIL; исследовать универсальный регистр.

Краткая теория

Совокупность из нескольких триггеров, предназначенных для хранениядвоичного кода, называется регистром.Введением дополнительной логики функциональные возможности регистров расширяются, обеспечивая возможность сдвига записанной информации в ту или иную сторону.

В соответствии с назначением различают регистры хранения, регистры сдвига и универсальные регистры.

По принципу хранения информации регистры делятся на статические и динамические. Статические регистры строят на потенциальных элементах памяти (триггерах), которые могут хранить записанную информацию сколь угодно долго ( при наличии напряжения питания). Динамические регистры строят на элементах памяти такого типа, как конденсатор, которые могут хранить информацию лишь в течение некоторого промежутка времени. Поэтому в динамических регистрах необходима регенерация записанной информации.

Важнейшие характеристики регистров – разрядность и быстродействие. Разрядность определяется количеством триггеров. Быстродействие характеризуется максимальной тактовой частотой, с которой может производиться запись, чтение и сдвиг информации.

Наиболее широко распространены регистры сдвига, предназначенные для преобразования информации путём её сдвига под воздействием тактовых импульсов. Такие регистры представляют собой совокупность последовательно соединённых триггеров, как правило, двухступенчатой структуры. По направлению сдвига информации различают регистры прямого сдвига (вправо, т.е. в сторону младшего разряда), обратного сдвига (влево, т. е. в сторону старшего разряда) и реверсивные, допускающие сдвиг в обоих направлениях.

В простейшем регистре триггеры соединены последовательно: выходы Q и ^Qпредыдущего триггера передают бит данных на входы R и S последующего. Все тактовые входы C триггеров соединены параллельно. При таком включении единица, записанная в виде напряжений низкого и высокого уровней по входамR и S первого триггера, после подачи одного тактового импульса перейдёт во второй триггер, затем во время следующего тактового импульса она попадёт в третий триггер и так последует далее, до конца регистра.

Аналогично продвигается по регистру многоразрядное слово: оно поразрядно вводится на входыR и S первого триггера. Простейший регистр имеет один вход и один выход – последовательные. Вход управления также единственный – тактовый. Если ко входу каждого триггера добавить разрешающую логику, можно получить дополнительные, так называемые параллельные входы одновременной загрузки байта в регистр. Здесь, как правило, используют дополнительные защёлки, где фиксируются данные, поступившие на входы после прихода тактового импульса. В такую схему добавляется вход разрешения записи.

Можно предусмотреть также логическую схему параллельного отображения на выходе состояния каждого триггера. Тогда после заполнения регистра от последовательного или параллельного входов по команде разрешения выхода накопленное цифровое слово можно отобразить поразрядно сразу на всех параллельных выходах.Для удобства поочерёдной выдачи данных от такихрегистров – буферных накопителей в шину данных обрабатывающего устройства – процессора – параллельные выходы регистров снабжаются выходными буферными усилителями, имеющими третье, разомкнутое Z-состояние. По многопроводной шине данных процессор получает цифровое слово – байт от выходов того регистра, которому дана команда разрешения выдачи.

а)

б)

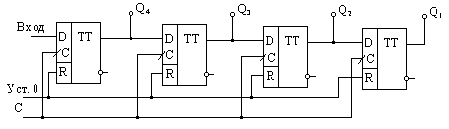

Рисунок 1 – Регистр сдвига:

а) функциональная схема;

б) условное обозначение

Наиболее широко распространены регистры сдвига на D-триггерах(рисунок 1). Такие регистры имеют один информационный вход, вход для импульсов синхронизации(импульсов сдвига) и установочный вход R. Выходы в регистре могут быть с каждого разряда для считывания информации в параллельном коде. Также имеется один выход с последнего (относительно входа) разряда для считывания информации последовательно во времени, т.е. последовательным кодом. Вход регистра для импульсов сдвига получается объединением С-входов всех триггеров, а установочный вход –R-входов.

Перед записью информации регистр устанавливается в нулевое состояние подачей положительного импульса по шине «Уст. 0». Записываемая информация должна быть представлена последовательным кодом. Запись осуществляется поразрядно со стороны старшего (рисунок 1) или младшего разряда (направление сдвига указываетсястрелкой на условном обозначении регистра) путём продвижения кодовой комбинации с каждым тактовым импульсом от разряда к разряду. Следовательно, для записи N-разрядного слова необходимы N-импульсов сдвига.

Считывание информации последовательным кодом осуществляется, как и запись, поразрядным сдвигом записанной кодовой комбинации к выходу с каждым тактовым импульсом. Следовательно, для считывания N-разрядного слова необходимыN импульсов сдвига. Считывание информации параллельным кодом происходит в паузе между последним импульсом сдвига одного цикла записи и первым импульсом сдвига другого цикла записи, т.е. в интервале времени, когда на С-входах триггеров нулевой уровень, и они находятся в режиме хранения.

Рисунок 2 – Разряд реверсивного регистра

Таким образом, с помощью регистра сдвига можно осуществлять преобразование информации из последовательной формы представления в параллельную. Очевидно, если предусмотрена запись информации параллельным кодом, то можно преобразовывать информацию из параллельной формы представления в последовательную.

Регистры сдвига могут быть построены и на триггерах одноступенчатой структуры. В этом случае в каждом разряде регистра нужно использовать два триггера, которые управляются двумя сдвинутыми во времени тактовыми импульсами. Наличие двух триггеров в одном разряде позволяет поразрядно продвигать информацию в регистре от входа к выходу. Если бы в регистре были применены одноступенчатые триггеры по одному на разряд, то правило работы регистра было бы нарушено: при первом же импульсе сдвига информация, записавшись в первый разряд, перешла бы во второй, затем в третий и т.д.

Реверсивные регистры сдвига объединяют в себе свойства регистров прямого и обратного сдвига. Строятся они по тем же схемотехническим принципам, что и рассмотренные регистры, но с использованием

дополнительных логических элементов в межразрядных связях. Указанная особенность реверсивного регистра показана на примере i-разряда (рисунок 2), состоящего из D-триггераи логической схемы, на входы которой поданы:Qi-1-сигнал с выхода младшего разряда, Qi+1-сигнал с выходастаршего разряда, V-сигнал управления направлением сдвига:V = 1 –вправо, V = 0 –влево.

Существуют многорежимные регистры. Их входные и выходные линии данных объединены и образуют так называемый порт данных. Это означает, что от шины данных процессора приходит один провод (а не два), который по команде служит или входным или выходным. Число сигнальных входов и выходов микросхемы за счёт портовой организации можно уменьшить в два раза.

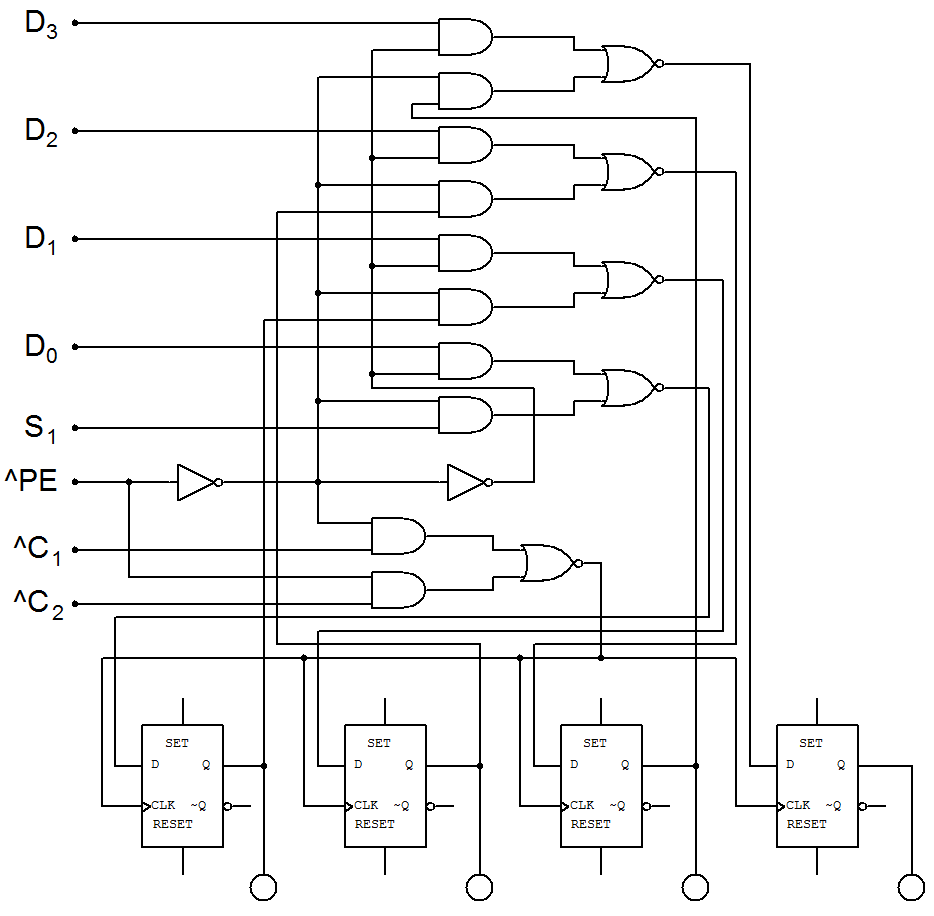

Подробное рассмотрениерегистров проведём на примере микросхемы К155ИР1 – четырёхразрядный сдвиговый регистр, принципиальная схема которого приведена на рисунке 3. Он имеет последовательный вход данныхS1, четыре параллельных входа D0 – D3 , а также четыре выхода Q0 –Q3от каждого из триггеров. Регистр имеет два тактового входа ^C1 и ^С2. От любого из пяти входов данных код поступит на выходы синхронно с отрицательным перепадом, поданным на выбранный тактовый вход.

Рисунок 3 – Схема четырехразрядного сдвигового регистра K155ИР1

Вход разрешения параллельной загрузки ^РЕ служит для выбора режима работы регистра. Если на вход ^РЕ даётся напряжение высокого уровня, разрешается работа тактовому входу ^С2. В момент прихода на этот вход отрицательного перепада тактового импульса в регистр загружаются данные от параллельных входов D0– D3.

Если на вход ^PE подано напряжение низкого уровня, разрешается работа тактовому входу^C1. Отрицательные фронты последовательности тактовых импульсов сдвигают данные от последовательного входаS1 на выход Q0, затем на Q1, Q2 и Q3, т.е. вправо. Сдвиг данных по регистру влево получится, если соединить выход Q3 и вход D2, выход Q2 и вход D1, Q1 и D0 по схеме рисунке 2. Регистр можно перевести в параллельный режим, подав на вход ^РЕ напряжение высокого уровня. Напряжение на входе ^РЕ можно менять только, если на обоих тактовых входах уровни низкие. Однако если на входе ^С1 напряжение низкого уровня, перемена сигнала на входе ^РЕ от низкого уровня к высокому не меняет состояния выходов.

Методика выполнения

2.1. Включите необходимое программное обеспечение.

Рисунок 4 – Сдвигающий регистр на D-триггерах

2.2. Соберите схему простейшего сдвигающего регистра на D-триггерах по рисунку 4, воспользовавшисьD-триггерами (D_FF) из группыMiscDigital, семейства TIL.

Спланируйте эксперимент и постройте временные диаграммыQi = f (D,R,C).

2.3. Соберите схему для исследования универсального регистра по рисунку 5. Для этого используется интегральная микросхема 74198N – восьмибитовыйрегистр сдвига из группыTTL, семейства 74STD.

На этом рисунке:

Da,…,Dh– входы для параллельной записи в регистр байта abcdefgh;

Qa,…,Qh– выходы регистра;

CLK– вход синхронизации;

CLR– вход начальной установки всех разрядов в нуль;

DR, DL– входы для последовательного ввода информации слева и справа;

Рисунок 5 – Схема для исследования универсального регистра

S1, S0– входы, задающие режим работы регистра: параллельная запись, хранение, сдвиги влево и вправо. Для данной схемы спланировать эксперимент и составить таблицу, описывающую поведение регистра при различных режимах (S1и S0), различных значениях на входах регистра (Da,…,Dh, DR и DL). Определить в каких режимах на выполнение операции влияет C, какое действие оказывает R. Выясните необходимые состояния управляющих сигналов для реализации различных режимов работы регистра – запись, хранение, сдвиг влево, сдвиг вправо.

Для режимов сдвига вправо и влево построить временные диаграммы.

Содержание отчета

Отчет лабораторной работы должен содержать:

1. Титульный лист.

2. Цель работы.

3. В соответствии с порядком проведения работы, должны быть приведены:

– схема;

– расчетные формулы; результаты расчетов;

– таблица экспериментальных данных;

– результаты сравнения экспериментальных и расчетных данных:

– выводы по работе.

Лабораторная работа № 13

Дата добавления: 2018-04-05; просмотров: 779; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!