Типовые цифровые узлы АСР и ЭВМ

1 Общие сведения об элементах и узлах АСР и ЭВМ.

2 Триггер – логическая ячейка памяти.

3 Регистры

4 Формирователи – распределители

5 Дешифраторы

6 Счетчики

1 Элементы и узлы цифровых ЭВМ и АСР являются комплексными логическими элементами.

По функциональному назначению цифровые узлы можно подразделить на три основные группы:

1) узлы памяти, выполняющие функцию запоминания поступающих сигналов;

2) логические цифровые узлы, реализующие различные логические функции на основе алгебры логики;

3) вычислительные узлы, выполняющие по соответствующим правилам обычной алгебры вычислительные функции – сложение, умножение, сравнение и т.д.

К первой группе относятся накопители на магнитных элементах и элементы памяти на логических элементах.

Накопители на магнитных элементах – это накопители на основе ферритовых колец с прямоугольной гистерезисной характеристикой намагничивания (ленты, дискеты, диски и т.п).

Элементы памяти на логических элементах построены на триггерных ячейках – это регистры различного назначения.

К группе логических цифровых узлов относятся формирователи-распределители импульсов, дешифраторы (декодеры) и логические переключающие устройства.

К группе вычислительных цифровых узлов относятся такие типовые узлы, как счетчики, сумматоры, узлы сравнения.

2. Триггер – электронное устройство, с помощью которого можно записывать, хранить и считывать двоичную информацию. Он имеет два устойчивых состояния равновесия: одно из устойчивых состояний принимается за логическую 1, а другое – за логический 0.

|

|

|

В схемном отношении триггер представляет собой два простейших усилителя постоянного тока с логикой ИЛИ или И на входе и с взаимно обратными положительными связями, наличие которых приводит к тому, что в устойчивом состоянии один транзистор усилителя открыт, а другой – закрыт. Сигналы снимаемые с выходов триггера, имеют два уровня постоянного напряжения: верхний и нижний. Под воздействием управляющих сигналов, подаваемых на входы, триггер скачкообразно переходит из одного устойчивого состояния равновесия в другое.

Простейший триггер может быть выполнен на двух логических элементах ИЛИ-НЕ. Схема такого триггера и его условное обозначение приведены на рисунке 2.5.7. Триггеры могут быть выполнены на транзисторах, интегральных схемах

R Q

R Q

S S Т Q

S S Т Q

R R Q

R R Q

S Q

S Q

а) б)

|

|

|

Рисунок 2.5.7

Состояние триггера и значение хранимой двоичной информации определяется прямым и инверсным выходными сигналами.

Триггер, приведенный на рис.2.5.7, называется асинхронным RS-триггером. Он представляет собой элементарный конечный автомат, функционирующий в соответствии с таблицей состояний (таблица 2.5.2)

Таблица 2.6.2

| R | S | Q | Примечание |

| 0 0 1 1 | 0 1 0 1 | 0/1 1 0 - | Хранение 0 или 1 Установка 1 Установка 0 Запрещено |

При R = 1 и S = 0 триггер устанавливается в нулевое состояние (Q = 0), при R = 0 и S = 1 – в единичное состояние (Q =1); R = S = 0 триггер сохраняет состояние, в котором он находился до поступления на его входы нулевых сигналов. При R = S = 1 на прямом и инверсном выходах устанавливается нулевой сигнал. Триггерная схема превращается в два независимых инвертора, и при переходе к хранению информации (R = S = 0) триггер может устанавливаться в любое состояние. Поэтому такая комбинация входных сигналов запрещена.

В интегральных системах элементов триггер и схема, управляющая его входами, выполняются в виде конструктивно законченного модуля на одной кремниевой пластинке, заключенной в корпус с выводами. В зависимости от количества входов и особенностей схемы меняется работа триггера. Схемы триггеров можно разделить на несколько типов:

|

|

|

- RS – триггер с установочными входами R,S;

- Т-триггер со счетным входом;

- одно-ходовый D-триггер;

- специфический для интегральных схем универсальный JК-триггер.

Если хотя бы с одного входа информация в триггер заносится принудительно под воздействием синхронизирующего сигнала, то триггер называется синхронизируемым. Если занесение информации в триггер с любого входа производится без синхронизирующего сигнала, то триггер называется асинхронным.

Общая форма условного обозначения триггеров показана на рисунке 2.5.8.

S Т Q S ТТ Q

S Т Q S ТТ Q

|  |  |  |

Х1 Х1

Х1 Х1

С С

С С

Х2 Х2

Х2 Х2

|  |  |  |

R Q R Q

R Q R Q

|

|

|

Рисунок 2.5.8

Символы Т и ТТ обозначают соответственно однотактный и двухтактный триггеры; символы R и S – входы не синхронизируемой установки триггера в состояние 1 и 0, на местах символов Х1 и Х2 могут быть показаны следующие типы входов:

- S – вход раздельной установки триггера в состояние 1;

- R – вход раздельной установки триггера в состояние 0;

- Т – вход триггера со с счетным входом одновременно на входы Х1 и Х2 JК-триггера;

- D - вход D-триггера (единственный);

- J – вход для установки состояния 1 в универсальном JК-триггере;

- К – вход для установки состояния 0 в универсальном JК-триггере;

- С – вход синхронизации.

Если вход отмечен кружком, это означает, что действующее значение входного сигнала – инверсное, т.е. нулевое. Состояние триггера определяется сигналом Q на прямом выходе триггера (или сигналом Q на его инверсном выходе).

Законы функционирования триггеров задаются таблицами переходов, где может быть указано, что новое состояние триггеров либо совпадает с предыдущим, либо является его отрицанием.

3 Регистр – элемент памяти, состоящий из триггерных и логических элементов, обладающий свойством принимать, хранить и по команде выдавать числовые коды. Регистры используются в цифровых ЭВМ в большом количестве для непродолжительного хранения информации, подлежащей оперативной обработке. Они подразделяются на регистры параллельного действия (накопительные) и регистры последовательного действия (сдвигающие). Первые позволяют только принимать, запоминать и выдавать цифровую информацию, а вторые кроме этого – осуществлять сдвиг чисел влево (вправо), что равносильно изменению порядка их величины.

На рисунке 2.5.9 показана схема сдвигающего регистра, построенного на D-триггерах.

В сдвигающих регистрах происходит перемещение всех цифр слова в направлении от старших разрядов к младшим (сдвиг вправо) или от младших разрядов к старшим (сдвиг влево). Сдвиг числа на n разрядов осуществляется за n тактов n микроопераций сдвига. Микрооперация сдвига – сдвиг числа на один разряд вправо или влево относительно принятой сетки. Сдвигающие регистры используют для сдвига кода и для преобразования параллельного кода, который принимается регистром, в последовательный.

Установка регистра в состояние 0 выполняется подачей логической единицы на вход R. По приходу тактового импульса на вход С первый триггер записывает бит, который находится на входе D, а каждый последующий триггер переключается в состояние, в котором находится предыдущий. Так как записанный сигнал проходит с входа D триггеров к выходу У с выдержкой времени, необходима большая длительность фронта тактового импульса, во время которого производится запись.

У1 У2 У3 У4

У1 У2 У3 У4

Uсчит

Uсчит

& & & &

& & & &

|  |  |  |

Х D Т1 D Т2 D Т3 D Т4

Х D Т1 D Т2 D Т3 D Т4

С С С С

С С С С

R R R R

R R R R

Уст "0"

Уст "0"

ТИ

Рисунок 2.5.9.

На рисунке 2.5.10 показана типичная схема накопительного регистра для четырехразрядного двоичного числа.

Регистр состоит из четырех триггеров с прямыми входами и восьми элементов И: И1, И3, И5, И7 установлены на прямых входах, а И2, И4, И6 и И8 – на прямых выходах триггеров. Входы триггеров R соединены с шиной установки в исходное состояние (шин «Уст.0»). На первые входы элементов И1, И3, И5, И7 поступают коды чисел подлежащих записи, а их вторые входы подключены к шине генератора импульсов записи. Считывание информации производится с выходов У1, У2, У3 и У4 элементов И2, И4, И6, И8 при наличии импульсов считывания Uсчит.

У1 У2 У3 У4

У1 У2 У3 У4

U

счит

счит

И2 И4 И6 И8

И2 И4 И6 И8

И1 И3 И5 И7

И1 И3 И5 И7

& & & & & & & &

& & & & & & & &

S Т 1 S Т 2 S Т 3 S Т 4

S Т 1 S Т 2 S Т 3 S Т 4

|  |  |

R R R R

R R R R

Ген. импульса записи (ТИ)

Уст "0"

Уст "0"

Х1 Х2 Х3 Х4

Рисунок 2.5.10

Перед записью по шине Уст.«0» на входы R подают импульс сброса. При этом все триггеры устанавливаются в исходное положение: на прямых выходах устанавливаются логические «0», а на инверсных – логические «1».

Пусть теперь нужно записать число в двоичном коде 1011. Синхронно (одновременно) на первые входы И1, И3, И5, И7 поступают соответственно 1,0,1,1, а на вторые входы импульсы генератора записи. На прямые входы триггеров Т1, Т2, Т3 и Т4 поступят соответственно 1, 0, 1, 1. При этом триггеры Т1, Т3, Т4 сработают и на их прямых выходах появятся «1», а Т2 останется в исходном состоянии, так как через И3 сигнал не пройдет. Код записан.

Для считывания на вторые входы И2, И4, И6, И8 подаются импульсы считывания с шины Uсчит. Элементы И2, И6, И8 откроются и на их выходах появится «1», а элемент И4 останется в закрытом состоянии.

Таким образом, на выходах У1, У2, У3, У4 появятся 1, 0, 1 и 1 соответственно, что совпадает с записанным кодом, который при этом не разрушается, а хранится сколько угодно. Увеличивая число ячеек (один триггер и два элемента И) можно построить регистр для любого числа.

2. К группе логических цифровых узлов относится формирователь-распределитель, который поступающие на вход распределителя импульсы с тактовой частотой fт поочередно распределяет по своим выходам. При этом сигнал на (i + 1) выходе появляется при исчезновении сигнала на i-входе, а снимается сигнал на выходе (i +1) тактовым импульсом Хс.

Схема узла с таким алгоритмом работы, выполненная на D-триггерах с динамическим входом для распределителя с тремя выходами, показана на рисунке 2.5.11,а. На рисунке 2.5.11,б приведена временная диаграмма его работы.

|

D – сокращение английского слова delay – задержка, отсюда и название – D-триггер.

В исходном состоянии предварительно записывается единичный сигнал и на выходе первого триггера У1 =1. При появлении первого тактового импульса единичный сигнал исчезает с выхода триггера Т1 и появляется на выходе триггера Т2 (У2 =1). При следующем тактовом импульсе У2 = 0 и У3 = 1. После третьего тактового импульса за счет обратной связи цикл повторяется.

При этом частота цикла f4 = fт/3.

В общем случае f = fт/n, где n – число триггерных ячеек. Тактовые синхроимпульсы формируются высокостабильными генераторами импульсов.

3. Важным логическим цифровым узлом является дешифратор, который преобразует сигнал на «n» входах, представляющий собой число в двоичном коде, в единичный сигнал на одном из выходов.

В общем случае дешифратор, имеющий «n» входов, имеет 2n выходов, так как n – разрядный код входного числа может принимать 2n различных значений и каждому из этих значений должен соответствовать сигнал на одном из выходов дешифратора.

|

Дешифраторы часто применяют в устройствах управления, когда необходимо код операции преобразовать в управляющий сигнал. В качестве примера рассмотрим работу диодного дешифратора на 4 выхода (рисунок 2.5.12).

Рисунок 2.5.12

Основными элементами схемы являются двухразрядный триггерный регистр и диодная матрица. Если диод подключен к выходу триггера, где имеется низкий потенциал, соответствующий логическому нулю, то диод открывается. Сопротивления резисторов R1÷R4 значительно больше сопротивления открытого диода. Тогда потенциал выходной шины, к которой подключен хотя бы один открытый диод, будет низким, так как практически все напряжение от источника +Е будет падать на одном из резисторов R1÷R4.

Рассмотрим процесс дешифрации чисел, записанных в двоичном коде. Предварительно регистр устанавливается в исходное состояние импульсом сброса. Если на входе Х1 = 0 и Х2 = 0 (число 0), то оба триггера на прямых выходах будут иметь низкие потенциалы, а на инверсных – высокие. Диоды Д1, Д2, Д5, Д6 будут открыты, а диоды Д3, Д4, Д7, Д8 – закрыты. Высокий потенциал будет на выходной шине Р1.

Если на входе Х1 = 1, а Х2 = 0 (число «1»), то на прямом выходе Т1 будет высокий потенциал, а на прямом выходе Т2 – низкий. На инверсных выходах потенциалы противоположны. Тогда открываются диоды Д1, Д2, Д7, Д8, а диоды Д3, Д4, Д5, Д6 будут закрыты. Высокий потенциал будет на шине Р2.

Пусть Х1=0, а Х2=1 (число 2). Тогда высокие потенциалы будут на прямом выходе Т2 и на инверсном Т1. Диоды Д1, Д2, Д7, Д8 будут закрыты, а диоды Д3, Д4, Д5, Д6 открыты. Высокий потенциал будет на шине Р3.

Если Х1=1 и Х2=1, что соответствует числу 3, то оба триггера будут находиться в единичном положении и на их прямых выходах будут высокие потенциалы. Таким образом, диоды Д1, Д2, Д5 и Д6 заперты, а остальные открыты. Высокий потенциал возникает на шине Р4.

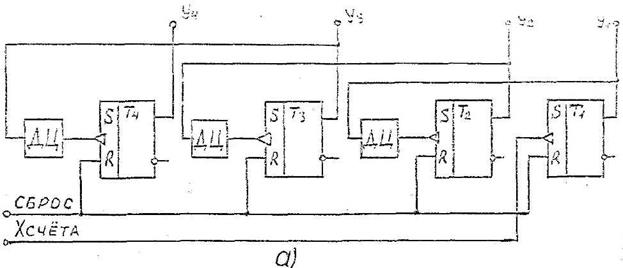

4.Счетчиком называют устройство, предназначенное для подсчета числа входных сигналов. На рисунке 2.5.13 приведена упрощенная схема 4-х разрядного двоичного счетчика и временная диаграмма его работы

Счетчик состоит из 4-х триггеров. Прямой выход триггера через дифференцирующую цепь ДЦ подключен к счетному входу последующего. Примененные триггеры переводятся из одного состояния в другое импульсами только отрицательной полярности. Записанное в счетчике число снимается с прямых выходов триггеров в параллельном коде. Начальное состояние триггеров нулевое, в которое они приводятся импульсом сброса. При подаче на вход счетчика первого импульса счета триггер Т1 переходит в состояние «1» и на его прямом выходе получается положительный перепад напряжения. Положительный импульс на выходе ДЦ не переводит Т2 в единичное состояние. Второй импульс счета на входе Т1 переводит триггер в состояние 0 и на выходе дифференциальной цепи формируется отрицательный импульс, который переводит триггер Т2 в состояние 1. Таким образом, отрицательный импульс переноса в ячейку старшего разряда двоичного счетчика появляется тогда, когда триггер ячейки младшего разряда переходит из состояния 1 в состояние 0. это соответствует правилу сложения двоичных чисел 1 + 1, дает нуль в данном разряде и единицу переноса в старший разряд.

Следует отметить, что такие счетчики могут быть использованы и как делители частоты с коэффициентом переноса 2n , где n – число разрядов. По аналогичной схеме строятся вычитающие счетчики. В отличии от суммирующих импульс переноса в старший разряд формируется при переходе младшего разряда из состояния 0 в состояние 1.

|

|

|

|

ИСПОЛНИТЕЛЬНЫЕ МЕХАНИЗМЫ

Дата добавления: 2019-02-22; просмотров: 459; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!