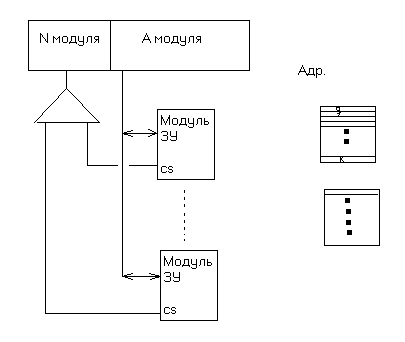

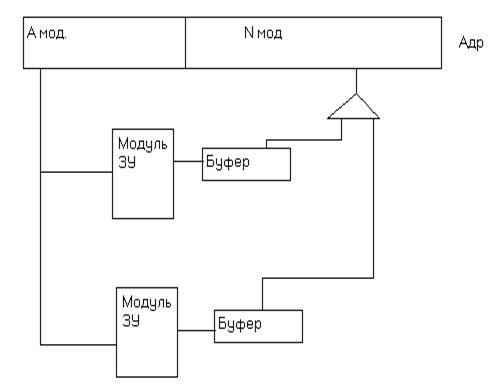

Память с расслоением обращений.

Память с расслоением

Наличие в системе множества микросхем памяти позволяет использовать потенциальный параллелизм, заложенный в такой организации. Для этого микросхемы памяти часто объединяются в банки или модули, содержащие фиксированное число слов, причем только к одному из этих слов банка возможно обращение в каждый момент времени. Как уже отмечалось, в реальных системах имеющаяся скорость доступа к таким банкам памяти редко оказывается достаточной . Следовательно, чтобы получить большую скорость доступа, нужно осуществлять одновременный доступ ко многим банкам памяти. Одна из общих методик, используемых для этого, называется расслоением памяти. При расслоении банки памяти обычно упорядочиваются так, чтобы N последовательных адресов памяти i, i+1, i+2, ..., i+ N-1 приходились на N различных банков. В i-том банке памяти находятся только слова, адреса которых имеют вид kN + i (где 0 ( k ( M-1, а M число слов в одном банке). Можно достичь в N раз большей скорости доступа к памяти в целом, чем у отдельного ее банка, если обеспечить при каждом доступе обращение к данным в каждом из банков. Имеются разные способы реализации таких расслоенных структур. Большинство из них напоминают конвейеры, обеспечивающие рассылку адресов в различные банки и мультиплексирующие поступающие из банков данные. Таким образом, степень или коэффициент расслоения определяют распределение адресов по банкам памяти. Такие системы оптимизируют обращения по последовательным адресам памяти, что является характерным при подкачке информации в кэш-память при чтении, а также при записи, в случае использования кэш-памятью механизмов обратного копирования. Однако, если требуется доступ к непоследовательно расположенным словам памяти, производительность расслоенной памяти может значительно снижаться.

|

|

|

Обобщением идеи расслоения памяти является возможность реализации нескольких независимых обращений, когда несколько контроллеров памяти позволяют банкам памяти (или группам расслоенных банков памяти) работать независимо.

Организация ассоциативной памяти.

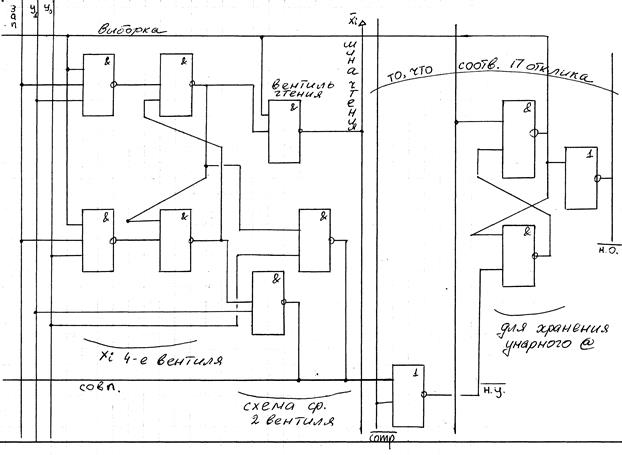

В этой памяти каждая ячейка отыскивается не по ее номеру или адресу, а по ее содержанию, т.е. по той информации которая в этой ячейке находится, по ассоциации. Поскольку поиск требуемого содержания ведется параллельно по всем разрядам ячеек ЗМ, то эта память является более быстродействующей, чем адресная. Считывание в данной памяти осуществляется без разрушения.

Ш вх.

a0 a1 a2

|

|

|

Ш вых.

Рг АП – регистр ассоциативного признака.

Рг КМ – регистр кода маски

КС - комбинационная схема

Рг СВ – регистр совпадений

ФС - формирующая схема.

Общей частью операций чтения и записи в данной памяти является операция контроля ассоциаций, которая может иметь и самостоятельное значение. ЗМ (запоминающий массив) состоит из N n+1 разрядных ячеек памяти. n+1 разряд - служебный. Если там содержится 1 то ячейка памяти занята, если 0 – то ячейка памяти свободна. Для осуществления операции контроля ассоциаций в Рг АП заносится n- разрядный ассоциативный признак (n+1 разряд свободен). В Рг КМ заносится n разрядный код маски, причем 1 в те разряды Рг КМ, по которым в ячейках ЗМ проводися ассоциативный поиск, так называемые незамаскированные разряды. Если в РгКм в каком-либо разряде стоит 0, то это замаскированный разряд, по таким разрядам поиск в ячейках ЗМ не производится. По содержимому Рг АП и Рг КМ в ячейках ЗМ осуществляется ассоциативный поиск. КС по результатам ассоциативного поиска в Рг СВ формирует содержимое, проставляет 1 в тех разрядах номер которой совпадает с номером ячейки П, где имеется ассоциативный признак, т.е. каждый разряд регистра совпадений отвечает за содержимое той ячейки памяти, номер которой совпадает с номером соответствующей ячейки памяти. По содержимому Рг СВ ФС вырабатывает унитарное 3-х разрядное слово a0a1a2. Если а0=1 (100) в ЗМ нет ни оной ячейки содержащей ассоциативный признак, если а1=1 (010) в ЗМ есть она ячейка содержащая ассоциативный признак, если а2=1 (001) в ЗМ две или более ячейки содержат ассоциативный признак. Для выполнения операции считывания сначала выполняется операция контроля ассоциации. Если а0=1 , то считывание отменяется, если а1=1, то информация из этой единственной ячейки ЗМ считывается в РгИ, если а2=1, то информация считывается из ячейки с наименьшим номером. Для осуществления операции запись сначала выполняется операция контроля ассоциации. Ассоциативный признак n+1 разрядный. В n+1 разряд 0 , а все остальные разряды 1, в Рг КМ n+1 разрядный все n разрядов 0, n+1 разряд 1. По содержимому регистра совпадений формируется 3-х разрядное слово. Если а0=0, то запись отменяется, т.к. в ЗМ нет ни одной свободной ячейки памяти. Если а1=1, запись производится в эту единственную свободную ячейку памяти. Если а2=1, то запись производится в свободную ячейку с наименьшим номером.

|

|

|

Схема одного разряда одной ячейки ассоциативной памяти + схема одного разряда памяти отклика.

|

|

|

поразрядное сравнение. x – слово, которое хранится; y – слово, которое поступает на сравнение.

Совпадение=

Не совпадение=

Достаточно несовпадения в одном разряде.

| yi | not(yi) | значение |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 0 | 0 | исключение разряда из сравнения |

| 1 | 1 | запрещенная комбинация |

сигнал выборки – это адресная шина

н.о. – наличие отклика (наличие совпаления).

самая нижняя горизонтальная линия никакого отношения к рисунку не имеет.

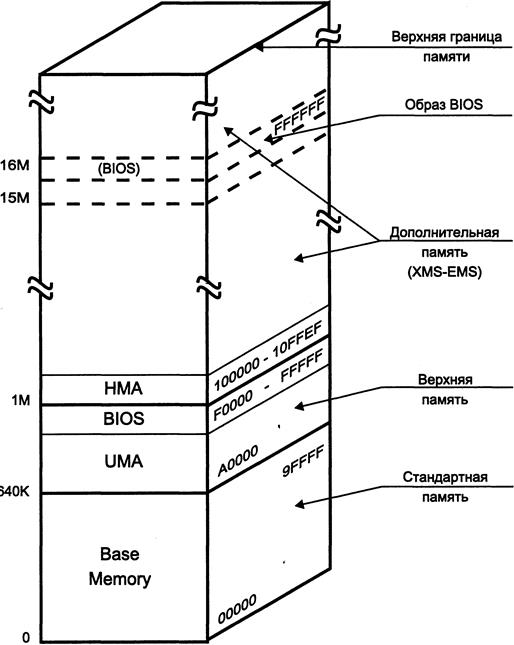

Распределение памяти

Логическая структура памяти PC обусловлена особенностями системы адресации процессоров семейства х86. Процессоры 8086/88, применявшиеся в первых моделях PC, имели доступное адресное пространство 1 Мбайт (20 бит шины адреса). Эти процессоры использовали сегментную модель памяти, унаследованную и старшими моделями в реальном режиме. Согласно этой модели, исполнительный (линейный) адрес вычисляется по формуле Addr=Segxl6+Offset, где Seg и Offset — содержимое сегментного и адресного регистров. Таким образом, обеспечивался доступ к адресному пространству Addr==00000-FFFFFh при помощи 16-битных регистров. Заметим, что при Seg=FFFFh и Offset=FFFFh данная формула дает адрес lOFFEFh, но ввиду 20-битного ограничения на шину адреса эта комбинация в физической памяти указывает на OOFFEFh. Таким образом, адресное пространство как бы сворачивается в кольцо с небольшим «нахлес-том». Начиная с процессора 80286 шина адреса была расширена до 24 бит, а впоследствии (386DX, 486 и старше) до 32 и даже 36 (Pentium Pro и Pentium II). В реальном режиме процессора, используемом в DOS, применяется та же сегментная модель памяти и формально доступен лишь 1 Мбайт памяти, что является недостаточным для большинства современных приложений. Однако выяснилось, что процессоры 80286 в реальном режиме эмулируют 8086 с ошибкой: та самая единица в бите А20, которая отбрасывалась в процессорах 8086/88, теперь попадает на шину адреса, и в результате максимально доступный линейный адрес в реальном режиме достиг lOFFEFh. За эту ошибку с радостью ухватились разработчики PC, поскольку дополнительные (64К-16) байты оперативной памяти, адресуемой в реальном режиме, оказались подарком, позволяющим освободить дефицитное пространство оперативной памяти для прикладных программ. В эту область (lOOOOOh- lOFFEFh), названную «высокой памятью» — High Memory Area (НМА), стали помещать часть операционной системы и небольшие резидентные программы. Однако для обеспечения полной совместимости с процессором 8086/88 в схему PC ввели вентиль линии А20 шины адреса — GateA20, который либо пропускает сигнал от процессора, либо принудительно обнуляет линию А20 системной шины адреса. Более старшие биты такой «заботы» не требуют, поскольку переполнение при суммировании 16-битных компонентов адреса по данной схеме до них не распространяется. Управление этим вентилем подключили к свободному программно-управляемому выходному биту 1 контроллера клавиатуры 8042, ставшего стандартным элементом архитектуры PC, начиная с AT. Предполагалось, что этим вентилем часто пользоваться не придется. Однако жизнь внесла свои поправки, и оказалось, что переключение вентиля в многозадачных ОС, часто переключающих процессор между защищенным, реальным режимом и V86 контроллером клавиатуры, выполняется слишком медленно. Так появились альтернативные методы быстрого переключения вентиля, специфичные для различных реализации системных плат (например, через порт 92h). Кроме того, иногда использовали и аппаратную логику быстрого декодирования команды на переключение бита, поступающую к контроллеру клавиатуры. Для определения способа переключения в утилиту Setup ввели соответствующие опции, позволяющие выбрать между стандартным, но медленным способом и менее стандартизованным, но быстрым в зависимости от используемого ПО.

Поскольку ошибка эмуляции 8086 была радостно принята и широко использована, ее повторили и в 386, и в других старших моделях. А для упрощения внешних схем в процессоры, начиная с 486, ввели и вентиль GateA20 с соответствующим внешним управляющим выводом.

Основную часть адресного пространства занимает оперативная память. Объем установленной памяти определяется тестом POST при начальном включении (перезагрузке) компьютера, начиная с младших адресов. Натолкнувшись на отсутствие памяти (ошибку), тест останавливается на достигнутом и сообщает системе объем реально работающей памяти.

Рис. 1. Распределение памяти PC

Распределение памяти PC, непосредственно адресуемой процессором, приведено на рис.1 и представляется следующим образом:

* OOOOOh-QFFFFh — Conventional (Base) Memory, 640 Кбайт — стандартная (базовая) память, доступная DOS и программам реального режима. В некоторых системах с видеоадаптером MDA верхняя граница сдвигается к AFFFFh (704 Кбайт). Иногда верхние 128 Кбайт стандартной памяти (область 80000h-9FFFFh) называют Extended Conventional Memory.

* AOOOOh-FFFFFh - Upper Memory Area (UMA), 384 Кбайт - верхняя память, зарезервированная для системных нужд. В ней размещаются области буферной памяти адаптеров (например, видеопамять) и постоянная память (BIOS с расширениями). Эта область, обычно используемая не в полном объеме, ставит непреодолимый архитектурный барьер на пути непрерывной (нефрагментированной) памяти, о которой мечтают программисты.

* Память выше 100000h — Extended Memory — дополнительная (расширенная) память, непосредственно доступная только в защищенном режиме для компьютеров с процессорами 286 и старше. В ней выделяется область lOOOOOh-lOFFEFh (высокая память, НМА) — единственная область расширенной памяти, доступная 286+ в реальном режиме при открытом вентиле Gate A20. Эту область драйвер HIMEM.SYS делает доступной для размещения ядра DOS с целью экономии стандартной памяти. На некоторых некачественных 386 системах DOS 6.x эту область может использовать лишь частично (хотя DOS 5.x работает нормально).

Для компьютеров класса AT с 24-битной шиной адреса верхняя граница дополнительной памяти — FDFFFFh (максимальный размер 14,9 Мбайт). Область FEOOOOh-FFFFFFh содержит ПЗУ BIOS (ROM BIOS Area), обращение к этой области эквивалентно обращению к ROM BIOS по адресам OEOOOOh-OFFFFFh.

Для 386+ процессоров и 32-битной шины адреса теоретическая верхняя граница — 4 Гбайт, а для Pentium Pro и Pentium II—64 Гбайт (36-битная шина адреса). В компьютерах с 32-разрядной шиной адреса образ BIOS дополнительно проецируется в адреса FFFEOOOOh-FFFFFFFFh. Однако иногда используется и проекция BIOS в область FEOOOOh-FFFFFFh, что не позволяет использовать более 16 Мбайт ОЗУ, поскольку система воспринимает только найденную непрерывную область расширенной оперативной памяти. Если 32-разрядный компьютер имеет отображение области BIOS под границей 16 Мбайт, это отображение обычно можно запретить соответствующей опцией BIOS Setup. Иногда для использования специфических адаптеров ISA, имеющих буфер с адресами в 16-м мегабайте памяти, предусматривают опцию Memory Hole At 15-16M. Ее разрешение также не позволяет использовать оперативную память свыше 16 Мбайт.

Реально современные системные платы позволяют установить до 128-512 Мбайт ОЗУ, для мощных серверных платформ и это не предел. Обращение по адресам, превышающим границу установленной оперативной памяти (или максимально возможного объема), транслируется на шину PCI, которая имеет 32-битную адресацию.

Компьютеры, использующие режим системного управления SMM (System Management Mode), имеющийся у большинства процессоров последних поколений, имеют еще одно адресное пространство памяти — SMRAM. Это адресное пространство «параллельно» пространству обычной памяти и при работе доступно процессору только в режиме обработки SMI. Память SMRAM может представлять собой часть физической оперативной памяти (DRAM), а может быть реализована и специальной микросхемой энергонезависимой памяти. Ее размер может варьироваться в диапазоне от 32 Кбайт (минимальные потребности SMM) до 4 Гбайт. SMRAM располагается, начиная с адреса SMIBASE (по умолчанию ЗООООЬ), и распределяется относительно адреса SMIBASE следующим образом:

* FEOOh-FFFFh (3FEOOh-3FFFFh) — область сохранения контекста (распределяется, начиная со старших адресов по направлению к младшим). По прерыванию SMI сохраняются практически все регистры процессора, включая программно-невидимые регистры CR1, CR2 и CR4, а также скрытые регистры дескрипторов для CS, DS, ES, FS, GS и SS. Автоматическое сохранение для регистров DR5-DRO, TR7-TR3 и регистров FPU не производится.

* 8000h (38000h) - точка входа в обработчик (SMI Handler). * 0-7FFFh (30000h-37FFFh) - свободная область.

Память SMRAM должна быть схемотехнически защищена от доступа прикладных программ. Процессор генерирует специальный выходной сигнал SMIACTff во время обработки SMI, который и должен являться «ключом» доступа к этой памяти. Если SMRAM не является энергонезависимой, то системная логика должна обеспечить возможность ее инициализации (записи программного кода обработчика) процессором из обычного режима работы до разрешения появления сигнала SMIft.

Дата добавления: 2018-10-26; просмотров: 660; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!