Сегментная организация памяти в микропроцессорах i8086/88 и в реальном режиме работы микропроцессоров x86.

В микропроцессорах i8086/88 сегментация памяти осуществляется простым способом. Все адресное пространство в 1 Мбайт разбивается на несколько (от 16 до 65536) смежных блоков памяти. Каждый такой блок может иметь размер от 16 байт до 64 Кбайт и выравнивается на шестнадцатибайтной границе. Блок памяти длиной в 16 байт и выравненный на 16-ти байтной границе называется параграфом. Для обращения к любому адресу в памяти необходимо знать его физический адрес, который в микропроцессорах i8086/88 и реальном режиме работы микропроцессоров x86 совпадает с его линейным адресом.

В общем случае для формирования линейного адреса необходимо знать базу (Base, Segment) и смещение (Offset) этого адреса. В микропроцессорах i8086/88 оба компонента линейного адреса являются шестнадцатиричными.

Для микропроцессоров x86 в реальном режиме работы смещение (Offset) является одновременно эффективным адресом. Эффективные адреса формируются в Intel-совместимых микропроцессорах с помощью регистров данных (смотри VOLIII(6), "Системные регистры центрального процессора".) Эффективный адрес формируется следующим образом.: к восьми или шестнадцатиразрядному смещению в программе добавляется 16-ти разрядное содержимое базового регистра и 16-ти разрядное содержимое индексного регистра. (смотри VOLIII(6) "Классификация регистров данных").

Примечания: 1. Разрядность смещения должна соответствовать разрядности регистра, куда пересылаются данные.

|

|

|

2. Обычно в базовом регистре содержится начальный адрес блока извлекаемых данных, а в индексном регистре -- длина извлекаемой записи, умноженная на порядковый номер (от 0 до N-1) записи.

Система команд в микропроцессорах x86 устроена так, что для образования эффективного адреса необходимо обязательное присутствие только одного его компонента. Таким образом любой компонент: база, индекс, смещение -- или даже оба из них могут быть опущены.

Примечание: Необходимые сочетания индексных, базовых регистров и разрядности смещения не произвольны, а резервируются фирмой Intel в своих разработках.

Базовые адреса и формирование линейных адресов.

Базовые адреса содержатся в сегментных регистрах микропроцессоров i8086/88 и в регистрах селекторов сегментов в микропроцессорах x86 (смотри VOLIII(6), "Классификация регистров для сегментации и страничной организации памяти".) Эти регистры шестнадцатиразрядные. Однако образующийся в результате сложения базового и эффективного адреса линейный адрес является 20-ти разрядным.

Базовые адреса выравнены на границах параграфа. Поэтому трансляция линейного адреса в физический не вызывает проблем.

Примечание: Это справедливо для микропроцессоров i8086/88. В защищенном режиме работы микропроцессоров значение в сегментном регистре не имеет прямой взаимосвязи с реальным адресом в памяти. Кроме того, само понятие "параграф" там не используется.

|

|

|

Следует отметить, что в микропроцессоре i8086 максимальное значение физического адреса составляет FFFFFh (или 1Мбайт - 1 байт). Однако величина максимального значения линейного адреса (сумма максимальных значений базового и эффективного адресов) равна:

Таким образом максимальный линейный адрес имеет размер 1,062 Мбайт (то есть на 64 Кбайт больше, чем адресное пространство в 1 Мбайт). Поэтому в микропроцессорах i8086/88 происходит "заворачивание" адреса вокруг границы сегмента. (то есть физический адрес (формула E.1.) будет иметь значение 0FFEFh). В микропроцессоре i80286, в резульате ошибки разработчиков, такого заворачивания нет (смотри раздел Верхняя память). В микропроцессорах i80386 и выше это "заворачивание" можно включить, а можно и выключить, Для включения "заворачивания" необходима аппаратная блокировка линии A20 (A20=0) с помощью порта контроллера клавиатуры. Его состоянием можно управлять программно.

Особенности сегментации памяти в микропроцессоре i8086 (итоги).

|

|

|

1. Сегменты памяти определяются только сегментными регистрами.

2. Начальный адрес сегмента связан с физическим адресом параграфа.

3. Никаких средств правильности использования сегментов нет.

4. Размещение сегментов в памяти достаточно произвольно. Ограничение - только выравнивание на границе параграфа.

5. Сегменты могут частично или полностью перекрываться, или не иметь общих частей.

6. Программа может обращаться к любому сегменту как для считывания, так и для записи данных и команд.

7. Для защиты памяти от несанкционированного доступа других программ требуются специальные "внешние" схемы.

8. Система не делает различий между сегментами данных, кода и стека.

9. Нет никаких препятсятвий для обращения к физически не существующей памяти.

10. При обращении к несуществующей памяти результат непредсказуем (все зависит от разработчика материнской платы и другого аппаратного обеспечения компьютера.)

11. Длина сегмента равна целому числу параграфов.

Общепринятая в настоящее время концепция виртуальной памяти появилась достаточно давно. Она позволила решить целый ряд актуальных вопросов организации вычислений. Прежде всего к числу таких вопросов относится обеспечение надежного функционирования мультипрограммных систем.

|

|

|

В любой момент времени компьютер выполняет множество процессов или задач, каждая из которых располагает своим адресным пространством. Было бы слишком накладно отдавать всю физическую память какой-то одной задаче тем более, что многие задачи реально используют только небольшую часть своего адресного пространства. Поэтому необходим механизм разделения небольшой физической памяти между различными задачами. Виртуальная память является одним из способов реализации такой возможности. Она делит физическую память на блоки и распределяет их между различными задачами. При этом она предусматривает также некоторую схему защиты, которая ограничивает задачу теми блоками, которые ей принадлежат. Большинство типов виртуальной памяти сокращают также время начального запуска программы на процессоре, поскольку не весь программный код и данные требуются ей в физической памяти, чтобы начать выполнение.

Другой вопрос, тесно связанный с реализацией концепции виртуальной памяти, касается организации вычислений на компьютере задач очень большого объема. Если программа становилась слишком большой для физической памяти, часть ее необходимо было хранить во внешней памяти (на диске) и задача приспособить ее для решения на компьютере ложилась на программиста. Программисты делили программы на части и затем определяли те из них, которые можно было бы выполнять независимо, организуя оверлейные структуры, которые загружались в основную память и выгружались из нее под управлением программы пользователя. Программист должен был следить за тем, чтобы программа не обращалась вне отведенного ей пространства физической памяти. Виртуальная память освободила программистов от этого бремени. Она автоматически управляет двумя уровнями иерархии памяти: основной памятью и внешней (дисковой) памятью.

Кроме того, виртуальная память упрощает также загрузку программ, обеспечивая механизм автоматического перемещения программ, позволяющий выполнять одну и ту же программу в произвольном месте физической памяти.

Системы виртуальной памяти можно разделить на два класса: системы с фиксированным размером блоков, называемых страницами, и системы с переменным размером блоков, называемых сегментами.

Быстрое замещение фрагментов данных. Ассоциативная память образца 1956 года.

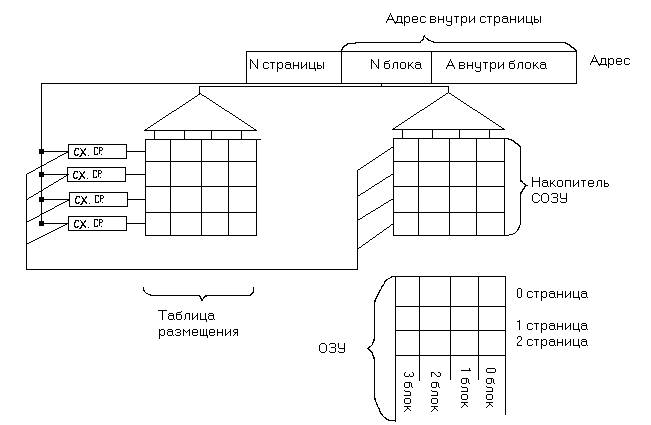

Страница разбивается на блоки. СОП тоже делится на страницы. Замещение идет строго по блокам, к.е. 0 блок может попасть только в 0 блок. Номер блока внутри страницы однозначно определяется дешифратором. Номера страниц из которых выбираются нужные нам блоки записаны в таблицу размещений.

1. вариант –КЭШ для программ (впервые Motorola).

2. вариант – КЭШ отдельно для программ и отдельно для данных (впервые Intel).

3. вариант – КЭШ второго уровня (все страницы растягиваем в одну цепочку).

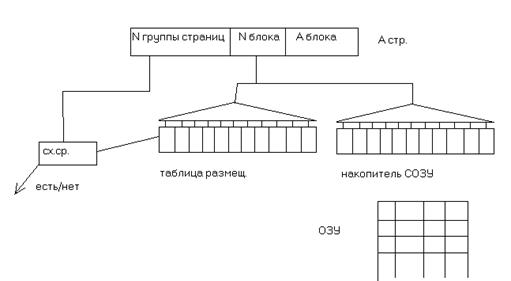

А стр. – старый адрес страницы.

схема одностраничного КЭШа большого объема.

Дата добавления: 2018-10-26; просмотров: 513; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!