Трех (6) уровневая модель памяти.

Верхний уровень памяти образуют КЭШ-1 и регистры центрального процессора. КЭШ-2 дополнительная буферная память для диска. В ОП выделен кусок памяти - оперативный буфер дисковой памяти, т.е. буфер для ВУ. КЭШ-2+ОП=ВП. ВП - внешняя память. ВЗУ+ОП(часть)=ГП. ГП – главная память машины. Получили всего три уровня, но каждый состоит из 2-х частей.

|

Верхний уровень всегда сначала обращается в буфер более нижнего уровня. ЦП обращается в КЭШ-2.

Как собрать память большого объема.

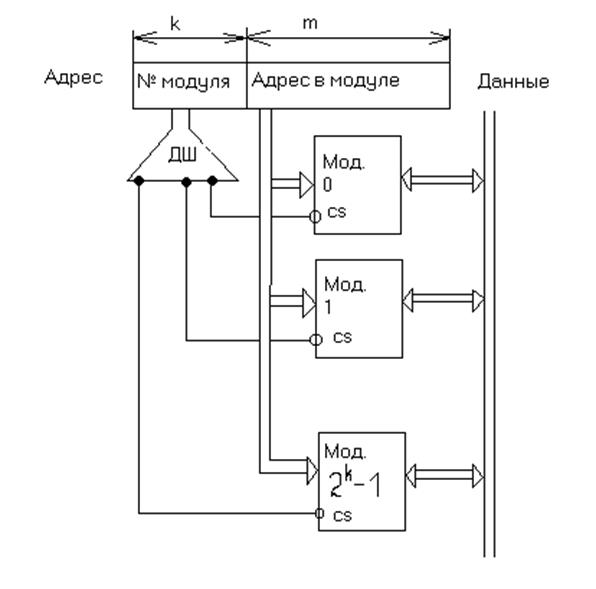

Классическая схема построения ЗУ большого объема, если есть модули памяти малого объема.

cs – chip select – выбор кристалла, разрешение работы.

Данные, чтение либо запись параллельно разводятся на все модули. Выбор кристалла осуществляется старшими разрядами адреса, через дешифратор подаются сигналы на входы cs.

Активное значение сигнала на входе cs не только разрешает работу модулю, но и одновременно открывает и выходные ключи.

oe (output enable) – сигнал на выходе поставляемый на трехстабильный ключ. cs является одновременно сигналом oe.

Организация ОП (основной памяти).

Памяти всегда мало. 2 ситуации.

- короткий адрес ( 16-ти разрядная машина)

- длинный адрес (32-х разрядная машина).

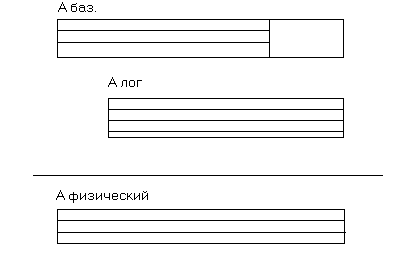

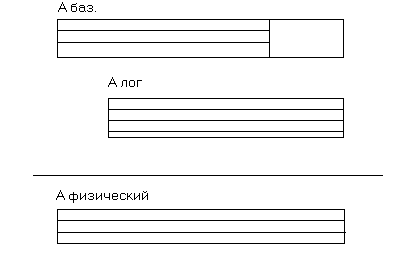

Логический адрес –это тот адрес, который определяется командой при логической адресации. Если логический адрес 16-ти разрядный, то объем

ОЗУ =216=64 Кб.

Физическая память – это память с которой мы реально работаем.

|

|

|

Если адрес физический = 20..24 разряда, получается адрес физический больше адреса логического.

Если адрес логический 32 разряда, то обратная ситуация адрес логический больше адреса физического.

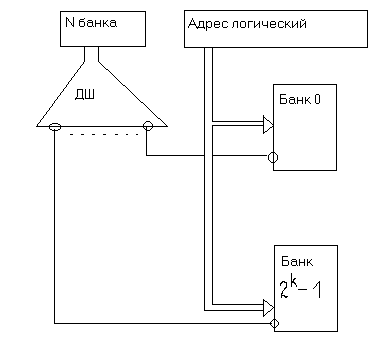

Метод банков.

Физический адрес = номер банка + логический адрес.

V банка = 64Кб. Номер банка записывается в отдельный регистр по отдельной команде. Этот регистр находится не в РЗУ.

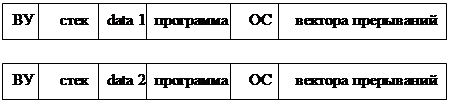

Гипотетическое распределение адресного пространства. Есть один банк памяти.

но места не хватает, т.к. 64 Кб. Заведем 2 банка

|

Для того, чтобы обратиться к data2 мы должны во второй банк поместить помимо data2 все старое из предыдущего банка.

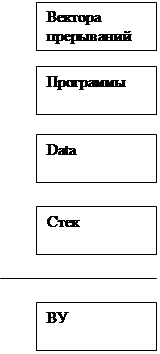

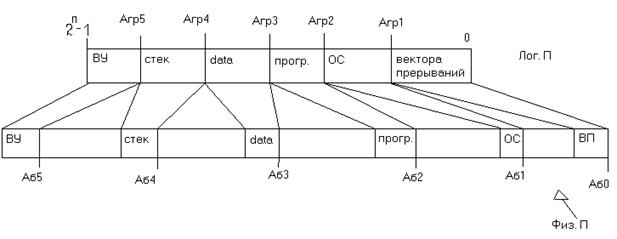

Оказалось, что эта схема плохая, сделали новую. Для каждого типа данных (информации) заводится свое адресное пространство. При этом в какое пространство процессор должен обращаться определяется алгоритмом выполнения команды. Отсюда возникает вопрос, можем ли мы включить счетчик команд в список регистров? Нельзя! => счетчик команд и указатель стека мы исключаем из РОН. Обращение к ВУ выполняется по отдельным командам.

Имеем 5 банков.

по алгоритму выполнения команды мы знаем в какой банк обращаться => мы можем указывать адрес и тип банка. Уже с 64 Кб мы получили суммарный V 64*4=256 Кб.

|

|

|

|

По каждому типу информации заводим несколько банков, следовательно, для каждого типа заведем сой регистр N банка.

Идея базового адреса.

16-ти разрядный базовый адрес в 20-ти разрядах.

Был регистр номер банка, а теперь регистр сегмента .

Сегментный регистр кодовый –cs, данных - ds, стека – ss. Логический адрес становится смещением в сегменте. Базовый адрес хранится в сегментном регистре.

Длинный физический адрес, короткий логический.

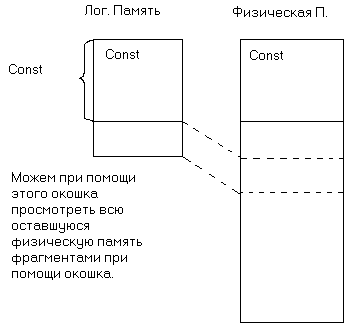

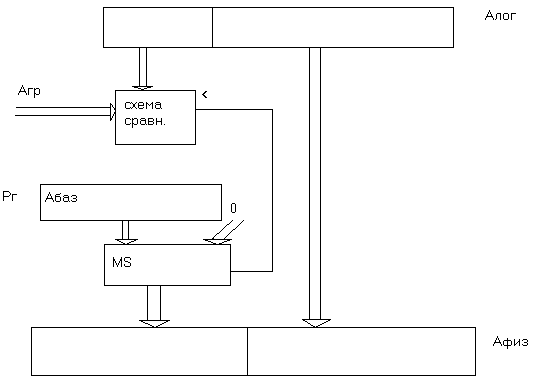

Агр. – адрес гранцы постоянной части.

Эта схема расширенной памяти не связана с логикой работы процессора, поэтому она может находиться где угодно.

Абаз. – базовый адрес окна.

РгАбаз. – рассм. как ВУ.

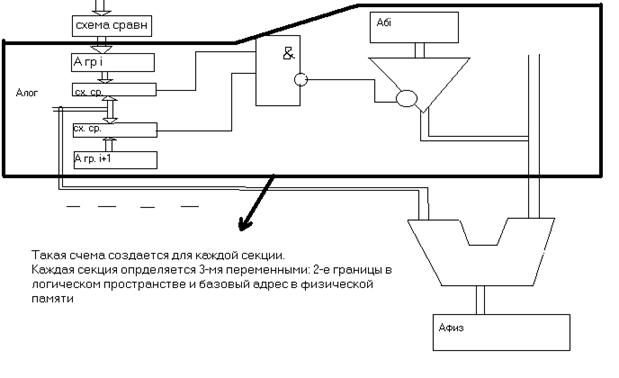

Мы сделали окно только для расширения данных, а если еще каждую секцию памяти определить как окно. Разбиваем логическую память на секции. Каждая секция характеризуется граничными адресами. Будем каждую секцию транслировать в свою область физической памяти.

Схема для трансляции адреса одной секции.

Схема для трансляции адреса одной секции.

Схема диспетчера памяти.

k секций 2k-1 регистров.

k секций 2k-1 регистров.

Зона ВУ не транслируется, ее положение неизменно, это всегда последние адреса как логической, так и физической памяти.

|

|

|

Диспетчер памяти имеет много регистров, их неудобно держать в центральном процессоре. Трансляция адресов ВУ всегда однозначна.

В чистом виде ни метод сегментных регистров ни метод диспетчера памяти не позволяет работать с Памятью большого объема.

В Intel используется подход, который использовался при страничной организации памяти.

чтобы увеличить адрес физический надо увеличить разрядность Абаз, т.е. выйти за пределы слова.

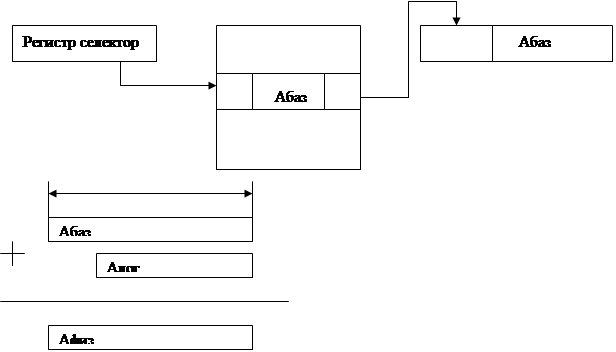

Занести слово двойной длины Абаз в сегментный регистр при дальнем переходе невозможно. А если хранить Абаз в другом месте, а в регистр Абаз хранить косвенный адрес.

Длинные адреса начала секций хранятся в специальном месте памяти, а в сегментном регистре хранятся не прямые значения адреса, а указатель на таблицу базовых адресов.

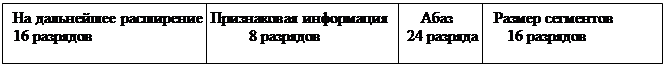

Регистры, связанные с формированием длинного физического адреса.

Рг сегм=Рг селектор (селектор сегмента).

Он программно доступен, 16-ти разрядный. Он не хранит адрес базы в нем смещение для некоторой таблицы. В таблице находятся дескрипторы включающие в себя в том числе и базовые адреса. Строка из таблицы дескрипторов читается в специальный регистр дескриптора и уже Абаз, который хранится в регистре дескриптора используется.

|

|

|

А физический адрес : длинный Абаз

+короткий логический адрес

= длинный физический адрес.

Регистр дескр.

Регистр дескр.

Таблица дескрипторов

24 разряда

Абаз может быть любой длины. Для 16-ти разрядной машины Абаз уже 24 разряда. Мы можем иметь практически нулевой шаг между сегментами.

Как правило пользователь не замечает таблицы. При смене содержимого регистра селектора центральный процессор сам, по собственной микропрограмме залезает в таблицу дескрипторов, выбирает требуемый дескриптор и заносит его в требуемый рг. дескриптор. Так как смена регистра дескриптора делается автоматически на уровне микропроцессора этот регистр оказывается программно недоступен. Следовательно, вся работа дескриптора для пользователя не видна, не нужно тратить ни одной команды, хотя смена сегмента требует большего времени.

Процессор имеет два режима: реальный и защищенный. Реальный – это классический режим с сегментными регистрами. Можно работать с памятью объемом 1Мб. В реальном режиме схема с дескрипторами не работает. В защищенном режиме работает схема с дескрипторами.

При включении процессора – реальный режим, идет формирование таблицы, а затем, по специальной команде идет переход в защищенный режим.

Подробнее:

4 регистра, а к ним добавлены регистры дескрипторы.

сел. дескрипт.

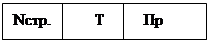

селектор:

содержимое селектора: старшие разряды – это номер строки в таблице дескриптора, Т – признак таблицы дескриптора, машина использует 2-е таблицы дескрипторов, Пр – кодовое слово, называют уровень привилегий.

2 таблицы дескрипторов:

- глобальная;

- локальная.

Глобальная таблица – это системная таблица дескрипторов (общая для всех программ + системная информация).

Локальная таблица – собственная таблица программы.

Полный размер таблицы дескрипторов = 216=64Кб, т.е. ровно одно логическое пространство. Таблица может быть определена как один полный сегмент.

Что хранится в дескрипторе.

В центральном процессоре есть специальный регистр, где хранится начальный адрес глобальной таблицы дескрипторов.

GDT – глобальная таблица дескрипторов.

|

В этой таблице определено все, в том числе и сегмент локальной таблицы дескрипторов. Поэтому для задачи делается короткий 16-ти разрядный регистр, где хранится селектор сегмента локальной таблицы дескрипторов – LDT.

Регистры GDT и LDT программно доступны.

|

| ||||

Как правило обе таблицы находятся в первом мегабайте. -> 16-ти разрядная машина позволяет работать с виртуальной памятью объемом до 1 Гб.

Идея с дескрипторами восходит к идее табличной организации памяти.

Дата добавления: 2018-10-26; просмотров: 405; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!