Организация вычислителя УЧПУ.

Каждый из ОМП обладает аппаратными средствами организации асинхронного обмена с использованием шины управления СМГ. Наряду с МП основным элементом ВЧС является память. В микропроцессорных УЧПУ модули памяти используются для хранения системного ПО, которое заносится на заводе- изготовителе УЧПУ в репрограммимруемую постоянную память (РПЗУ) с возможностью перезаписи и удаления. Для хранения ЧП, констант оборудования и результатов промежуточных вычислений используется статическая оперативная энергонезависимая память (СОЗУ). Данные, хранящиеся в этой памяти, изменяются в ходе эксплуатации устройства с большей или меньшей частотой, однако при плановом или аварийном выключении устройства они должны сохраняться в течении определённого срока, обычно не менее 2004.

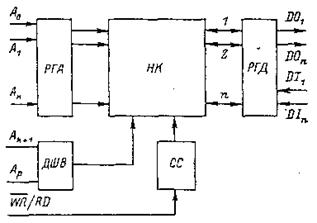

Различают три основных варианта организации модульных ЗУ [30]. В варианте с централизованной дешифрацией ЗУ и входящих в него модулей памяти временная диаграмма выборки ЗУ и работы самого модуля формируются в центральном блоке управления. В варианте с децентрализованной дешифрацией ЗУ в каждом модуле памяти помимо ЗУ имеется дешифратор ДШВ, обеспечивающий выборку нужного модуля путём дешифрации старших разрядов кода адреса Аk+1-Ap (рис. 19)

Рис. 19 Структура модуля памяти с децентрализованной дешифрацией адреса

Рис. 19 Структура модуля памяти с децентрализованной дешифрацией адреса

В этом случае сигналом с выхода дешифратора осуществляется выбор одного из модулей, а младшие адреса с выхода регистра адреса РГА определяют адрес конкретной ячейки в модуле БИС ЗУ. Сигнал «Чтение- запись» WR/RD определяет вид операции с памятью. После его появления на входе схемы согласования СС производится чтение или запись информации в регистр данных РГД.

Арифметические расширители в ВЧС УЧПУ. При решении задач вычисления траекторий и управления приводом требуется выполнение стандартных арифметических операций (умножения, деления, вычисления модуля вектора по его проекциям и некоторых других). Особенно часто выполняется умножение, причем обычно это умножение 32-разрядных слов. К операции умножения предъявляются высокие требования по скорости выполнения, в частности, умножение 16-разрядных слов должно выполняться за 5—10 мкс. Если операция умножения отсутствует в системе команд МП или не удовлетворяет требованию к скорости выполнения, то используют арифметический расширитель умножения, функциональная схема которого приведена на рис. 20

Схема расширителя умножения содержит три адресуемых регистра РГ1, РГ2, РГЗ. Базовый адрес расширителя (старшие разряды кода адреса), общий для этих регистров, поступает с СМГ через приемопередатчик BD1 в регистр селектора адреса СА, стробируется сигналом СИЛ с выхода СУЙ и в качестве разрешающего сигнала поступает на дешифратор. Адресный дешифратор ДШ дешифрует адреса приемников расширителя, задаваемые младшими разрядами кода адреса. Этими приемниками являются регистры множимого РГ1 и множителя РГ2. После передачи множителя в регистр РГ2 этот регистр находится

Рис. 20 Функциональная схема арифметического расширителя умножения

в режиме сдвига логической единицы со сметного входа. Тактовые импульсы (Т И) с внутреннего генератора расширителя поступают на двоичный счетчик, который пылает на регистр мастичного произведения РГ3 16 импульсов, управляющих процессом умножения (на .схеме генератор и счетчик не показаны). При подаче каждого импульса выполняются операции сложения в сумматоре SM результата умножения и суммы ранее вычисленных произведений, поступающей с регистра частичных произведений РГЗ. Последовательность действий в каждом цикле определяется младшим разрядом регистра множителя. Если в разряде установлена 1, то к содержимому РГЗ добавляется множимое из РГ1 и производится сдвиг вправо в регистре РГ1 и РГЗ, в противном случае выполняется только сдвиг;. РГ1 н РГЗ без сложения. Поскольку по мере сдвига множителя вправо старшие разряды регистра множителя РГ2 освобождаются, то он используется для хранения младшей части произведения, которая последовательно поступает с выхода младшего разряда QO регистра РГЗ.

После выполнения описанных действий в 16 тактах работы расширителя в регистре РГЗ находится старшая часть результата, а в регистре РГ2 — младшая. Командами пересылки из .МП результат по СМГ передается в регистры МП через линии А приемопередатчиков BD1, BD2 с использованием сигнала ВЫВ СУЙ, который переводит регистры РГ2, РГЗ в режим параллельной передачи данных.

Третий вариант организации мо-

дульного ЗУ предусматривает, выбор модуля специальным сигналом, подаваемым на- схему управления модулем ЗУ, которая определяет всю временную диаграмму работы модуля. В МПС с асинхронным обменом используется вариант организации памяти с децентрализованной дешифрацией ЗУ. Рассмотрим модуль памяти РПЗУ, использующий ЗУ емкостью 1К слов. Общая емкость адресуемой памяти модуля, упрощенная функциональная схема которого приведена на рис.21(используется восемь таких БИС), равна 4К слов (16-разрядных). Модуль работает в составе ВЧС как пассивное устройство, обеспечивающее

Рис. 21 Функциональная схема модуля памяти РПЗУ

асинхронный обмен данными с МП. Схема управления интерфейсом (СУИ) модуля принимает от МП сигналы SYNC к DIN по управляющей шине СМГ и формирует сигналы управления модулем.: ВВД, СИА и ответный сигнал пассивного устройства RPLY на управляющую шину СМГ.

Сигналом СИА производится фиксация младших разрядов адреса в регистрах адреса РА1, РА2. Три старших разряда адреса пропускают на мультиплексор D8. Если их код совпадает с кодом, набранным перемычками выбора банка ВБ на входах ХО—Х7 мультиплексора D8, то сигнал выбора банка записывается в регистр РА2, с соответствующего выхода которого поступает разрешение на прием сигнала DIN с управляющей шины СМГ. Из сигнала DIN СУИ формирует два сигнала. Сигнал ВВ1 стробирует дешифратор выборки ЗУ D10 и формирует разрешающий сигнал CS на выборку данных из ЗУ. Адрес обращения к самой ЗУ уже сформирован в регистре PA1. Сигнал ВВ2 задержан во времени относительно сигнала ВЫ. Он используется для переключения приемопередатчиков BD по входу УВ из режима приема адреса в режим передачи данных на СМГ с выходов DO выбранной БИС ЗУ.

Работа модуля памяти СОЗУ отличается тем, что при работе с этой памятью возможен как режим чтения, так и режим записи данных, причем возможна адресация как слов, так и байт, записанных в памяти данных. Модули СОЗУ имеют меньшую информационную емкость при тех же габаритах по сравнению с модулями РПЗУ, в то же время необходимо увеличивать объем СОЗУ в микропроцессорных УЧПУ, особенно при работе с управляющими программами большой длины. Также необходимо сокращать длину УП путем использования подпрограмм, полуаналитического программирования, повышения уровня входного языка и других программных средств.( рис 32, б). Биты D6, D5 определяют режим работы порта РА, бит D4- направление передачи данных через порт РА. Биты D2, D1 используются для задания направления передачи и режима работы порта РВ. Порт РС разделён на две четырёхбитовых порта работающих в режиме О с независимым заданием направления передачи битами D3 и D0.

Пример. Все порты работают в режиме 0, РА, РВ-на вывод, PC — на ввод. Управляющее слово имеет вид 10001001 В = 89Н.

БИС допускает поразрядный сброс и установку отдельных разрядов порта PC путем записи в РУС управляющего слова в формате 2 (рис. '3 -. б). Это значит, что порт PC можно рассматривать как совокупность восьми однобитовых портов с независимым управлением.

Какие два последовательных управляющих слова необходимо записать в РУС, чтобы настроить PC на вывод информации и установить на выходе РС4 сигнал логической единицы?

Пользуясь справочником по микропроцессорным комплектам БИС [19], постарайтесь понять, как с помощью рассмотренной БИС организовать межпроцессорный обмен информацией в параллельном коде? Это позволит вам понять принципы сопряжения контроллеров, управляющих приводами, с ЭВМ более высокого уровня управления.

Дата добавления: 2018-04-15; просмотров: 483; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!