ТРИГЕР НА БІПОЛЯРНИХ ТРАНЗИСТОРАХ

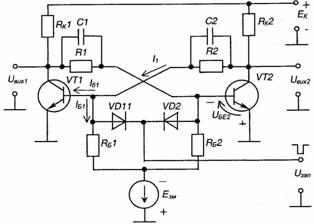

Схема симетричного тригера на БТ зображена на рис.136.

а) б)

Рисунок 136 – Схема симетричного тригера на БТ (а); часові діаграми роботи (б)

Тригер являє собою двокаскадний підсилювач з додатнім зворотним зв'язком, виконаний на біполярних транзисторах VT1 i VT2, увімкнених за схемою зі СЕ.

Додатній зворотний зв'язок забезпечується ланцюжками R1, C1 та R2, C2, які з'єднують колектор одного транзистора з базою іншого.

Напруга Езм призначена для надійного утримання у закритому стані одного з транзисторів схеми.

Коло, до якого входять діоди VD1 i VD2, призначене для запуску тригера при подачі напруги Uзап.

Відмінність в характері зв'язку визначає наступні особливості тригера в порівнянні з мультивібратором: у мультивібраторі розрядка хронірующего конденсатора приводить до зміни потенціалу бази закритого транзистора, до його відмикання і подальшому перекиданню схеми. Ланцюг зв'язку в тригері не містить конденсатора, що розряджається. Тому мимовільного перекидання тригера бути не може – він перемикається під дією зовнішніх імпульсів.

Тригер є симетричним, бо RК1 = RК2 =RК; R1 = R2 =R; С1 = С2 =С; RБ1 = RБ2 =RБ.

Він має два сталих стани:

- VT1 відкритий, VT2 закритий, при цьому Uвих1= 0, Uвих2 = 1;

- VT1 закритий, VT2 відкритий, при цьому Uвих1= 1, Uвих2 = 0.

Після підмикання джерела живлення тригер рівноможливо може опинитися у будь-якому стані і, за відсутності зовнішніх сигналів керування, може знаходитися у сталому стані скільки завгодно часу (але тільки за наявності живлення – енергозалежна пам'ять).

|

|

|

Розглянемо умови, коли VT1 відкритий, а VT2 закритий:

Іб1 = І1 – ІБ1; Іб1 = ЕК/(RК+R) – Езм/ RБ . (1)

Щоб транзистор VT1 знаходився у насиченому стані, необхідно забезпечити:

Іб1 ≥ Ібн ; Ібн = ІКН /β = ЕК/(RК ∙ β), (2)

тобто,

ЕК/(RК+R) – Езм/ RБ ≥ ЕК /(RК ∙ β). (3)

Вираз (3) є визначальним для забезпечення насиченого стану VT1.

Маємо

UБЕ2 = Езм - URБ2; URБ2 = Езм RБ / (RБ+R);

UБЕ2 = Езм - Езм RБ / (RБ+R) < 0. (4)

Період вихідних імпульсів Твих у два рази більший за період запускаючих Тзап (тому такий тригер називають тригером поділювачем на два).

Поряд з лічильним запуском існує роздільний запуск, котрий можна реалізувати двома способами:

- подачею імпульсів однієї полярності від двох різних генераторів на бази кожного з транзисторів у різні моменти часу;

- подачею імпульсів змінної полярності на базу одного з транзисторів.

|

|

|

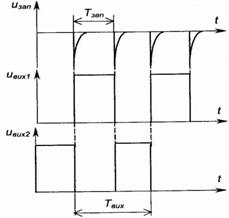

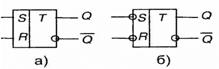

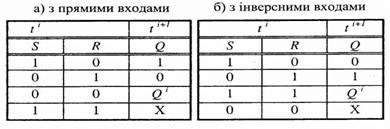

ТРИГЕРИ НА ЛОГІЧНИХ ЕЛЕМЕНТАХ

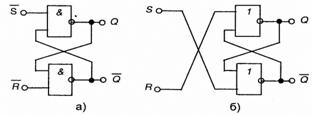

RS – тригер. Умовні позначення асинхронних RS – тригерів з прямими (такими, що реагують на наявність 1) і інверсними (такими, що реагують на наявність 0) входами наведені на рис.137.

Рисунок 137 – Умовні позначення RS – тригера з прямими (а) і інверсними (б) входами

Роботу тригерів описують відповідні таблиці переходів, наведені в табл.1.

Таблиця 14 – Таблиця переходів RS – тригерів

Схеми таких RS–тригерів, побудованих на елементах І-НЕ та АБО–НЕ зображені на рис.138.

Рисунок 138 – RS–тригер з інверсними входами на елементах І-НЕ (а) та з прямими входами на елементах АБО-НЕ (б)

Асинхронні тригери мають найнижчу стійкість проти перешкод тому, що вони переключаються сигналами на інформаційних входах i майже короткочасна зміна вхідних сигналів може переключити тригер в інший стан. Значно більшу стійкість проти перешкод мають синхронні тригери, в яких запис інформації з інформаційних входів відбувається тільки під час дії сигналу дозволу на спеціальному вході синхронізації.

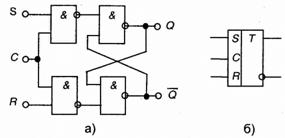

Схема і умовне позначення синхронного RS – тригера з прямими входами, побудованого на елементах І-НЕ, наведені на рис.139.

|

|

|

Рисунок 139 – Синхрнний RS–тригер

Слід зазначити, що тактові входи бувають потенціальні прямі, як у даному випадку (тригер змінює свій стан при надходженні сигналу 1 на вхід С), інверсні (тригер змінює свій стан при надходженні сигналу 0), або імпульсні, також прямі й інверсні (коли тригер змінює свій стан при зміні сигналу на тактовому вході з 0 на 1 або з 1 на 0 відповідно).

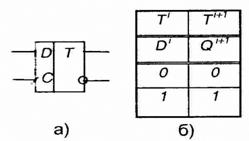

D- тригер (від англійського delay – затримка) має два входи: D- інформаційний та С – тактовий (синхронізуючій): D- тригер синхронний. А це значить, що інформація, яка надходить на вхід D, запам'ятовується лише при надходженні синхронізуючого імпульсу на вхід С, тобто із затримкою на час надходження останнього. Тому D- тригер ще називають тригером затримки.

Умовне позначення D-тригера з прямим імпульсним входом синхронізації та таблиця переходів наведені на рис.107, а часові діаграми його роботи – на рис.140.

Рисунок 140 – Умовне позначення (а) і таблиця переходів (б) D-тригера

Рисунок 141 – Часові діаграми роботи D-тригера

Т-тригер (від англійського to toggle – перекидатись) ще називають тригером поділювачем на два або лічильним тригером. Тригер має тільки один тактовий вхід, а його стан змінюється на протилежний з надходженням на вхід кожного імпульсу. Цей тригер використовують для лічення та ділення частоти імпульсів.

|

|

|

Він може бути побудований з використанням двотактного синхронногоRS–тригера.Т–тригер реалізує функцію виду

,

,

тобто одиничний вхідний сигнал Т повинен міняти стан тригера на протилежний, а нульовий – залишати стан тригера без змін.

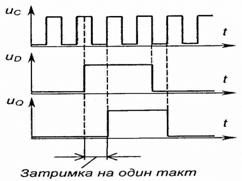

Умовне позначення та часові діаграми роботи Т-тригера з інверсним імпульсним входом наведені на рис.142.

Рисунок 142 - Схеми Т–тригера: а) – схема двотактного несинхронного Т–тригера на основі двотактного RS–тригера; б) – схема синхронного двотактного Т–тригера; в) – умовне графічне позначення двотактного синхронного Т–тригера

Схема двотактного несинхронного Т–тригера, утвореного з RS–тригера, наведена на рис. а. В цій схемі надходження сигналу Т = 1 на вхід С призводить до запису в двотактний RS–тригер стану, протилежного попередньому. Сигнал на виході тригера зміниться тільки після завершення дії сигналу Т = 1, що виключає виникнення генерації в схемі із зворотнім зв’язком.

На рис. б представлена схема синхронного двотактного Т–тригера, а на рис. в – його умовне позначення. Одиничний вхідний сигнал Т уявляється високою напругою при С = 1. Запис інформації в тригер здійснюється при С = 1, причому зміна стану, як звичайно в двотактних тригерах, відбувається після закінчення дії імпульсу синхронізації С = 1. При Т = 1 стан тригера змінюється на протилежний, а при Т = 0 – не змінюється.

Часова діаграма роботи Т–тригера наведена на рис.143.

Рисунок 143 - Часова діаграма роботи Т–тригера

Як видно з часової діаграми Т–тригер можна використовувати як асинхронний тригер з лічильним входом, якщо на інформаційний вхід Т подати константу 1, а логічну змінну подавати на вхід С.

Синхронні і асинхронні тригери з лічильним входом застосовуються в цифрових пристроях і мікропроцесорних системах для побудови схем лічильників.

Розповсюдженим типом тригера в системах інтегральних логічних елементів є універсальний двотактний JK–тригер (рис.144)а) – схемна реалізація; б) – умовне позначення:

Рисунок 144 - JK–тригер: а) – схемна реалізація; б) – умовне позначення

Входи J і K відповідають входам S і R RS–тригера, тобто сигнал 1 на вході J встановлює тригер в стан 1, а сигнал 1 на вході K встановлює його в стан 0 незалежно від попереднього стану. Але на відміну від RS–тригера в JK–тригері сигнали 1 можуть одночасно прийти на входи J і K. При цьому стан тригера завжди буде змінюватись на протилежний, тобто при J = K = 1 схема поводить себе як Т–тригер з лічильним входом. Сигнали J і K можуть бути результатом кон’юнкції кількох сигналів J = J1 Ù J2 Ù J3 і K = K1 Ù K2 Ù K3. Крім того тригер має входи несинхронізованого встановлення  і

і  , за допомогою яких при С = 0 тригер можна встановити в стан 1 через подачу сигналів

, за допомогою яких при С = 0 тригер можна встановити в стан 1 через подачу сигналів  = 1,

= 1,  = 0 або в стан 0 через подачу сигналів

= 0 або в стан 0 через подачу сигналів  = 0,

= 0,  = 1.

= 1.

Функцію переходів JK–тригера Q(t + 1) можна представити у вигляді булевих функцій від змінних, що відповідають попередньому стану t і вхідним сигналам тригера при  =

=  =1 (тобто сигнали на несинхронізованих входах не впливають на стан тригера):

=1 (тобто сигнали на несинхронізованих входах не впливають на стан тригера):

Функціонування JK–тригера може бути описано таблицею переходів. Наводиться таблиця переходів (таблиця 2) при  =

=  =1 під дією синхронізованих входів (С = 1).

=1 під дією синхронізованих входів (С = 1).

Таблиця 2 - Таблиця переходів JK–тригера

| t | t + 1 | Коментар | |

| J | K | Q | |

| 0 | 0 | Q(t) | Зберігання 0 або 1 |

| 0 | 1 | 0 | Встановлення 1 |

| 1 | 0 | 1 | Встановлення 0 |

| 1 | 1 | `

| Інверсія стану |

JK–тригер (рис.145) зручний тим, що при різних варіантах підключення його входів можна отримати схеми, що функціонують як D–, T– і RS–тригери.

Рисунок 145 - Схеми варіантів включення універсального JK–тригера: а) – як D–тригер; б), в) – як Т–тригер; г) – як RS–тригер

Дата добавления: 2018-04-05; просмотров: 1060; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!