ОСНОВНІ ПАРАМЕТРИ ІМС. ТИПИ ЛОГІК

До основних параметрів ІМС відносяться:

- коефіцієнт об’єднання за входом Коб визначає кількість входів елементу, призначених для подачі логічних змінних;

- коефіцієнт розгалуження за виходом Кроз визначає кількість входів аналогічних елементів, яку можна підключити до виходу даного елементу. Чим вище Кроз елементу, тим менша кількість елементів може знадобитися при побудові цифрового пристрою;

- швидкодія логічних елементів визначається часом затримки розповсюдження сигналу від входу до виходу елемента;

- завадостійкість визначається максимальним значенням напруги завади, що не порушує роботи елементу;

- потужність споживання Рсп, мВт.

За типами реалізації базових елементів електронних перемикачів існують такі схеми:

- резистивно-діодна логіка РДЛ,

- резистивно-транзисторна логіка РТЛ,

- транзисторно-транзисторна логіка (ТТЛ) -І-НЕ;

- емітерно-зв’язана логіка (ЕЗЛ) - АБО; АБО-НЕ;

- інжекційна інтегральна логіка (І2Л) - І-НЕ, АБО-НЕ;

- структури метал-оксид-напівпровідник p-типу та n-типу (МОН) - І-НЕ; АБО-НЕ;

- комплементарні МОН-структури (КМОН) - І-НЕ, АБО-НЕ.

У цифрових пристроях логічному нулю (лог.0) і логічній одиниці (лог.1) відповідає напруга визначеного рівня (або форми). Найбільше використовується два способи фізичного представлення лог.0 і лог.1: потенціний і імпульсний.

При потенційній формі (рис.125, а і б) використовується напруга двох рівнів: високий рівень відповідає лог.1 (рівень лог.1) і низький рівень – рівень лог.0 – це називається позитивною логікою. Дуже рідко використовують негативну логіку, при якій логічній одиниці ставлять низький рівень напруги, а лог.0 – високий. При імпульсній формі лог.1 відповідає наявність імпульсу, логічному 0 – відсутність імпульсу (рис.125,в).

|

|

|

При потенційній формі відповідна сигналу інформація (лог.1 або лог.0) може бути визначена практично в будь-який момент часу, а при імпульсній формі відповідність між рівнем напруги і значенням логічної величини встановлюється у визначені дискретні моменти часу (тактові моменти часу), позначені на рис.125,в цілими числами t=1,2,…

Рисунок 125 – Форма представлення напруги у цифрових пристроях

СХЕМОТЕХНІКА ЛОГІЧНИХ ЕЛЕМЕНТІВ

Логічні елементи базиса І, НЕ, АБО на дискретних компонентах.

Діодний логічний елемент АБО(збірка). Логічний елемент АБО, виконується на діодах, має два і більш входів і один вихід. Елемент працює при потенційному і імпульсному представленні логічних величин.

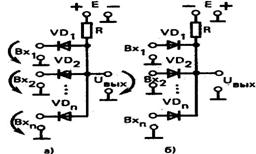

На рис.126,а приведена схема діодного елемента для роботи з потенціалами і імпульсами позитивної полярності. При використанні негативної логіки і негативних потенціалів або імпульсів негативної полярності необхідно змінити полярність включення діодів (рис.126,б).

|

|

|

Розглянемо роботу схеми на рис.65,а. Якщо імпульс (або високий потенціал) діє лише на одному вході, то відкривається підключений до цього входу діод і імпульс (або високий потенціал) передається через відкритий діод на резистор R. При цьому на резисторі утвориться напруга такої полярності, при якій діоди в ланцюгах інших входів виявляються під дією замикаючої напруги.

Рисунок 126 - Схема діодного елемента АБО для роботи с потенціалами і імпульсами: а) позитивної полярності; б) негативної полярності

Якщо сигнали, що відповідають лог.1, одночасно надходять на кілька входів, то при строгій рівності рівнів цих сигналів відкриються всі діоди, підключені до цих входів.

Якщо опір відкритого діода малий в порівнянні з опором резистора R, рівень вихідної напруги буде близький до рівня вхідного сигналу незалежно на скількох входах одночасно діє сигнал лог.1.

Якщо рівні вхідних сигналів відрізняються, то відкривається лише діод того з входів, рівень сигналу на якому має найбільше значення. На резисторі R утвориться напруга, близька до найбільшої з напруг, що діють на входах. Всі інші діоди закриваються, відключаючи від виходу джерела з малим рівнем сигналу.

|

|

|

Таким чином, на виході елемента утвориться сигнал, що відповідає лог.1, якщо хоча би на одному з входів діє лог.1. Елемент реалізує операцію диз′юнкції (операцію АБО).

Діодний елемент І (схема спів падання (збігу). Логічний елемент І має один вихід і два чи більш входів. Діодний елемент працює з інформацією, представленої в потенціній чи в імпульсної формі. На рис.127,а приведена схема, яка використовується при позитивних значеннях вхідних напруг, а для імпульсів негативної полярності рис.127,б.

Рисунок 127 – Схема діодного елемента І: а) при позитивних значеннях вхідних напруг; б) при негативних значеннях вхідних напруг

Нехай на одному з входів ланцюга (рис.127,а) діє низький рівень напруги - лог.0.

Струм буде замикатися в ланцюзі від джерела Е через резистор R, відкритий діод і джерело низької вхідної напруги. Тому що, опір відкритого діода малий, то низький потенціал з входу через відкритий діод буде передаватись на вихід. Діоди, підключені до інших входів, на яких діє високий рівень напруги, закриті. Діюча на діоді напруга UД = uвих - uвх. Таким чином, вихідна напруга, що прикладається до анодів діодів, є для них позитивною, прагнучою відкрити діоди; вхідна напруга, що прикладається до катода, - негативною, прагнучою закрити діод. І якщо uвих < uвх , то UД негативно і діод закритий. Тобто, коли на виході елемента низький потенціал (рівень лог.0), а на вході високий потенціал (рівень лог.1), підключений до цього входу діод закритий.

|

|

|

Таким чином, якщо хоча б на одному з входів діє напруга низького рівня (лог.0) то на виході елемента діє напруга низького рівня (лог.0).

Нехай на усіх входах діє напруга високого рівня (лог.1). Вони можуть трохи відрізнятися за значенням. При цьому буде відкритий той діод, що підключений до входу з більш низькою напругою. Це напруга через діод буде передаватися на вихід. Інші діоди будуть практично закриті. На виході установиться напруга високого рівня (лог.1).

Отже, на виході елемента встановлюється напруга рівня лог.1 у тому випадку, коли на усіх входах діє напруга рівня лог.1. Таким чином елемент виконує логічну операцію І.

Транзисторний елемент НЕ (інвертор).

Операція НЕ може бути реалізована ключовим елементом (рис.128).

Рисунок 128 – Схема транзисторного елемента НЕ (а); його часові діаграми (б)

Цей елемент виконує операцію тільки при потенційній формі представлення логічних величин. При низькому рівні вхідного сигналу, що відповідає лог.0, транзистор закритий, на його виході встановлюється напруга високого рівня Е (лог.1). І навпаки, при високому рівні вхідної напруги (рівні лог.1) транзистор насичений, на його виході встановлюється напруга , близько до нуля (рівня лог.0). Графіки вхідних і вихідних напруг на рис.128,б.

Інтегральні логічні елементи базису І-НЕ і їх параметри.

Інтегральні логічні елементи використовуються при потенційної формі представлення логічних величин.

Елемент І-НЕ діодно-транзисторної логіки (ДТЛ).

Схема інтегрального елемента І-НЕ типа ДТЛ наведена на рис.129.

Рисунок 129 - Схема інтегрального елемента І-НЕ типа ДТЛ

Елемент розіб'ємо на дві послідовно включені функціональні частини. Вхідні величини подаються на діодний логічний елемент І. Друга частина елемента, виконана на транзисторі, яка є інвертором (виконуючий операцію НЕ). Таким чином, в елементі послідовно виконуються логічні операції І і НЕ і, отже , у цілому він реалізує логічну операцію І-НЕ.

Якщо на усіх входах елемента діє напруга високого рівня (лог.1), то на виході першої частини схемы (у точці А) утвориться напруга високого рівня. Ця напруга через діоди VD передається на вхід транзистора, і відкриває його (насичує), на виході елемента напруга низького рівня (лог.0).

Якщо ж хоча б на одному з входів буде діяти напруга низького рівня (лог.0), то в точці А утвориться напруга низького рівня (близького до нуля), транзистор закритий і на виході елемента напруга високого рівня (лог.1). Робота елемента в інтегральному виконанні відрізняеться від роботи такого ж елемента на дискретних компонентах тим, що при одночасній подачі лог.1 на усі входи всі діоди виявляються закритими. Завдяки цьому зменьшується до дуже малого значення споживання струму від джерела, що подає на вхід напругу лог.1.

Елемент І-НЕ транзисторно-транзисторної логіки (ТТЛ) наведена на рис.130.

Рисунок 130 - Елемент І-НЕ транзисторно-транзисторної логіки (ТТЛ)

Основна схема елемента рис.130,а складається з двох послідовно включених функціональних частин: схеми, що виконує операцію І, і схеми інвертора. Особливість схеми І в елементі ТТЛ –один багатоемітерний транзистор БТ, що замінює групу вхідних діодів схеми ДТЛ. Емітерні переходи БТ виконують роль вхідних діодів, а колекторний перехід – роль зміщуючого діода у ланцюзі бази транзистора інвертуючої частини схеми елемента.

Розглянемо принцип роботи БТ. Він складається з окремих транзисторів з об′еднаними базами і колекторами рис.130,б.

Нехай на усі входи елемента подана напруга рівня лог.1 (3,2 В). Емітерні переходи БТ виявляються зміщеними в зворотному напрямку (потенціали емітерів вище потенціалу бази, колекторний перехід БТ, навпаки, зміщений у прямому напрямку (потенціал колектора нижче потенціалу бази). Таким чином, БТ можна представити транзисторами, що працюють в активному режимі з інверсним включенням (у такому включенні емітер і колектор міняються ролями). Базовий струм БТ через колекторний перехід втікає в базу транзистора VT, утримуючи останній у режимі насичення. На виході встановлюється напруга низького рівня (лог.0).

Нехай хоча б на одному з входів діє напруга рівня лог.0.

Потенціал бази БТ вище потенціала емітера і колектора. Отже обидва переходи емітерний і колекторний, зміщені у прямому напрямку і БТ знаходиться у режимі насичення. Весь базовий струм БТ замикається через емітерні переходи. Напруга між колектором і емітером близько до нуля, і діючий на еміторі низький рівень напруги через БТ передається на базу транзистора VT. Транзистор VT закритий, на виході високій рівень напруги (рівень лог.1). при цьому практично весь базовий струм БТ замикається через зміщений в прямому напрямку емітерний перехід БТ.

Логічний елемент емітерно-зв'язаної логіки.

Базовий елемент ЕЗЛ, побудований на основі транзисторного перемикача струму, наведений на рис.131.

Рисунок 131 – Схема ЕЗЛ

Транзистори VTo, VT1, VT2, VT3, працюють у схемі перемикача струму, транзистори VT4, VT5 – у вихідних эмітерних повторювачах.

Нехай на Вх1 подається напруга лог.1. Транзистор VT1 відкритий, эмітерний струм цього транзистора створює на R спадання напруги Ua = лог.1; колекторний струм створює на резисторі Rк1 напругу = лог.0, напруга на колекторі U = Е – URк1 = лог.1. Напруга між базою і эмітером = лог.0, транзистор VTo закритий. Таким чином, відкритий стан кожного з транзисторів VT1, VT2, VT3 приводить до закритого стану транзистора VTo. Струм через резистор Rк2 малий (тече лише базовий струм транзистора VT5) і напруга на колекторі VT0 = лог.1.

Нехай на усіх входах діє напруга лог.0 = 3,5 В. При цьому відкривається транзистор VT0 (з усіх транзисторів, эмітери яких об'еднані відкривається той, на базі якого більш висока напруга). U на базі VTo = 3,9 В.

Uа = U – UБЕ = 3,9-0,7=3,2В, де UБЕ = 0,7 - напруга між базою і эмітером відкритого транзистора; напруга між базою і эмітером транзисторів VT1, VT2, VT3 дорівнює UБЭVT1…VT3 = U° – Uа = 3,5 – 3,2 = 0,3B і ці транзистори закриті. На виході VTo у точці (в) лог.0, на вих.2 VT5 напруга низького рівня лог.0.

З'ясуємо, яка логічна функція формується на виходах елемента.

В точці (в) і на Вих.2 утвориться напруга низького рівня при відкритому транзисторі VTo , тобто , коли х1 = 0, х2 = 0, х3 = 0. При будь-якій іншій комбінації значень вхідних перемінних транзистор VTo закритий і на Вих2 утвориться напруга високого рівня.

Тобто, на Вих.2 формується диз'юнкція змінних х1 V х2 V х3.

На Вих.1 формується функція АБО-НЕ

= х1↓х2↓х3.

= х1↓х2↓х3.

Отже, логічний елемент виконує операції АБО-НЕ і АБО.

Цей елемент відноситься до класу швидкодіючих елементів з високою споживаною потужністю.

Логічні елементи на МДН транзисторах наведено на рис.132.

Рисунок 132 - Логічні елементи на МДН транзисторах: а) схема логічного елемента І-НЕ на однотипних МДН транзисторах з індуктованим каналом n-типу; б) схема елемента АБО-НЕ на однотипних МДН транзисторах з індуктованим каналом n-типу; в) схема елемента АБО-НЕ КМДН-технології

На рис. 132,а показана схема логічного елемента І-НЕ на однотипних МДН транзисторах з індуктованим каналом типу n (n МДН-технологія).

Основні транзистори VT1, VT2 включені послідовно, транзистор VT3 виконує роль навантаження. Якщо на обох входах елемента висока напруга лог.1, оби два транзистори VT1 і VT2 відкриті і на виході встановлюється низька напруга- лог.0. Якщо хоча б на одному вході лог.0 на виході лог.1. На рис.132,б) наведена схема елемента АБО-НЕ.

На його виході встановлюється низька напруга - лог.0, якщо хоча б на одному з входів діє висока напруга- лог.1, що відкриває один з основних транзисторів VT1 чи VT2.

На рис.132,в) наведена схема елемента АБО-НЕ КМДН-технології. У ній транзистори VT1 і VT2 – основні, транзистори VT3 и VT4 – навантажувальні.

Нехай на Вх.1 діє висока напруга- лог.1. При цьому транзистор VT2 відкритий, транзистор VT4 закритий і, незалежно від рівня напруги на іншому вході і стану інших транзисторів на виході встановлюється низька напруга- лог.0. Елемент реалізує операцію АБО-НЕ.

КМДН-схема характеризується дуже малим споживаним струмом (отже і потужності) від джерела живлення.

ДОМАШНЄ ЗАВДАННЯ:

1 Які логічні функції належать до базових?

2 Що таке багатоемітерний транзистор?

3 Побудувати комбінаційний цифровий пристрій за логічною функцією:

а)  ; б)

; б)  ; в)

; в)

4 Який транзистор спеціальної конструкції використовується в І2Л логіці?

5 Яке значення вхідного сигналу буде достатнім для рівня логічної одиниці?

6 Як реалізується живлення основного транзистора інтегральної інжекційної логіки?

7 Які логічні функції можна реалізувати на логіках І2Л та КМДН?

8 Що є особливістю КМДН логіки?

9 В яких межах знаходиться вихідний опір кожного з комплементарних транзисторів в закритому стані?

ВИКЛАДАЧ - Ковальова Т.І.

ЛЕКЦІЯ №36 (2 год.)

ТЕМА 5.5 Тригери

МЕТА:

- навчальна: ознайомити студентів з цифровими пристроямиз пам’яттю;

- розвиваюча: розширити світогляд студентів, поглибити вивчене для систематизації та узагальнення фундаментальних знань щодо тригерів; розвивати вміння самостійно застосовувати знання до вирішення практичних завдань;

- виховна: виховувати увагу, логічне мислення, впевненість у вирішенні практичних завдань:

ОБЛАДНАННЯ: дошка, схеми, таблиці істинності

ПЛАН

1 Характеристика пристроїв з пам’яттю. Класифікація тригерів.

2 Тригер на біполярних транзисторах.

3 Тригери на логічних елементах.

4 Двоступеневі тригери типу M-S.

ЗМІСТ ЛЕКЦІЇ

Дата добавления: 2018-04-05; просмотров: 857; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!