Представление отрицательных чисел. Дополнительный код.

При записи двоичного числа в прямом коде старший разряд является знаковым разрядом. Если его значение равно 0 — то число положительное, если 1 — то отрицательное. В остальных разрядах (которые называются цифровыми разрядами) записывается двоичное представление модуля числа.

При представлении отрицательных чисел, данные сохраняются в форме дополнения. При этом используются две системы. Одна использует дополнение до основания системы счисления (дополнительный код), а вторая — дополнение до основания системы счисления –1 (обратный код). Первым появился обратный код, в котором при представлении отрицательного числа каждая цифра числа вычитается из основания системы счисления минус 1 с целью получения значения дополнения до основания системы счисления –1.

Получим дополнение 8-разрядного двоичного числа 01001100 до значения основания системы счисления минус 1 с целью отображения его как отрицательного значения. Обратите внимание на то, что каждая цифра числа вычитается из единицы для генерирования дополнения до значения основания системы счисления минус 1 (единица). В данном примере отрицательное число

–01001100(2)=–76(10) представляется как 10110011(2). Та же самая методика может применяться для любой системы счисления, но в применении к двоичной системе счисления получение обратного кода может быть достигнуто путем инвертирования каждого двоичного разряда числа.

|

|

|

Сегодня само по себе дополнение до основания системы счисления –1 (обратный код) не используется; оно используется только в качестве этапа на пути к получению дополнения до основания системы счисления. Основная проблема дополнения до основания системы счисления –1 заключается в том, что при использовании этой системы возникают два нуля: положительный (00000000) и отрицательный (11111111); в системе, использующей дополнение до основания системы счисления, существует только положительный ноль.

Таким образом, дополнение до основания системы счисления (дополнительный код) используется для представления отрицательных чисел в современных компьютерных системах.

Для формирования дополнения до основания системы счисления сначала находят дополнение до основания системы счисления –1 (обратный код), а затем добавляют единицу к результату. Пример ниже показывает, как число 01001000(2)=72(10) преобразуется в отрицательное значение переводом его в дополнение до двух (основание системы счисления):

01001000 ® 10110111 ® 10110111 + 1 = 10111000=–72(10)

Чтобы убедиться в том, что 1011 1000 является инверсией (отрицательным значением 0100 1000), сложим их для формирования 8-разрядного результата:

01001000

+ 10111000

100000000

|

|

|

Девятый разряд отбрасывается и результат будет нулем, потому что 01001000 — это положительное 72, в то время как 10111000 — это отрицательное 72 в дополнительном коде. Та же самая методика применима для любой системы счисления.

При использовании дополнительного кода изменяется диапазон представления чисел машинным словом заданной длины.

Еще для представления отрицательных чисел используют так называемый смещенный код. Для его получения прибавляют к числу в обычном дополнительном коде половину диапазона, для байта — это 12810. Такое преобразование эквивалентно инверсии старшего (знакового) разряда, при этом положительные числа имеют десятичный эквивалент от 129 до 255, а отрицательные — от 0 до 127. Такой код используется при цифро-аналоговом преобразовании чисел со знаком.

Байтовые данные хранятся как в форме целых чисел без знака, так и в форме целых чисел со знаком, при этом отрицательные числа хранятся в дополнительном коде и старший разряд байта является знаковым (1 — для отрицательных чисел, 0 — для положительных). Рис. 1.12 иллюстрирует как знаковую, так и беззнаковую формы байтовых целых чисел. Разница между этими формами заключается в весе самого левого разряда. Его значение равно 128 для беззнакового целого и –128 для целого со знаком. В формате целого со знаком самый левый разряд одновременно является как знаковым разрядом числа, так и разрядом с весом минус 128. Например, 0x80=10000000(2) представляет значение 128 как беззнакового числа; в качестве же числа со знаком оно представляет число –128. Целые числа без знака имеют диапазон значений 0x00 – 0xFF (0 – 25510). Целые числа со знаком имеют диапазон значений -12810 до +12710.

|

|

|

| 128 | 64 | 32 | 16 | 8 | 4 | 2 | 1 | |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 8(10) |

| –128 | 64 | 32 | 16 | 8 | 4 | 2 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | –8(10) |

Рисунок 1.12 — Байтовые (8-битные) данные

Метод оценки чисел со знаком путем использования весов позиций каждого разряда является намного более легким, чем операция нахождения дополнения до двух числа с целью определения его абсолютного значения.

Всякий раз, когда выполняется нахождение дополнения до двух числа, знак этого числа изменяется с отрицательного на положительный либо с положительного на отрицательный. Например, число 00001000 — это +8. Его отрицательное значение (-8) находится посредством определения дополнения до 2-х числа +8. Для нахождения дополнения числа до 2-х сначала находится его дополнение до одного. Для нахождения дополнения числа до одного, каждый разряд этого числа инвертируется — с нуля на единицу либо с единицы на ноль. Как только дополнение до единицы будет сформировано, определяется дополнение числа до двух посредством добавления единицы к дополнению до одного (рис. 1.12).

|

|

|

Данные в формате ASCII (Американский Стандартный Код для Информационного Обмена — American Standard Code for Information Interchange) представляют алфавитно-цифровые символы в памяти компьютерной системы (табл. 1.8). Стандартный ASCII-код является 7-битным кодом, в котором восьмой (самый старший бит), используется как бит паритета в некоторых устаревших системах. Если ASCII-данные используются для вывода на принтер, то нулевое значение самого старшего бита будет означать режим алфавитно-цифровой печати, а единичное — режим графической печати. В персональном компьютере расширенный набор символов ASCII выбирается установкой единичного состояния самого левого бита.

Управляющие символы ASCII, приведенные в табл. 1.8, выполняют функции управления в компьютерной системе, включая очистку экрана, символ «шаг назад», перевод строки и т.д. Для ввода управляющих кодов с компьютерной клавиатуры нужно, удерживая в нажатом состоянии клавишу Ctrl (Control), вводить соответствующие символы. Так для ввода 0x01, нужно ввести Control-A; а код 0x02 вводится как Control-B и т.д. Обратите внимание на то, что управляющие коды часто появляются на экране как ^A для Control-A, ^В для Control-B и т.д. Также обратите внимание на то, что код возврата каретки (CR) в большинстве современных клавиатур соответствует клавише <Enter> (Ввод). Назначением символа CR является возврат курсора или печатающей головки на левое поле. Другим кодом, который часто появляется во многих программах, является код перевода строки (LF), который перемещает курсор вниз на одну строку.

Таблица 1.8 — ASCII коды

ASCII-данные чаще всего сохраняются в памяти при использовании специальной команды Ассемблера, которая называется declare byte (Объявить байт) или DB, либо командой DATA в случае строк.

Двоично-кодированные десятичные (BCD) данные могут сохраняться как в упакованной, так и неупакованной форме. Упакованные BCD-данные сохраняются в форме двух цифр на байт, а неупакованные BCD-данные сохраняются как одна цифра на байт. Диапазон BCD-цифр лежит от 00002 до 10012, что соответствует десятичным цифрам от 0 до 9. Неупакованные BCD-данные поступают от микрокомпьютерной клавиатуры. Упакованные BCD-данные используются в некоторых командах набора команд микропроцессора, включая BCD-сложение и вычитание.

Табл. 1.9 показывает некоторые десятичные числа, преобразованные, как в упакованную, так и в неупакованную BCD-форму. Приложениями, которые в типичном случае требуют использования BCD-данных, являются локальные торговые терминалы, а также почти любые иные устройства, выполняющие минимальное количество простых арифметических операций. Если системы требуют выполнения сложных арифметических операций, то BCD-данные в них используются редко, поскольку нет простого и эффективного метода выполнения сложных арифметических BCD-операций.

Таблица 1.9 — Упакованные и неупакованные BCD-данные

| Десятичные | Упакованные | Heуп aкованные | |||

| 12 | 0001 0010 | 0000 0001 | 0000 0010 | ||

| 623 | 0000 0110 | 0010 0011 | 0000 0110 | 0000 0010 | 0000 0011 |

| 910 | 0000 1001 | 0001 0000 | 0000 1001 | 0000 0001 | 0000 0000 |

Во всех случаях придерживаются соглашения о порядке записи данных в память, при котором первыми (по младшему адресу) записываются младшие разряды чисел. Это означает, что для сохранения в памяти, например, числа 623 в неупакованном BCD, сначала нужно сохранить 3, затем — 2, и наконец — 6.

Пословные данные. Слово (16 битов) формируется двумя байтами данных. Младший байт всегда сохраняется в ячейке памяти с меньшим номером, а старший — в ячейке с большим номером (адресом). Этот метод сохранения числа называется форматом с обратным порядком байтов. Альтернативный метод, используемый в некоторых других системах, называется форматом с прямым порядком. При использовании этого формата числа сохраняются так, что ячейка с меньшим номером содержит старший байт данных.

Рисунок 1.13 — Пословные (16 бит) данные

Рис. 1.13, вверху показывает веса для каждой битовой позиции слова данных, а рис. 1.13 внизу показывает, как число 1234Н заносится в ячейки памяти 200Н и 21Н. Единственная разница между словом со знаком и беззнаковым словом связана с самой левой битовой позицией. В беззнаковой форме самый левый бит не связан со знаком и имеет вес 32768; в форме со знаком его вес будет равен -32768. Как и в случае байтовых данных со знаком, слово со знаком имеет форму дополнения до двух, когда оно представляет отрицательное число.

Действительные числа иногда встречаются в приложениях — здесь они рассматриваются в силу того, что иногда встроенные контроллеры должны иметь дело с действительными числами. Действительное число или число с плавающей точкой, как его часто называют, состоит из двух частей: мантиссы — значащей или дробной части и экспоненты. Рис. 1.14 показывает как 4-байтовую, так и 8-байтовую форму действительных чисел, как они сохраняются в системах Intel. Обратите внимание на то, что 4-байтовая форма называется формой числа одинарной точности, а 8-байтовая форма называется формой числа двойной точности. Представленные здесь формы сохранения действительных чисел являются теми же, которые специфицированы стандартом IEEE-754, версия 10.0. Этот стандарт был принят в качестве стандартной формы представления действительных чисел практически всеми языками программирования, а также многими прикладными пакетами. Данный стандарт также применяется при манипулировании данными в арифметических сопроцессорах персональных компьютеров. Рис. 1.14, а показывает форму числа одинарной точности, которая содержит бит знака, 8-битную экспоненту и 24-битную дробную часть (мантиссу). Обратите внимание на то, что в силу того, что приложения часто требуют использования чисел с плавающей точкой двойной точности, соответствующая форма также представлена на рис. 1.14, б.

| 31 | 30 | 23 | 22 | 0 | |||||||||||

| знак | экспонента | мантисса | |||||||||||||

а

| 63 | 62 | 52 | 51 | 0 | |||||||||||||||||||||||||||

| знак | экспонента | мантисса | |||||||||||||||||||||||||||||

б

Рисунок 1.14 — Данные, заданные в формате с плавающей точкой: а — одинарной точности; б — двойной точности

Простой арифметический подсчет показывает, что для сохранения всех названных фрагментов данных необходимо 33 бита. Однако это не так — 24-битная мантисса содержит подразумеваемый (неявный) бит, что позволяет мантиссе представлять 24 бита, будучи сохраняемой всего в 23 битах. Неявный бит — это первый бит нормализованного действительного числа. При нормализации числа, оно подстраивается таким образом, что его значение по крайней мере равно единице, однако меньше 2. Например, если 12 преобразовать в двоичную форму (11002), то после нормализации результатом будет: 1.1´23. Целая часть нормализованного числа (1) не сохраняется при использовании 23-битной части числа, задающей мантиссу; 1 находится в единичном «скрытом» бите. Табл. 1.10 показывает форму этого и других чисел одинарной точности.

Таблица 1.10 — Примеры чисел с одинарной точностью

| Десятичное | Двоичное | Нормализованное | Знак | Смещенная экспонента | Мантисса | ||

| +12 | 1100 | 1.1 ´ 23 | 0 | 10000010 | 1000000 | 00000000 | 00000000 |

| -12 | 1100 | 1.1 ´ 23 | 1 | 10000010 | 1000000 | 00000000 | 00000000 |

| +100 | 1100100 | 1.1001 ´ 26 | 0 | 10000101 | 1001000 | 00000000 | 00000000 |

| -1.75 | 1.11 | 1.11 ´ 20 | 1 | 01111111 | 1100000 | 00000000 | 00000000 |

| +0.25 | 0.01 | 1.0 ´ 2–2 | 0 | 01111101 | 0000000 | 00000000 | 00000000 |

| +0.0 | 0 | 0 | 0 | 00000000 | 0000000 | 00000000 | 00000000 |

| + ¥ (- ¥) | + ¥ (- ¥) | 0 (1) | 11111111 | 0000000 | 00000000 | 00000000 | |

| +0.15625 | 0.00101 | 1.01 ´ 2–3 | 0 | 01111100 | 0100000 | 00000000 | 00000000 |

Экспонента сохраняется в форме смещенной экспоненты (специфичный для данного представления формат чисел со знаком). В форме действительного числа одинарной точности смещение равно 127 (0x7F), а при использовании формы действительного числа двойной точности оно равно 1023 (0x3FF). Значения смещения и экспоненты складываются перед сохранением экспоненты в соответствующей части числа с плавающей точкой. Например, экспонента, равная 23, представляется в форме смещенной экспоненты, равной (127+3) или 130 (0x82) в форме действительного числа одинарной точности или как 1026 (0x402) в форме действительного числа двойной точности. Экспонента, равная 2–3, представляется в форме смещенной экспоненты, равной (127–3)=124 (0x7C=01111100(2)) в форме действительного числа одинарной точности или как (1023–3)=1020 (0x3FC=1111111100) в форме действительного числа двойной точности.

Число 0 сохраняется в форме, все разряды которой равны нулю. Это соответствует минимально возможной экспоненте –12710 (–102310). Число «бесконечность» сохраняется в форме, все разряды экспоненты которой имеют единичное значение (максимально возможная экспонента +12810, (+102410)), а мантиссы — нулевое. Знаковый бит в этом случае указывает либо положительную, либо отрицательную бесконечность. В скобках указаны значения для плавающего формата двойной точности.

Бывают отличия в форматах. Так Microchip использует другой формат для чисел с плавающей точкой в компиляторе с языка С С18. Рис. 1.15 иллюстрирует разницу между форматом чисел с плавающей точкой фирмы Microchip и форматом IEEE. Разница заключается в размещении знакового бита числа. Эта разница не оказывает воздействия на работу компилятора С.

IEEE-754

| seee eeee | efff ffff | ffff ffff | ffff ffff |

MICROCHIP

| eeee eeee | sfff ffff | ffff ffff | ffff ffff |

s — знаковый бит

е — экспонента

f — мантисса

Рисунок 1.15 — Форматы чисел с плавающей точкой IEEE и MicroChip

2 Элементы цифровых устройств

2.1 Комбинационные и последовательностные устройства

В общем случае на вход цифрового устройства поступает n (n>1) двоичных переменных X(x1, x2,… xn), а с выхода снимается m (m>1) двоичных переменных Y(y1, y2,… ym). При этом устройства осуществляют (реализуют) определенную связь (ФАЛ) между входными и выходными переменными.

По способу функционирования цифровые устройства делят на комбинационные и последовательностные.

Комбинационными устройствами или автоматами без памяти называют логические устройства, выходные сигналы которых однозначно определяются только действующей в настоящий момент на входе комбинацией переменных и не зависят от значений переменных, действовавших на входе ранее.

В качестве примера на рис. 2.1, б приведена временная диаграмма работы логического элемента И-НЕ с двумя входами и одним выходом (рис. 2.1, а).

а б в

Рисунок 2.1 — Функционирование комбинационных цифровых устройств

В теоретических рассмотрениях (как и в данной теме) обычно считается, что сигналы на выходе комбинационного устройства (КУ) появляются в тот же момент, когда на вход устройства поступают инициирующие их входные сигналы, т. е. предполагается их быстродействие бесконечным.

В реальных электронных приборах задержка выходного сигнала t>0 (t=10–8…10-10 с) — естественный физический предел электронных приборов, (рис. 2.1, в), а в сложных устройствах с последовательным соединением логических элементов задержки суммируются.

Комбинационные узлы и блоки цифровых устройств либо собирают из отдельных микросхем малой степени интеграции (элементов И-НЕ, ИЛИ-НЕ и др.), либо изготавливают в виде систем средней интеграции, либо входят в состав БИС и СБИС. Различные типы комбинационных узлов и блоков широко используются в устройствах ввода-вывода и управления, в оперативных запоминающих устройствах современных цифровых систем.

По функциональному назначению можно выделить следующие классы КУ: сум маторы, шифраторы и дешифраторы, цифровые компараторы, мультиплексоры и демультиплексоры, преобразователи кодов, программируемые логические матрицы (ПЛМ), перемножители, арифметико-логические устройства.

Для построения цифровых систем, кроме комбинационных узлов, требуются последовательностные устройства (автоматы с памятью), значения выходных двоичных переменных Y которых определяются как значениями входных переменных Х в течение рассматриваемого такта работы, так и предысторией системы (предыдущим состоянием).

Последовательностными устройствами, или автоматами с памятью, называют логические устройства, выходные сигналы которых определяются не только действующей в настоящий момент на входе комбинацией переменных, но и всей последовательностью входных переменных, действовавших в предыдущие моменты времени. Этот тип устройств часто называют цифровыми автоматами.

В последовательностных устройствах, кроме логических, должны быть еще и запоминающие элементы — элементы памяти с множеством входов и выходов (рис. 2.2), включаемые в цепи обратной связи, в соответствии со стрелками, указывающими прохождение сигналов. При этом память системы может охватывать не бесконечно большое, а лишь конечное число тактов, формируемых генератором тактовых импульсов (ГТИ) (см. рис. 2.2). Поэтому цифровые устройства с памятью называют конечными автоматами, которыми являются все ЭВМ. Следует отметить, что сам элемент памяти содержит также внутренние обратные связи и является последовательностным устройством.

В последовательностных устройствах, кроме логических, должны быть еще и запоминающие элементы — элементы памяти с множеством входов и выходов (рис. 2.2), включаемые в цепи обратной связи, в соответствии со стрелками, указывающими прохождение сигналов. При этом память системы может охватывать не бесконечно большое, а лишь конечное число тактов, формируемых генератором тактовых импульсов (ГТИ) (см. рис. 2.2). Поэтому цифровые устройства с памятью называют конечными автоматами, которыми являются все ЭВМ. Следует отметить, что сам элемент памяти содержит также внутренние обратные связи и является последовательностным устройством.

Обозначим t и (t+1) два следующих друг за другом такта конечного автомата. Состояние элементов памяти в (t+1)-й такт определяется множествами как входных x сигналов, так и сигналов q на выходах элементов памяти в предыдущий такт t, т. е.:

или

или

Это выражение называют функцией переходов автомата с памятью.

Выходные же сигналы Y могут формироваться двояко. В автоматах Мили они являются функциями как входных сигналов, так и сигналов элементов памяти в этом же такте, т. е. функция выходов автомата Мили:

.

.

В автоматах Мура они являются функциями только сигналов элементов памяти в этом же такте (состояния автомата), т. е. функция выходов автомата Мура:

Существуют правила перехода от одного вида автоматов к другому.

Функции переходов qj и выходов у i последовательностных устройств представляют в виде таблиц переходов и выходов или объединенными таблицами состояний. Как отмечалось, реальные элементы всегда инерционны. Таблицы и алгебраические функции соответствуют статическим режимам. В динамических режимах (в переходной части тактов) связь между переменными может оказаться отличающейся от режима статики, что может привести к сбоям (ошибкам), т. е. к появлению ошибочных сигналов на входах памяти, а также к ошибочным состояниям автомата. Это явление называют «гонками» в автоматах, и его надо учитывать при синтезе конкретных цифровых блоков и устройств.

Учитывая это явление, во многих автоматах, называемых синхронными, элементы памяти управляются внешними тактовыми импульсами ГТИ (рис. 2.2), обеспечивающими переход элементов памяти из состояния t в состояние (t+1) и выдачу сигналов yi после завершения переходных процессов в момент подачи (или окончания) тактового импульса. В асинхронных автоматах изменение входных сигналов сразу влечет за собой соответствующие изменения выходных сигналов.

Простейшими конечными автоматами являются триггеры, они же, в свою очередь, являются элементами памяти более сложных цифровых устройств. Основными типами функциональных узлов последовательностных устройств являются триггеры, регистры, счетчики и генераторы чисел.

Познакомимся с некоторыми типовыми узлами и блоками комбинационных и последовательностных устройств в интегральном исполнении.

2.2 Шифраторы, дешифраторы, преобразователи кодов

Дешифратор или декодер — комбинационная схема с n входами и m выходами (m> n), преобразующая двоичный входной n-разрядный код (кодовое слово) в унитарный (один из m).

Дешифратор или декодер — комбинационная схема с n входами и m выходами (m> n), преобразующая двоичный входной n-разрядный код (кодовое слово) в унитарный (один из m).

На одном из m выходов дешифратора появляется логическая единица (нуль, если выходы инверсные, с кружками), а именно на том, номер которого равен поданному на вход двоичному числу. На всех остальных выходах дешифратора выходные сигналы равны нулю (единице при инверсных выходах). Дешифратор используют, когда нужно обращаться к различным цифровым устройствам, и при этом номер устройства — его адрес представлен двоичным кодом.

Условное изображение дешифратора 4®16 (читаемого «четыре в шестнадцать») на схемах представлено на рис. 2.3. Полный дешифратор DC содержит число выходов, равное числу комбинаций входных переменных, например, при n=4, m =2n=16, от  до

до  . Обратим внимание, что в конъюнкциях используется общая инверсия, поскольку выходы дешифратора — инверсные.

. Обратим внимание, что в конъюнкциях используется общая инверсия, поскольку выходы дешифратора — инверсные.

Каждый выход полного дешифратора реализует конъюнкцию входных переменных (код адреса) или их инверсий: при наборе  (0000), у 0 = 0; при

(0000), у 0 = 0; при  (1000) y8=0; при

(1000) y8=0; при  (1111),.y15=0 и т. д.

(1111),.y15=0 и т. д.

Применяются также неполные дешифраторы с меньшим числом выходов (например 10 у двоично-десятичного дешифратора 4®10 при четырех переменных на входе). В этом случае ряд комбинаций на входе не используется (рис. 2.4).

Дешифраторы часто имеют разрешающий (управляющий, стробирующий) вход G (G1, G2 на рис. 2.3). При G=1 дешифратор функционирует как обычно, при G=0 на всех выводах устанавливается 0 независимо от поступающего кода адреса. Отметим, что для дешифратора ИД3 (рис. 2.3) все происходит наоборот, поскольку и разрешающие входы G и выходы у него инверсные. Вход разрешения позволяет наращивать размерность дешифраторов, применяя многоступенчатую пирамидальную структуру. Дешифраторы широко используют во многих устройствах, в том числе в качестве преобразователей двоичного кода в унитарный, для выбора внешних устройств МПС по коду с шины адреса.

Дешифраторы часто имеют разрешающий (управляющий, стробирующий) вход G (G1, G2 на рис. 2.3). При G=1 дешифратор функционирует как обычно, при G=0 на всех выводах устанавливается 0 независимо от поступающего кода адреса. Отметим, что для дешифратора ИД3 (рис. 2.3) все происходит наоборот, поскольку и разрешающие входы G и выходы у него инверсные. Вход разрешения позволяет наращивать размерность дешифраторов, применяя многоступенчатую пирамидальную структуру. Дешифраторы широко используют во многих устройствах, в том числе в качестве преобразователей двоичного кода в унитарный, для выбора внешних устройств МПС по коду с шины адреса.

Шифратор (CD) или кодер (encoder) выполняет функцию, обратную дешифратору — преобразует унитарный код в двоичный (двоично-десятичный). Условное изображение шифратора 16®4 на схемах показано на рис. 2.5. Классический полный шифратор имеет n входов и m выходов (m<n), и при подаче активного уровня сигнала на один из входов (и не более) на его выходах появляется двоичный код номера возбуждённого входа. Число входов и выходов такого шифратора связано соотношением n = 2 m.

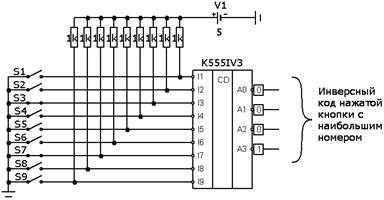

Если n<2 m, то шифратор называется неполным. Например, шифратор 9-4 может быть использован для преобразования нажатой клавиши 9-клавишного пульта в двоичный код (рис. 2.6).

| Входы | Выходы | |||||||||||

| I9 | I8 | I7 | I6 | I5 | I4 | I3 | I2 | I1 | A3 | A2 | A1 | A0 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | X | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 0 | X | X | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 | 0 | X | X | X | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 | 0 | X | X | X | X | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | X | X | X | X | X | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | X | X | X | X | X | X | 1 | 0 | 0 | 0 |

| 1 | 0 | X | X | X | X | X | X | X | 0 | 1 | 1 | 1 |

| 0 | X | X | X | X | X | X | X | X | 0 | 1 | 1 | 0 |

Рисунок 2.6 — Преобразование номера нажатой кнопки в ее двоичный код с помощью

приоритетного шифратора

Области использования шифраторов — отображение в виде двоичного кода номера нажатой кнопки (рис. 2.6) или положения многопозиционного переключателя, а также номера устройства, подавшего сигнал на обслуживание в микропроцессорных системах, входят в состав микросхем контроллеров прерываний.

Как раз для случая контроллера прерываний характерно использование так называемого приоритетного шифратора. Он отличается от обычного тем, что при возбуждении одновременно нескольких входов на его выходе появится код соответствующий возбужденному входу с наибольшим номером (с наиболее высоким приоритетом, рис. 2.6). Примеры схем приоритетных шифраторов К555ИВ3 (аналог 74XXX147), К555ИВ1 (аналог 74148, но входы и выходы — инверсные).

Преобразователями кодов, в общем случае, называют устройства, предназначенные для преобразования одного кода в другой, при этом часто они выполняют нестандартные преобразования кодов. Преобразователи кодов обозначают через X/ Y.

Рассмотрим особенности реализации преобразователя на примере преобразователя трехэлементного кода в пятиэлементный. Допустим, что необходимо реализовать таблицу соответствия кодов (табл. 2.1).

Таблица 2.1 — Таблица соответствия кодов кодопреобразователя

| Трехэлементный код | Пятиэлементный код | |||||||

| N | x 3 | х 2 | x1 | y5 | y4 | y3 | y2 | y1 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 |

| 2 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 |

| 3 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |

| 4 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 |

| 5 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 |

| 6 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 |

| 7 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 |

Здесь через N обозначено десятичное число, соответствующее входному двоичному коду. Преобразователи кодов часто создают по схеме дешифратор — шифратор. Дешифратор преобразует входной код в некоторый унитарный код, а затем шифратор формирует выходной код. Схема преобразователя, созданного по такому принципу, приведена на рис. 2.7, где использован матричный диодный шифратор. Принцип работы такого преобразователя довольно прост. Например, когда на всех входах дешифратора логический «0», то на его выходе 0 появляется логическая «1», что приводит к появлению «1» на выходах у 2 и у 1 , т. е. реализуется первая строка таблицы соответствия кодов.

Рисунок 2.7 — Схема преобразователя кодов по структуре дешифратор-шифратор

При использовании в качестве второй ступени обычного шифратора (а не диодной матрицы) эффективно стыкуются друг с другом декодер и кодер, построенные на элементах И-НЕ: первый имеет инверсные выходы, а второй — инверсные входы. Если некоторым входным комбинациям соответствует одна и та же выходная, то соответствующие выходы декодера объединяют на элементе ИЛИ и выход последнего подают на нужный вход кодера.

Проектирование кодовой преобразовательной схемы на паре декодер-кодер оказывается в среднем более выгодным и по числу корпусов, и по быстродействию, чем при проектировании из готовых базовых логических микросхем И-НЕ и ИЛИ-НЕ при использовании методик минимизации. Однако потребляемая мощность в этом случае может оказаться больше, чем у схемы из отдельных элементов. Затраты времени разработчика на логическое проектирование по схеме декодер-кодер неизмеримо меньше, чем затраты на проектирование преобразователя кодов из россыпи логических микросхем.

Преобразователи кодов в виде микросхем выпускаются для выполнении таких операций, как преобразования двоично-десятичного кода в двоичный или обратного преобразования, для преобразования двоичного кода в код Грея, для преобразования двоичного кода в код управления шкальными или матричными индикаторами, для преобразования двоично-десятичного кода в код управления сегментными индикаторами.

Так, микросхемы 74LS47, 74LS48 (рис. 2.8) представляют преобразователь двоично-десятичного кода в код семисегментного индикатора для семисегментных светодиодных дисплеев с общим анодом и общим катодом соответственно.

Рисунок 2.8 — Работа дешифратора индикатора на семисегментный светодиодный дисплей

с общим катодом

2.3 Мультиплексоры и демультиплексоры

Мультиплексор (MS) — это функциональный узел, осуществляющий подключение (коммутацию) одного из нескольких входов данных к выходу. Номер выбранного входа соответствует коду, поданному на адресные входы мультиплексора. Условное изображение мультиплексора на четыре входа и возможный вариант его структурной схемы показаны на рис. 2.9, а, б.

При состоянии адресных входов 00 (код адреса х2=0, х1=0) у= а; при состоянии 01 (x2=0, х1=1) у= b; при состоянии 10 (х2=1, х1=0) у= с; в положении 11 (x2=l, x1=1) у=d. Функционирование мультиплексора описывается выражением:

Вход Е — разрешающий: при Е=1 мультиплексор работает как обычно, при Е=0 его выход находится в неактивном состоянии, мультиплексор заперт.

Рисунок 2.9 — Мультиплексор из 4 в 1: а — условное обозначение; б — внутренняя структура

Серийные ИМС выпускаются с числом адресных входов n=2, 3 и 4 при возможном числе 2n коммутируемых входов (рис. 2.10). При необходимости коммутировать большее количество входов используют несколько мультиплексоров.

Рисунок 2.10 — Мультиплексоры разной размерности

Мультиплексоры находят широкое применение в устройствах отображения информации в различных микропроцессорных устройствах управления и ЭВМ.

Демультиплексоры выполняют функцию, обратную мультиплексорам, т. е. производят коммутацию одного входного сигнала на 2n выходов, где n — число адресных входов xi. Они могут осуществлять преобразование информации из последовательной формы (последовательно-параллельной) в параллельную. Демультиплексор имеет один информационный вход D и несколько выходов, причем вход подключается к выходу yi имеющему адрес, заданный кодом на адресных входах.

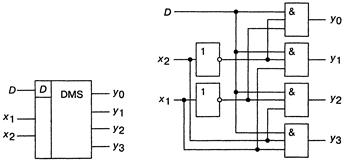

В качестве примера на рис. 2.11, а дано условное графическое обозначение демультиплексора (DMS), имеющего четыре выхода, закон функционирования которого задан (табл. 2.2). Пользуясь таблицей 2.2, запишем переключательные функции для выхода устройства:

.

.

Функциональная схема демультиплексора, реализующая эти выражения, приведена на рис. 2.11, б.

а б

Рисунок 2.11 — Демультиплексор 1-4: а — условное обозначение; б — внутренняя структура

Таблица 2.2 — Таблица истинности демультиплексора 1–4

| D | x2 | х1 | y3 | y2 | y1 | y0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 |

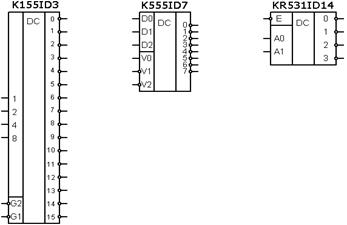

Функции демультиплексоров сходны с функциями дешифраторов. Дешифратор можно рассматривать как демультиплексор, у которого информационный вход поддерживает напряжение выходов в активном состоянии, а адресные входы выполняют роль входов дешифратора. Поэтому в обозначении как дешифраторов, так и демультиплексоров используются одинаковые буквы — ИД. Выпускают дешифраторы (демультиплексоры) К155ИДЗ, К531ИД7 и др.

Так, если в дешифраторе КР531ИД14А (рис. 2.13) вход разрешения Е использовать как вход данных, а информационные входы дешифратора считать за адресные входы демультиплексора, то получим демультиплексор 1®4, который работает аналогично демультиплексору рис. 2.11 (за небольшим исключением — у этих устройств разные пассивные уровни выходов).

Рисунок 2.12 — Демультиплексоры

2.4 Компараторы кодов

Цифровой компаратор предназначен для определения равенства двоичных чисел. Операция поразрядного сравнения заключается в выработке признака равенства (равнозначности) или неравенства (неравнозначности) двух сравниваемых двоичных чисел. Два числа равны при равенстве цифр в одноименных разрядах: ai = b i, где а i — цифра в i-ом разряде одного числа; b i — цифра в

i-ом разряде другого числа. Равенство ai = b i, имеет место при а i=1, bi=1 или при а i=0, bi=0. Поэтому логическая функция, выражающая это равенство, равна единице, если единице равно произведение этих цифр или произведение их инверсных значений, т. е.:

,

,

а логическая функция, описывающая компаратор равенства, имеет вид:

Для построения компаратора равенства только на элементах И-НЕ, запишем её в другой форме, воспользовавшись формулами де Моргана:

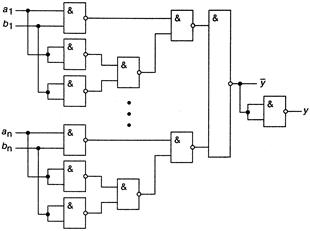

Схема, реализующая это выражение, приведена на рис. 2.13.

Рисунок 2.13 — Схема компаратора 2-х n-разрядных кодов на совпадение в базисе И-НЕ

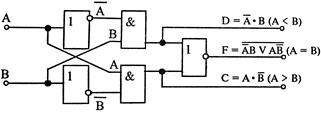

Помимо совпадения кодов реальные ИМС цифровых компараторов могут определять и вид их неравенства А>В или А<В. Т.е. реальные ИС компараторов имеют три выхода. Схема такого одноразрядного компаратора приведена на рис. 2.14.

Рисунок 2.14 — Одноразрядный компаратор с определением равенства и вида неравенства

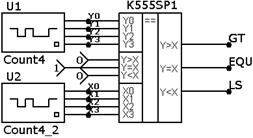

Цифровые компараторы выпускают, как правило, в виде самостоятельных микросхем. Так, например, имеется ТТЛШ микросхема К555СП1 (рис. 2.15) и КМОП К564ИП2, которые являются 4-хразрядными компараторами с определением типа неравенства и возможностью наращивания разрядности.

Рисунок 2.15 — Включение микросхемы компаратора 4-хразрядных кодов К555СП1

Если используется одна микросхема, то на ее вход Y=X следует подать логическую 1.

2.5 Двоичные полусумматор и сумматор

Сумматор — это устройство, в котором выполняется арифметическая операция суммирования цифровых кодов двух двоичных чисел. Известно, что числа в любой позиционной системе счисления складываются поразрядно. Поэтому для сложения двух чисел нужно иметь типовые узлы, реализующие суммирование цифр одного разряда слагаемых с учетом возможного переноса единицы из соседнего младшего разряда. К таким узлам относят одноразрядные комбинационные полусумматоры и сумматоры.

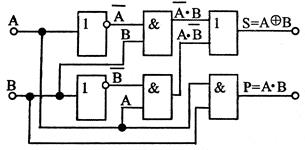

Полусумматор предназначен для суммирования двух одноразрядных двоичных чисел. Он имеет два входа — а i и bi и два выхода — S i и Pi+1, где S i — выход суммы, а Pi+1 является выходом переноса (табл. 2.3). Логические функции для  и

и  и функциональную схему (рис. 2.16) этого узла легко построить на основе таблицы истинности (таблица 2.3), используя элементы И, ИЛИ и НЕ.

и функциональную схему (рис. 2.16) этого узла легко построить на основе таблицы истинности (таблица 2.3), используя элементы И, ИЛИ и НЕ.

Таблица 2.3 — Таблица истинности одноразрядного полусумматора

| а i | bi | Pi+1 | S i |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Рисунок 2.16 — Схема одноразрядного полусумматора

При построении сумматоров на интегральных микросхемах для обеспечения быстродействия и минимального количества однотипных логических элементов необходимо уменьшить число последовательно включенных элементов. Анализ показал, что более экономичной по количеству элементов и быстродействующей является функциональная схема полусумматора, реализующая переключательную функцию:

,

,

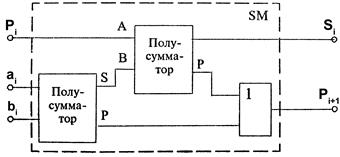

При суммировании двух многоразрядных чисел для каждого разряда (кроме младшего) необходимо использовать устройство, имеющее дополнительный вход переноса (из предыдущего более младшего разряда, вспомните правило сложения в столбик). Такое устройство (рис. 2.17) называют полным

сумма тором и его можно представить как объединение двух полусумматоров (Р вх — дополнительный вход переноса). Сумматор обозначают через SM.

В универсальных АЛУ, входящих в состав цифровых устройств, одноразрядные сумматоры проектируют из двух полусумматоров, объединенных в один выход S (рис. 2.17).

Рисунок 2.17 — Одноразрядный полный сумматор на основе двух полусумматоров

Многоразрядные комбинационные сумматоры последовательного или параллельного действия строятся на основе одноразрядных комбинационных сумматоров, реализующих функции для каждого разряда:

,

,

По этим функциям можно построить сумматор и на элементах И-НЕ или ИЛИ-НЕ.

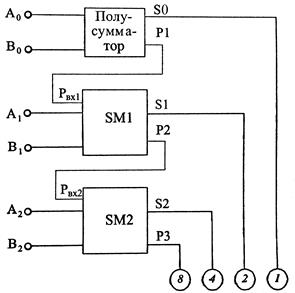

Соединяя определенным образом полусумматоры и полные сумматоры друг с другом, получают устройство для выполнения сложения нескольких разрядов двоичных чисел. В качестве примера рассмотрим устройство для сложения двух трехразрядных двоичных чисел А 2 А1, А0 и В 2 В1, В0, где A0 и В 0 — младшие разряды двоичных чисел (рис. 2.18).

На выходах S 2… S0 формируется код суммы чисел А 2 А 1 A0 и В 2 В1 В 0 , а на выходе Р 3 — сигнал переноса в следующую микросхему, так как при сложении двух трехразрядных двоичных чисел может получиться четырехразрядное число.

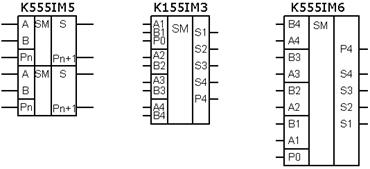

Следует отметить, что в рассмотренной структуре для суммирования в каждом разряде используется отдельный сумматор, но перенос из разряда в разряд осуществляется последовательно, что и определяет время выполнения суммирования. Рассмотренный сумматор называется параллельным сумматором c последовательным переносом (К155ИМ3).

Рисунок 2.18 — Параллельный 3-хразрядный сумматор с последовательным переносом

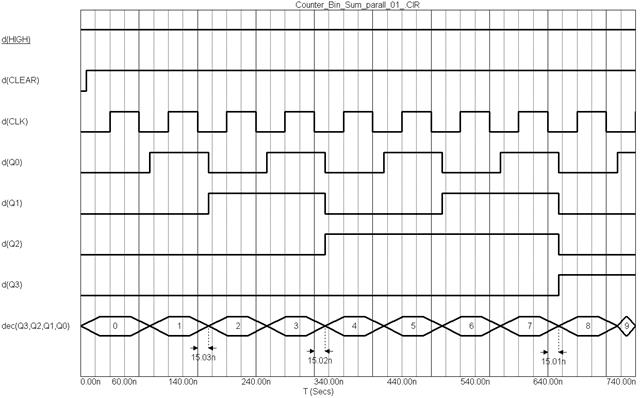

Для повышения быстродействия сумматоров необходимо уменьшить время переноса, что достигается использованием вместо последовательного параллельного переноса. В этом случае в каждом разряде как сигнал суммы, так и сигнал переноса непосредственно формируются из входных переменных. Так микросхема К555ИМ6 (74LS283) представляет собой четырехразрядный сумматор с параллельным переносом.

В виде интегральных микросхем выпускаются одноразрядные, двухразрядные и четырехразрядные двоичные сумматоры (рис. 2.19).

Рисунок 2.19 — Двоичные сумматоры

Рассмотренные сумматоры могут использоваться для вычитания двоичных чисел. В этом случае операция вычитания заменяется сложением уменьшаемого с вычитаемым, представленным в дополнительном коде, т. е. операцией:

Апр – Впр = Апр + Bдоп = Апр+Bобр+1.

где А={ A3 A2 A1 A0} , и В={ B3 B2 B1 B0} — многоразрядные двоичные числа, здесь для примера, четырехразрядные.

,

,

Рассмотрим 2 примера вычитания (10-5) и (5-10).

Двоичный эквивалент +1010=010102, а +510=001012.

Числа в дополнительных кодах:

–1010=10доп=10110B, –510=5доп=11011B

Для реализации описанного алгоритма вычитаемое нужно преобразовать в дополнительный код (см. выше) и сложить с уменьшаемым:

01010 00101

1 1011 10110

00101=510 11011=–510

Четыре младших разряда результата представляют собой результат в дополнительном коде, т. е. десятичное число 5 (в первом случае положительное, а во втором — отрицательное).

Следует подчеркнуть, что если А>В, т. е. результат — положительное число, то ответ формируется в прямом коде (знаковый разряд равен 0), при этом формируется 1 переноса в более старший разряд. При А<В ответ формируется в дополнительном коде (знаковый разряд равен 1) и 1 переноса в более старший разряд не образуется.

Принципиально возможно построение функциональных схем сумматоров, работающих в любой системе счисления, отличающейся от двоичной.

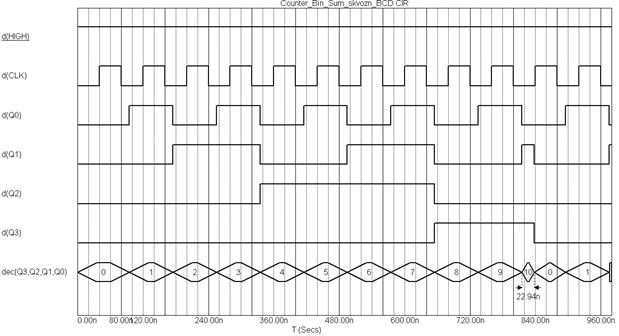

Кроме двоичных, в микропроцессорной технике часто используются так называемые двоично-десятичные коды. Они отображают выраженные в виде последовательности двоичных разрядов десятичные числа. Очевидно, что для представления десятичных цифр необходим, как минимум 4-разрядный двоичный код. При этом из 16 возможных его комбинаций используется только 10. Это предполагает разработку большого числа различных двоично-десятичных кодов (см. табл. 1.5).

На практике большое распространение получил класс так называемых взвешенных кодов. В этих кодах каждому разряду двоичного числа присваивается вполне определенный весовой коэффициент (см. табл. 1.5). В табл. 2.4 приведено соответствие десятичных чисел и их двоичных и двоично-десятичных эквивалентов в коде 8-4-2-1. Весовые коэффициенты его двоичных разрядов соответственно равны 8, 4, 2, 1.

Таблица 2.4. Двоичные и двоично-десятичные коды чисел от 0 до 15

| Двоичный код x3x2x1x0 | Двоично-десятичный код | Десятичное число |

| 0000 | 0000 | 0 |

| 0001 | 0001 | 1 |

| 0010 | 0010 | 2 |

| 0011 | 0011 | 3 |

| 0100 | 0100 | 4 |

| 0101 | 0101 | 5 |

| 0110 | 0110 | 6 |

| 0111 | 0111 | 7 |

| 1000 | 1000 | 8 |

| 1001 | 1001 | 9 |

| 1010 | 0001 0000 | 10 |

| 1011 | 0001 0001 | 11 |

| 1100 | 0001 0010 | 12 |

| 1101 | 0001 0011 | 13 |

| 1110 | 0001 0100 | 14 |

| 1111 | 0001 0101 | 15 |

Из приведенной таблицы следует, что 4-разрядные двоичные коды с 1010 по 1111 не имеют 4-разрядного двоично-десятичного эквивалента. Так, число 12 в двоично-десятичном коде представляется 8-разрядным упакованным кодом 00010010, а число 16 — кодом 00010110.

Описанная особенность двоично-десятичного кода предполагает использование для суммирования специальных логических схем. Смысл их построения состоит в том, что сначала двоично-десятичные коды суммируются как двоичные. Если результатом суммирования является несуществующий двоично-десятичный код, его необходимо уменьшить на 1010, и дополнительно сформировать сигнал переноса. Уменьшение кода на 1010 может выполняться его суммированием с дополнительным кодом числа 10 (в двоичной системе

–1010= 101102, т.е. фактически прибавлением 610=1102).

Необходимость выполнения такого суммирования согласно табл. 2.4 после минимизации выражается ФАЛ F= x3( x2 + x1).

Очевидно, что такое же суммирование необходимо выполнять и в случае, если в результате суммирования тетрад (BCD-кодов) получен сигнал переноса в старший разряд. С учетом сказанного, ФАЛ необходимости выполнения дополнительного суммирования имеет вид:

F = x3( x2 + x1)+ P (2.1),

где x3, x2, x1, x0 — разряды полученного кода в порядке убывания весов, P — перенос, возникший при сложении текущих тетрад BCD-кодов.

Таким образом, для реализации операции сложения двух двоично-десятичных кодов необходимы два 4-хразрядных сумматора и логическая схема, обеспечивающая формирование выходного сигнала в соответствие с ФАЛ (2.1).

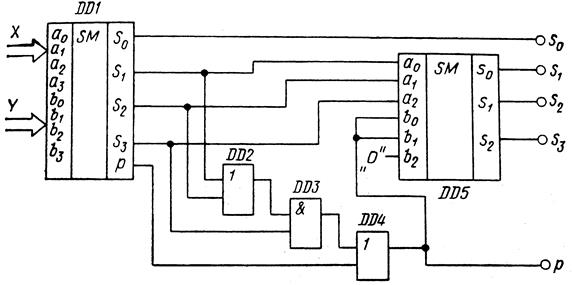

Пример реализации такого устройства показан на рис. 2.20. Четырехразрядный сумматор DD1 выполняет арифметическое сложение исходных двоично-десятичных кодов. Логическая схема на элементах DD2, DD3 и DD4 реализует ФАЛ (2.1), определяя необходимость дополнительного суммирования, выполняемого сумматором DD5.

Рисунок 2.20 — Сумматор двух BCD-чисел

2.6 Арифметико-логические устройства

Арифметико-логическое устройство (АЛУ) — часть центрального процессора, которая в общем случае формирует функции двух входных переменных и порождает одну выходную переменную. Эти функции обычно состоят из простых арифметических операций, простых логических операций и операций сдвига.

Вне зависимости от того, насколько широк круг операций, реализуемых современными АЛУ, главными среди них остаются операции арифметического сложения и умножения, продолжительность выполнения которых указывается в качестве основных характеристик вычислительного устройства. Простейшие операции: арифметическое сложение (вычитание), логическое умножение, логическое сложение, сумма по модулю два, инверсия, сдвиг влево, сдвиг вправо, инкремент (положительное приращение), декремент (отрицательное приращение) выполняются в АЛУ с помощью только аппаратных средств (схем на логических элементах). Операция умножения (деления), как правило, выполняется программным способом (с применением последовательного исполнения нескольких операций сложения и сдвига, выполненных аппаратным способом). Однако, как будет показано далее, существуют и аппаратные умножители.

АЛУ классифицируют по различным признакам.

По способу действия над операндами АЛУ подразделяют на

· АЛУ параллельного действия

· АЛУ последовательного действия.

По способу представления чисел различают:

· АЛУ для чисел с фиксированной запятой

· АЛУ для чисел с плавающей запятой

· АЛУ для десятичных чисел.

По способу организации работы:

· синхронные АЛУ

· асинхронные АЛУ

По характеру используемых элементов и узлов:

· Универсальные, в которых операции для всех форм представления чисел выполняются одними и теми же схемами,

· Функциональные, в которых операции над операндами с фиксированной и плавающей запятой, с десятичными переменными и логическими переменными осуществляются в отдельных операционных блоках.

В настоящее время практически все АЛУ выполняются в интегральном исполнении и выпускаются различные серии соответствующих ИС. Проиллюстрируем функциональные возможности таких схем на примере ИС К531ИК2 (74LS381). Ее условное обозначение приведено на рис. 2.21.

Данная схема оперирует с двумя 4-разрядными входными кодами и способна выполнять 3 логических (поразрядные И, ИЛИ, исключающее ИЛИ) и 3 арифметических (сложение, вычитания (A-B), (B-A)) операций. Тип выполняемой операции определяется кодовой комбинацией на входах S2,S1,S0 (Табл. 2.5). Вход C0 представляет собой перенос из предыдущего разряда при сложении, инверсный заем из следующего разряда при вычитании. Выходы P, G представляют собой инверсные биты переноса для каскадирования и переполнения соответственно (схема Micro-CAP 381.cir).

Таблица 2.5 — Операции, выполняемые схемой АЛУ 74LS381

Таблица 2.5 — Операции, выполняемые схемой АЛУ 74LS381

| S2 | S1 | S0 | Операция |

| 0 | 0 | 1 | B – A |

| 0 | 1 | 0 | A – B |

| 0 | 1 | 1 | A + B |

| 1 | 0 | 0 | A XOR B |

| 1 | 0 | 1 | A OR B |

| 1 | 1 | 0 | A AND B |

| 1 | 1 | 1 | PRESET |

Логика построения аппаратных умножителей неразрывно связана с традиционным алгоритмом выполнения операции умножения, базирующемся на суммировании частных произведений разрядов сомножителей. Проиллюстрируем сказанное на примере умножения 2-разрядных двоичных кодов:

a1 a0

X b1 b0

__________________________

b0a1 b0a0

+ b1a1 b1a0

__________________________

M3 M2 M1 M0

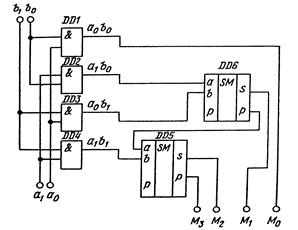

Структурная схема устройств показана на рис. 2.22. Частные произведения разрядов сомножителей формируются ЛЭ 2И — DD1…DD4. Суммируя эти произведения сумматорами DD5 и DD6 находят значение кода результата. Приведенная структура носит название матричного множительного блока.

Рисунок 2.22 — Основная ячейка матричного множительного блока

Используя аналогичный подход, можно синтезировать матричный множительный блок, работающий с входными кодами произвольной разрядности.

При разработке ИС желательно использовать структуру, позволяющую увеличивать разрядность входных кодов путем использования нескольких однотипных схем. Устройство, приведенное на рис. 20.22, этому требованию не удовлетворяет. Для нахождения структурной схемы умножителя, удовлетворяющей указанному требованию, рассмотрим алгоритм умножения двух 4-разрядных кодов:

| a3 | a2 | a1 | a0 | |||||

| X | b3 | b2 | b1 | b0 | ||||

| b0a3 | b0a2 | b0a1 | b0a0 | |||||

| b1a3 | b1a2 | b1a1 | b1a0 | |||||

| + | b2a3 | b2a2 | b2a1 | b2a0 | ||||

| b3a3 | b3a2 | b3a1 | b3a0 | |||||

| M7 | M6 | M5 | M4 | M3 | M2 | M1 | M0 |

Очевидно, что приведенный алгоритм можно представить в виде комбинации четырех однотипных блоков (выделены линией), соответствующих рассмотренному выше умножению 2-разрядных кодов. Однако для такого представления, кроме получения частного произведения, каждый из выделенных блоков должен выполнять дополнительные операции сложения.

Реализация умножения многоразрядных чисел на основе однотипных блоков требует введения в схему основной ячейки рис. 2.22 двух дополнительных сумматоров [11].

2.7 Триггеры

Триггером называется устройство, имеющее два устойчивых состояния и сохраняющее любое из них сколь угодно долго после снятия внешнего воздействия, вызвавшего переход триггера из одного состояния в другое. Поэтому говорят, что триггер обладает памятью. Триггер можно представить в общем случае состоящим из ячейки памяти и устройства управления (порой весьма сложного), преобразующего входную информацию в комбинацию сигналов, под воздействием которых ячейка памяти принимает одно из двух устойчивых состояний.

По способу записи информации триггеры могут быть асинхронными и синхронными. Триггер называют асинхронным, если сам сигнал, несущий информацию, вызывает его переключение. В синхронных (тактируемых) триггерах информация записывается при одновременном воздействии информационного сигнала и синхронизирующего (разрешающего) импульса. Синхронизация может осуществляться импульсом (потенциалом) или перепадом потенциала (фронтом или срезом импульса). В первом случае (статическое управление) сигналы на информационных входах оказывают влияние на состояние триггера в течение всего времени наличия синхроимпульса. Во втором случае (динамическое управление) воздействие информационных сигналов проявляется только в моменты изменения потенциала на входе синхронизации, т.е. при переходе его от 0 к 1 (фронт) или от 1 к 0 (срез).

По функциональному признаку различают RS-триггеры, D-триггеры,

Т-триггеры и JK-триггеры, а также их комбинации.

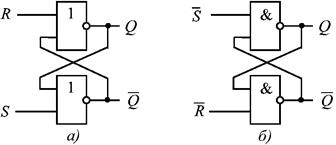

Рисунок 2.23 — Асинхронный RS-триггер с прямым (а) и инверсным (б) управлением

Рисунок 2.24 — Тактируемый RS-триггер: а) построение триггера на логических элементах

И-НЕ; б) обозначение триггера на функциональных схемах; в) временные диаграммы,

поясняющие работу триггера

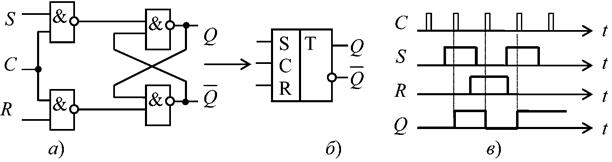

D-триггер (от английского Delay – задержка) имеет один информационный (D – Data – данные) и один тактируемый (С – Clock – тактовая последовательность) вход. Такой триггер можно получить из RS-триггера, подав на R-вход инвертированный сигнал с S-входа (рис. 2.25, а). Условное обозначение D-триггера со статическим управлением показано на рис. 2.25, б. Из временных диаграмм, приведенных на рис. 2.25, в можно увидеть, что при С=1 триггер работает как повторитель (Q=D), а при переходе сигнала на входе С от логической единицы к логическому нулю триггер запирается и переходит в режим хранения (защелкивает информацию со входа D). В отличие от RS-триггера, D‑триггер не имеет запрещенного состояния.

Статический синхронный триггер реагирует на входные сигналы в течение всего времени, пока тактовый сигнал С равен единице. Часто, однако, требуется триггер, в котором считываемая информация не передавалась бы непосредственно на выход, а появлялась там только тогда, когда все схемы уже заперты. Этим свойством обладают триггеры с динамическим управлением.

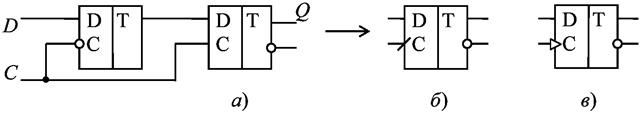

Рисунок 2.25 — Синхронный D-триггер со статическим управлением

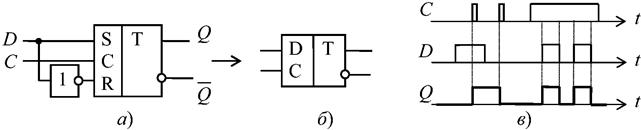

D-триггер с динамическим управлением, тактируемый фронтом тактового импульса, можно выполнить по двухступенчатой схеме, показанной на рис. 2.26, а. При С=0 триггер первой ступени повторяет сигнал D, но триггер второй ступени защелкнут (находится в режиме хранения). При переходе к С=1 первый триггер защелкивает на своем выходе информацию со входа D, а второй повторяет ее на своем выходе. Таким образом, двухступенчатый триггер по фронту тактового импульса защелкивает на своем выходе уровень сигнала с входа D и сохраняет его до следующего фронта. Триггеры с динамическим управлением необходимы для построения счетчиков и регистров сдвига.

Из двух вариантов УГО динамического входа, приведенных на рис. 2.26, б и в, в дальнейшем будем использовать вариант б, меняя направление косой черты для обозначения входа при тактировании по срезу импульса.

Рисунок 2.26 — Синхронный триггер задержки с динамическим управлением (а)

и варианты его УГО (б, в)

Серийно производимые в семействах ТТЛ D-триггеры, переключающиеся по положительному фронту, устроены не по принципу «ведущий-ведомый», на основе которого действует схема, приведенные на рис. 2.26, а. Вместо этого в триггерах типа 74LS74 (555ТМ2) реализована схема на 6 вентилях (рис. 2.27), которая меньше по объему и быстрее и обычно в литературе называется шестиэлементным триггером или схемой трех триггеров [1, 2]. Для уяснения работы такого триггера запишем систему функций алгебры логики ФАЛ, обозначив сигналы на выходах элементов D1–D4 X1– X4 соответственно. При этом будем считать, что триггер разблокирован по входам предустановки, т.е.  .

.

(2.2)

(2.2)

Решим систему уравнений (2.2) относительно входных сигналов выходного асинхронного триггера X2, X3.

(2.3)

(2.3)

Полученные выражения (2.3) содержат сигналы X2 и X3 как в правой, так и в левой частях. Это означает, что, подставляя в правую часть уравнений значения сигналов в момент времени tn, в левой части получим их значения в момент времени tn+1.

Допустим, что в исходном состоянии C=0. Тогда согласно (2.3) X2= X3=1, независимо от значения сигнала D. На входах выходного асинхронного RS-триггера D5-D6 будут действовать пассивные логические уровни (единицы) и он будет находиться в режиме хранения. При поступлении синхронизирующего сигнала C=1 из (2.3) получаем:

Данное состояние будет устойчивым, что легко проверить, подставив полученные значения X2 и X3 в (2.3). Таким образом, при появлении синхронизирующего сигнала С=1, на выходах выходного RS триггера будут присутствовать сигналы, определенные информационным уровнем на входе D. При D=1 получается Q=1, при D=0 — Q=0.

Пусть D=1, тогда сразу после прихода синхроимпульса имеем X2=0, X3=1. Подставив значения в (2.3), и, считая, что уровень на входе D может быть любым, находим:

Таким образом, после прихода синхроимпульса C=1 состояние выходного асинхронного RS-триггера становится нечувствительным к изменениям

сигнала на информационном входе D.

Для следующего переключения триггера необходимо подать C=0, при этом вентили D2, D3 устанавливают сигналы на своих выходах X2= X3=1, переводя выходной RS-триггер в режим хранения ранее записанной информации. Фронтом следующего импульса синхронизации триггер будет переведен в новое состояние, определяемое значением на информационном входе D.

Рассмотренный триггер является триггером с прямым динамическим управлением (принимает информацию по фронту синхросигнала). На практике в него вводят дополнительно асинхронные входы предустановки  и

и  ,

,

которые имеют приоритет над информационным входом D.

Т-триггер (от английского Toggle – опрокидываться, кувыркаться) имеет только тактовый вход Т и меняет свое состояние на противоположное по фронту или срезу каждого нового тактового импульса (рис. 2.28). На рисунке показано УГО Т-триггера и как можно выполнить Т-триггер на базе RS- или D-триггеров с динамическим управлением. Каждый раз по фронту сигнала Т изменяется уровень напряжения на выходе Q. Частота изменения потенциала на выходе Т-триггера в два раза меньше частоты импульсов на его тактовом входе. Это свойство Т-триггера используется при построении двоичных счетчиков, а Т-триггер называют также счетным триггером.

Рисунок 2.28 — Cчетный триггер, синхронизируемый фронтом и временные диаграммы его работы

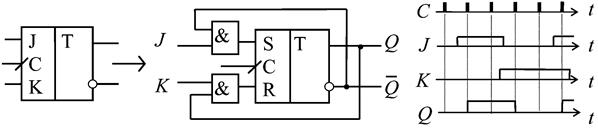

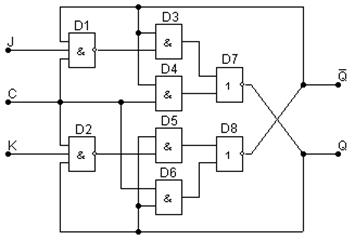

JK-триггер выполняет наиболее универсальные функции (J – Jerk – резкое движение, толчок; K – Kill – ликвидировать). Он строится на базе RS-триггера (рис. 2.29), но, в отличие от него, в JK-триггере устранено запрещенное состояние при J=K=1. При совпадении логических единиц на информационных входах J и K он работает как счетный (режим переключения), т.е. меняет свое состояние на противоположное при каждом новом такте. Логическая 1 на входе J устанавливает триггер в состояние единицы (режим записи 1, установка), логическая 1 на входе К переводит триггер в состояние логического нуля (режим записи 0, сброс) при наличии тактирования. При наличии логических нулей на входах J и К тактовый импульс не меняет состояние триггера (режим хранения). Во избежание режима генерации здесь требуется применять RS-триггер двухступенчатого типа или с динамическим управлением (рис. 2.30). Все работоспособные триггеры JK-типа имеют динамическое управление (переключаются по фронту или срезу синхроимпульса).

Рисунок 2.30 — JK-триггер с динамическим синхровходом (тактируемый фронтом СИ)

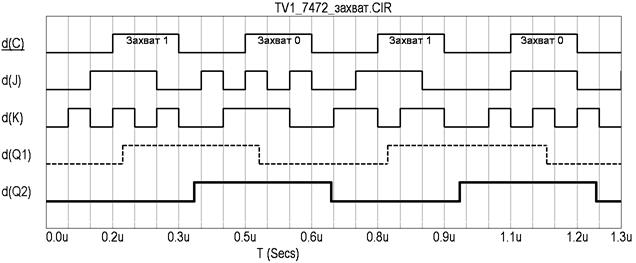

Синтез JK-триггера (Master-slave), запоминающего состояние J и K входов при высоком уровне синхроимпульса и меняющий состояние на выходе по отрицательному перепаду синхроимпульса (переход из высокого в низкое состояние).

Синтез JK-триггера (Master-slave), запоминающего состояние J и K входов при высоком уровне синхроимпульса и меняющий состояние на выходе по отрицательному перепаду синхроимпульса (переход из высокого в низкое состояние).

Схема синтезированного двухтактного триггера представлена на рис. 2.32.

Предназначен для использования при управлении короткими импульсами (имеется в виду длительность единичного состояния) со стороны тактового входа. В противном случае при изменении состояния информационных входов во время высокого уровня синхроимпульса, в первом (Master) RS-триггере может быть защелкнута промежуточная информация, а не непосредственно предшествующая спаду синхроимпульса (см. граф переходов синтезированного триггера). Данное явление носит название захвата нуля и захвата единицы [1, 2] и иллюстрируется рис. 2.33.

Рисунок 2.32 — Синхронный двухтактный JK-триггер, меняющий состояние выхода

по срезу (заднему фронту) синхроимпульса, синтезированный в соответствии с рис. 2.31

Рисунок 2.33 — Явления захвата нулей и единиц в двухступенчатом JK-триггере

Для того чтобы информация менялась на выходе в соответствии с сигналами на информационных входах по заднему (переднему) фронту (а точнее в течение короткого временного интервала, следующего за фронтом) надо изменить граф переходов, а, следовательно и принципиальную схему JK-триггера (рис. 2.34, есть задания в л.р. 8 сем).

Для того чтобы информация менялась на выходе в соответствии с сигналами на информационных входах по заднему (переднему) фронту (а точнее в течение короткого временного интервала, следующего за фронтом) надо изменить граф переходов, а, следовательно и принципиальную схему JK-триггера (рис. 2.34, есть задания в л.р. 8 сем).

JK-триггер, устанавливающийся в соответствии с управляющими сигналами на J и K входах по отрицательному перепаду синхроимпульса (переход из низкого в высокое состояние).

Синтез принципиальной схемы в соответствии с графом переходов рис. 2.34 после некоторых упрощений приводит к схеме 6-элементного JK-триггера. Структура 6-элементного JK-триггера, срабатывающего по фронту синхроимпульса и имеющего инверсный информационный вход K (ТВ15, XXXX109A) приведена ниже на рисунке 2.38.

Схема реального двухступенчатого JK-триггера со входами предустановки и логикой на входе 555ТВ1 (7472) приведена на рис. 2.35. За исключением наличия установочных входов, и логики на информационных входах J и K, ее работа аналогична схеме рис. 2.32 со свойственными недостатками, состоящими в вышеописанных явлениях захвата нулей и единиц.

Схема реального двухступенчатого JK-триггера со входами предустановки и логикой на входе 555ТВ1 (7472) приведена на рис. 2.35. За исключением наличия установочных входов, и логики на информационных входах J и K, ее работа аналогична схеме рис. 2.32 со свойственными недостатками, состоящими в вышеописанных явлениях захвата нулей и единиц.

Данный триггер из-за рассмотренного недостатка считается устаревшим, новые разновидности свободны от захватов и по существу изменяют состояние в соответствии с сигналами на J и K информационных входах по срезу (фронту) синхросигнала.

Одной из таких структур является схема триггера, использующая внутренние задержки составляющих его логических элементов (рис. 2.36).

Функционирование одноступенчатого триггера с внутренней задержкой (рис. 2.36, а) можно рассмотреть с помощью временных диаграмм (рис. 2.36, б).

Рассмотрим только счетный режим, т. к. процесс переключения по информационным синхронным входам (J, K) аналогичен для любых их комбинаций. Работа же входов сброса и установки рассмотрена ранее. Так как в счетном режиме J=K=1, соответствующие входы не влияют на работу элементов D1 и D2. Исходное состояние триггера примем нулевым. Поскольку схема симметрична, достаточно рассмотреть только один процесс переключения (из нуля в единицу, см. рис. 2.36, б).

а б

Рисунок 2.36 — JK-триггер с внутренними задержками

Работоспособность триггера обеспечивается только при условии tзд1,2>2×tзд3,4,5,6+ tзд7,8 (задержки вентилей D1 и D2 превышают суммарную задержку вентилей «И» и «ИЛИ-НE»), которое и отражено на временных диаграммах. Как видно из диаграмм, триггер переключается по отрицательному перепаду тактирующего сигнала. По такой схеме с добавлением входов (входа) предварительной установки строятся триггеры ТВ6 (74LS107), ТВ9 (74LS112), ТВ10 (74LS113), ТВ11 (74LS114). На рис. 2.37 показана внутренняя структура триггера ТВ9.

Также распространены шестиэлементные JK-триггеры с управлением фронтом. Принцип работы шестиэлементных триггеров рассмотрен ранее, приведем лишь внутреннюю структуру триггера ТВ15 (74LS109), использующего этот вариант построения (рис. 2.38).

Рисунок 2.37 — JK-триггер ТВ9 Рисунок 2.38 — JK-триггер ТВ15

Сводная карта всех триггеров-примитивов и ТТЛ-триггеров (которые также можно найти в системе моделирования Micro-CAP 9, 10) приведена на рис. 2.39. Триггеры серий КМОП и ЭСЛ представлены на рис. 2.40.

Рисунок 2.39 — Разновидности триггеров ТТЛ, имеющиеся в программе Micro-CAP

Рисунок 2.40 — Разновидности триггеров КМОП и ЭСЛ

2.7.1 Взаимные преобразования триггеров

2.8 Счетчики

Счетчиком называется последовательностное устройство, предназначенное для счета входных импульсов и фиксации их числа в двоичном коде.

Понятие «счетчик» является очень широким. К счетчикам относят автоматы, которые под действием входных импульсов переходят из одного состояния в другое, фиксируя тем самым число поступивших на их вход импульсов в том или ином коде.

Специфичной для счетчиков операцией является изменение их содержимого на единицу (возможно и условную). Прибавление такой единицы соответствует операции инкремента, вычитание — операции декремента. Обычно счетчиками выполняются также и другие операции — сброс, установка, параллельная загрузка и пр.

Счетчики строятся на основе N однотипных связанных между собой разрядных схем, каждая из которых в общем случае состоит из триггера и некоторой комбинационной схемы, предназначенной для формирования сигналов управления триггером.

В цифровых схемах счетчики могут выполнять следующие микрооперации над кодовыми словами:

· установка в исходное состояние (запись нулевого кода);

· запись входной информации в параллельной форме;

· хранение информации;

· выдача хранимой информации в параллельной форме;

· инкремент — увеличение хранящегося кодового слова на единицу;

· декремент — уменьшение хранящегося кодового слова на единицу.

2.8.1 Основные параметры и классификация счетчиков

Основным статическим параметром счетчика является модуль счета М, определяющий число возможных состояний счетчика. После поступления на счетчик М входных сигналов начинается новый цикл, повторяющий предыдущий.

Существуют следующие режимы работы счетчика:

· регистрация числа поступивших на счетчик сигналов;

· деление частоты.

В первом режиме результат — содержимое счетчика, во втором режиме выходными сигналами являются импульсы переполнения счетчика.

Основным динамическим параметром для первого режима, определяющим быстродействие счетчика, является время установления выходного кода tуст K — временной интервал между моментом подачи входного сигнала и моментом установления нового кода на выходе. Иногда быстродействие счетчика характеризуется максимальной частотой входных сигналов fma x.

Счетчики могут классифицироваться по многим параметрам. Рассмотрим основные из них.

По значению модуля счета счетчики подразделяют на:

· двоичные, модуль счета которых равен целой степени числа 2 (М=2 n);

· двоично-кодированные, модуль счета которых может принимать любое, не равное целой степени числа 2, значение.

По способу кодирования внутренних состояний различают:

· двоичные счетчики

· счетчики Джонсона

· счетчики с кодом "1 из N" и др.

По направлению счета счетчики подразделяют на:

· суммирующие, выполняющие микрооперацию инкремента над хранящимся кодовым словом;

· вычитающие, выполняющие микрооперацию декремента над хранящимся кодовым словом;

· реверсивные, выполняющие в зависимости от значения управляющего сигнала над хранящимся кодовым словом либо микрооперацию декремента, либо инкремента.

Счетчики строятся из разрядных схем, имеющих межразрядные связи. По способу организации межразрядных связей счетчики делятся на:

· счетчики с последовательным переносом, в которых переключение триггеров разрядных схем осуществляется последовательно один за другим;

· счетчики с параллельным переносом, в которых переключение всех триггеров разрядных схем осуществляется одновременно по сигналу синхронизации;

· счетчики с комбинированным последовательно-параллельным переносом, при котором используются различные комбинации способов

переноса.

По принадлежности к тому или иному классу aвтоматов говорят о синхронных или асинхронных счетчиках (более подробную классификацию по этому признаку не затрагиваем, учитывая реальный состав микросхем счетчиков).

2.8.2 Двоичные счетчики

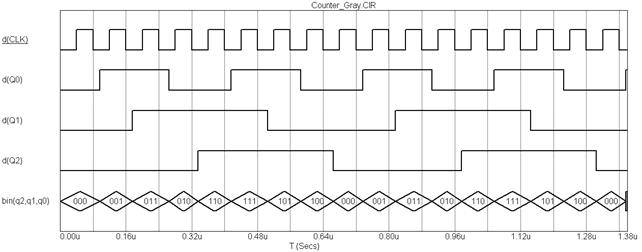

Как и любой автомат, счетчик можно строить на триггерах любого типа, однако удобнее всего использовать для этого триггеры типа Т (счетные) и JK, имеющие при J=К=1 счетный режим (режим Т-триггера).

Состояние счетчика читается по выходам разрядных схем как слово

Q n-1 Qn-2…Q0, входные сигналы поступают на младший разряд счетчика.

Двоичный счетчик — счетчик, имеющий модуль М=2 n, где n – целое число, и естественную последовательность кодов состояний (его состояния отображаются последовательностью двоичных чисел, десятичными эквивалентами которых будут числа 0, 1, 2, 3, М–1; см. табл. 1.1).

Для определения структуры двоичного счетчика рассмотрим последовательность двоичных чисел, ограничившись для простоты 3-разрядным кодом (табл. 2.6).

Таблица 2.6 — Таблица 3-разрядных двоичных чисел

| C | Q2 | Q1 | Q0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

| 1 | 1 | 1 | 1 |

Схему двоичного счетчика можно получить с помощью формального синтеза, однако более наглядным и быстрым является эвристический метод. Таблица истинности двоичного счетчика — последовательность двоичных чисел от нуля до М–1. Наблюдение за разрядами чисел, составляющих таблицу (табл. 2.6), приводит к пониманию структурной схемы двоичного счетчика. Состояния младшего разряда Q0 при просмотре по соответствующему столбцу таблицы показывают чередование нулей и единиц вида 01010101. В следующем разряде наблюдается последовательность пар нулей и единиц вида 00110011... . В третьем разряде образуется последовательность из четверок нулей и единиц 00001111... и т.д. Из этого наблюдения видно, что следующий по старшинству разряд переключается с частотой, в два раза меньшей, чем данный.

Так Q0, соответствующее младшему разряду двоичного числа, изменяет свое значение с приходом каждого импульса синхронизации; Q1 — с приходом каждого второго импульса синхронизации, a Q2 — с приходом каждого четвертого импульса. Данный алгоритм можно легко реализовать, используя асинхронные T-триггеры, причем синхронизацию каждого последующего триггера осуществляют выходным сигналом предыдущего, а переключение первого триггера, формирующего значение Q0 — непосредственно последовательностью синхроимпульсов (рис. 2.41, а). Так как в счетчике значения Q ассоциируются с выходными сигналами соответствующих триггеров, то для получения счетчика с модулем счета М=8 необходимо как минимум три триггера. Временные диаграммы, поясняющие такой алгоритм работы, приведены на рис. 2.41, б.

Представление счетчика цепочкой Т-триггеров справедливо как для суммирующего, так и для вычитающего вариантов, поскольку закономерность по соотношению частот переключения разрядов сохраняется как при просмотре таблицы сверху вниз (прямой счет), так и снизу вверх (обратный счет). Различия при этом состоят в направлении переключения предыдущего разряда, вызывающего переключение следующего. При прямом счете следующий разряд переключается при переходе предыдущего в направлении от 1–0, а при обратном — при переключении 0–1 (см. табл. 2.6). Следовательно, различие между вариантами заключается в разном подключении входов последующих триггеров к выходам предыдущих.

а

б

Рисунок 2.41 — Суммирующий счетчик с последовательным переносом: а — схема;

б — временные диаграммы

Так для получения суммирующего счетчика, последовательно включенные асинхронные T-триггеры должны быть снабжены инверсными динамическими входами (рис. 2.41). Для получения вычитающего счетчика на основе цепочки триггеров с инверсными динамическими входами, необходимо на вход последующего триггера подавать сигнал с инверсного выхода предыдущего

(рис. 2.42).

Если исходные асинхронные T-триггеры снабжены прямыми динамическими входами, то счетчик, собранный по схеме рис. 2.41, а превращается в вычитающий и выполняет микрооперацию декремента. Счетчик же, собранный по схеме рис. 2.42, а, превращается в суммирующий и выполняет микрооперацию инкремента.

Результаты приведенных выше рассуждений можно свести в таблицу (см. табл. 2.7).

а

б

Рисунок 2.42 — Вычитающий счетчик с последовательным переносом: а — схема;

б — временные диаграммы

Таблица 2.7 — Зависимость типа выполняемой микрооперации от вида межразрядных связей и типа синхровхода

| Тип входа Т | Используемый выход | |

| Q |

| |

| Прямой динамический | Декремент | Инкремент |

| Инверсный динамический ¯ | Инкремент | Декремент |

Таким образом, в счетчиках на синхронных Т-триггерах направление счета зависит как от того, какой из выходов используется для синхронизации последующего триггера, так и от типа входа синхронизации. В табл. 2.7 приведены все возможные комбинации соединения триггеров с различными типами входов синхронизации и получаемые при этом виды счетчиков.

Из сказанного также следует, что направление счета счетчика может изменяться (реверсирование) путем изменения вида межразрядных связей. Последнее легко достигается включением в состав каждой разрядной схемы счетчика мультиплексора (например на элементах И-ИЛИ, рис. 2.43), управление которым дает возможность реверсировать счет.

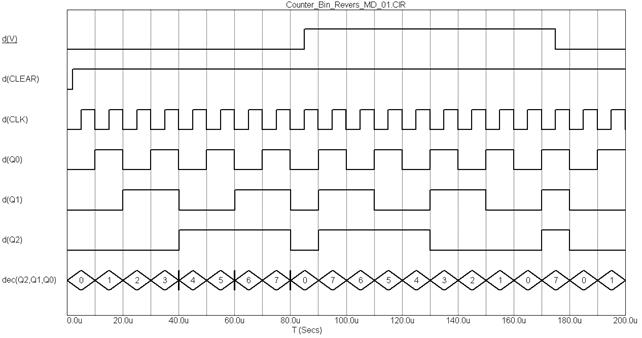

Сигнал на входе V данного счетчика определяет вид межразрядных связей, а, следовательно, и тип получаемого счетчика. Схема и временные диаграммы, поясняющие работу такого счетчика при различных значениях сигнала V, приведены на рис. 2.43.

а

б

Рисунок 2.43 — Реверсивный двоичный счетчик с последовательным переносом: а — схема; б — временные диаграммы

Полученные структуры относятся к асинхронным счетчикам, т. к. в них каждый триггер переключается выходным сигналом предыдущего, и эти переключения происходят не одновременно. Переключение одного триггера за другим есть не что иное, как распространение переноса по разрядам числа при изменении содержимого счетчика. В худшем случае перенос распространяется по всей разрядной сетке от младшего разряда к старшему, т. е для установления нового состояния должны переключиться последовательно все триггеры. Отсюда видно, что время установления кода в асинхронном счетчике удовлетворяет неравенству tycт к £ n × tтр. Другим названием асинхронного счетчика является «последовательный счетчик».

Максимальная частота входных импульсов в режиме деления частоты ограничивается возможностями триггера младшего разряда, т. к. все последующие разряды переключаются с более низкими частотами.

Особенностью последовательных счетчиков является возникновение в переходных процессах ложных состояний из-за задержек переключения триггеров (см. рис. 2.44).

а

б

Рисунок 2.44 — Пример возникновения ложных состояний в асинхронном суммирующем счетчике

На рис. 2.44 показана временная диаграмма работы трехразрядного суммирующего счетчика на триггерах с инверсным динамическим управлением, построенная с учетом задержек переключения триггеров tп тр (частота тактовых сигналов достаточно высока). Читая состояние счетчика Q по потенциалам на выходах триггеров Q2Q1 Q 0 видим, что после состояний 1, 3, 5, 7 появляются ложные состояния 0, 2, 4, 6. Отметим, что ложные состояния проявляются особенно заметно при высокой частоте работы счетчика. Так в случае, показанном на рис. 2.44, период тактовых импульсов, составляет 80 нс, в то время как время переключения триггеров счетчиков составляет 15-20 нс. Опасность воздействия коротких ложных импульсов на последующие цифровые схемы заставляет прибегать при необходимости к стробированию выхода счетчика.

Все рассмотренные выше счетчики являются счетчиками с последовательным переносом, так как переключение каждого последующего триггера может произойти только после переключения предыдущего. Данный тип счетчика отличается простотой внутренней структуры. Однако следствием такой организации является большое время установления выходного кода, которое к тому же не остается постоянным в процессе работы и зависит от конкретного значения его выходного кода. Максимальное значение tуст к наблюдается в случае необходимости переключения всех триггеров счетчика, например при изменении выходного кода со значения 111 на значение 000, или наоборот (см. рис. 2.44, б). Максимально возможное время установления кода определяется соотношением:

(2.4),

(2.4),

где N — число разрядов счетчика; tп тр — время переключения (установления выходного кода) одного триггера счетчика.

Уменьшить время установления выходного кода счетчика можно при условии, что все триггеры его разрядных схем будут переключаться одновременно. Для этого необходимо отказаться от применения асинхронных триггеров в пользу синхронных и сформировать сигналы, регламентирующие требуемый порядок переключения триггеров разрядных схем до прихода импульса синхронизации.

Максимальным быстродействием обладают синхронные счетчики с параллельным переносом, структуру которых можно определить, рассмотрев процессы прибавления единицы к двоичным числам и вычитания ее из них, например:

0 1 1 0 0 1 1 1 0 1 1 0 1 0 0 0

+ 1 – 1

0 1 1 0 1 0 0 0 0 1 1 0 0 1 1 1

Результат всегда отличается от исходного числа только в нескольких младших разрядах, значения которых инвертируются. Для суммирующего счетчика требуется инверсия разрядов до первого разряда, равного логическому нулю, включая и его, а для вычитающего аналогично до разряда, равного логической единице. Таким образом, в суммирующем счетчике должны переключиться все младшие последовательные разряды в единичном состоянии, в вычитающем — все младшие последовательные разряды в нулевом состоянии.

Эти задачи и должны решать счетчики с параллельным переносом. Время установления таких счетчиков не зависит от разрядности счетчика n и равно времени переключения одного триггера:

tycт К=tп тр (2.5).

Структура суммирующего синхронного счетчика с параллельным переносом, реализованного на триггерах с управлением срезом, показана на рис. 2.45, а. Следует отметить, что в данной структуре триггер, формирующий сигнал Q0, по-прежнему остался асинхронным. Поэтому его входной сигнал Tºl.

а

б

Рисунок 2.45 — Суммирующий счетчик с параллельным переносом: а — схема;

б — временные диаграммы работы

Однако если счетчик с последовательным переносом непосредственно после установления нового значения выходного кода готов к следующему переключению, то при реализации параллельного алгоритма для подготовки счетчика к следующему переключению должно пройти некоторое время tпод. Это время необходимо для формирования нового сигнала переноса и определяется временем задержки распространения сигнала через логические элементы И (tпод= t&), использующихся в цепях формирования сигналов переноса. Так как это время всегда меньше времени установления выходного кода одиночного триггера, быстродействие полученного счетчика всегда выше быстродействия счетчика с последовательным переносом.

Следует отметить, что в счетчиках с параллельным переносом направление счета не зависит от того, какой (прямой или инверсный) динамический вход имеют триггеры, составляющие его разрядные схемы. Направление счета определяется исключительно тем, какой (прямой или инверсный) выход триггера используется для формирования сигнала переноса. Так, счетчик, схема которого показана на рис. 2.45, будет суммирующим. Если же для формирования сигнала переноса будут использованы инверсные выходы триггеров разрядных схем, счетчик будет вычитающим (табл. 2.8).

Таблица 2.8 — Зависимость типа операции, реализуемой счетчиком с параллельным

переносом, от вида межразрядных связей

| Сигнал связи триггеров | Операция |

| Q | Инкремент |

| Декремент |

Следовательно, и при использовании параллельного переноса введением в разрядные схемы мультиплексоров на элементах И—ИЛИ можно легко построить реверсивный счетчик.

Схема межразрядной связи для реверсивного счетчика с сигналом V (V=1 — прямой счет, V=0 — обратный счет) показана рис. 2.46.

Рисунок 2.46 — Схема межразрядной связи для реверсивного счетчика с

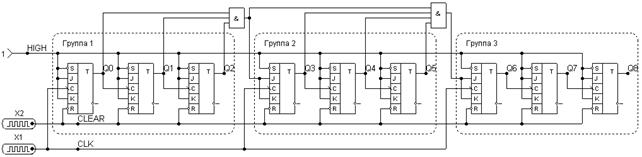

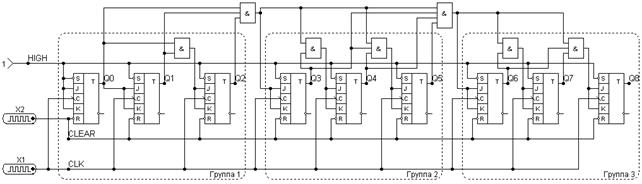

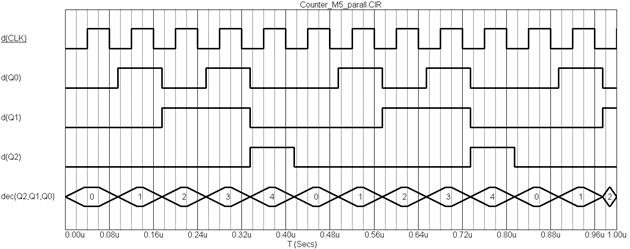

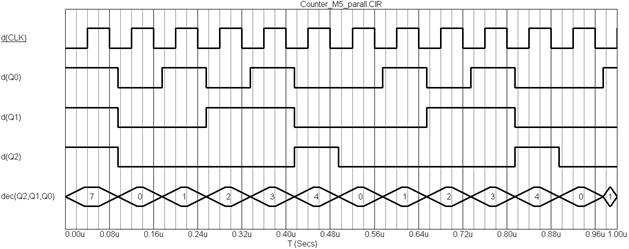

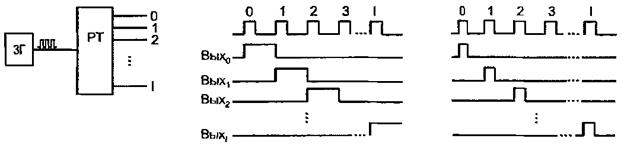

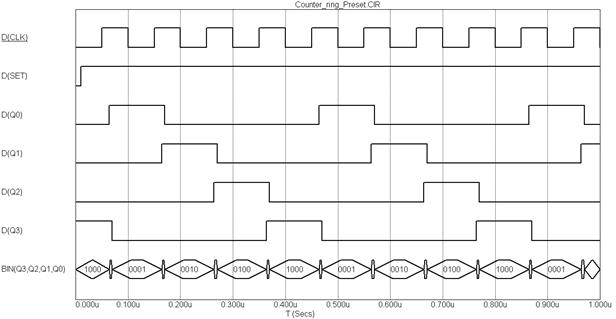

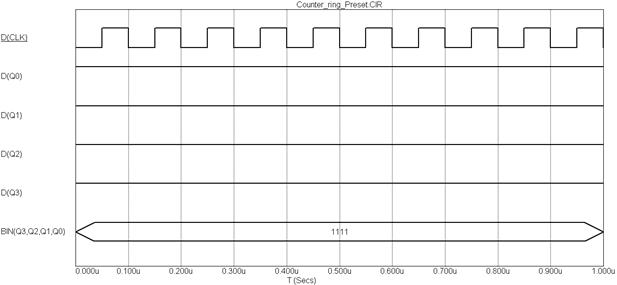

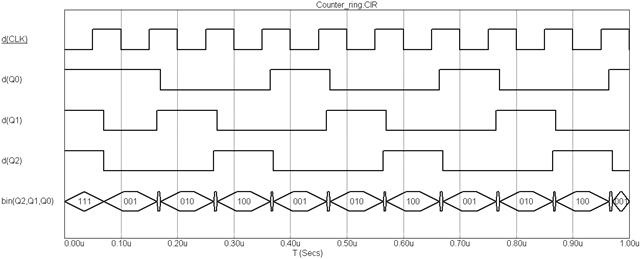

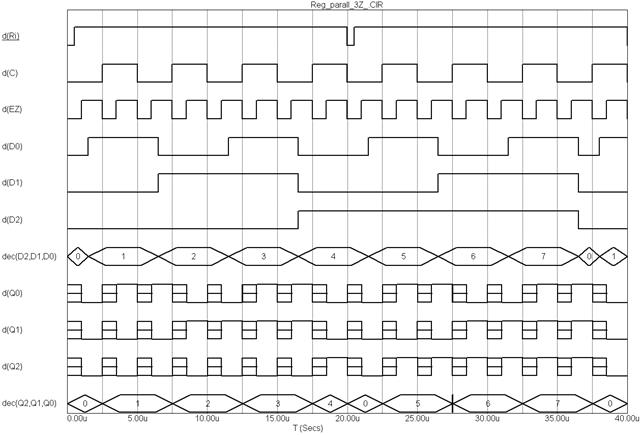

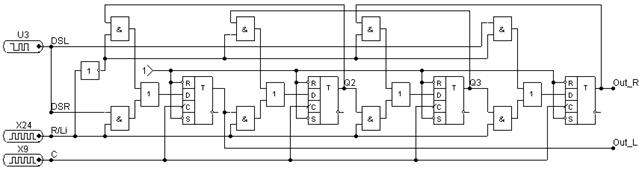

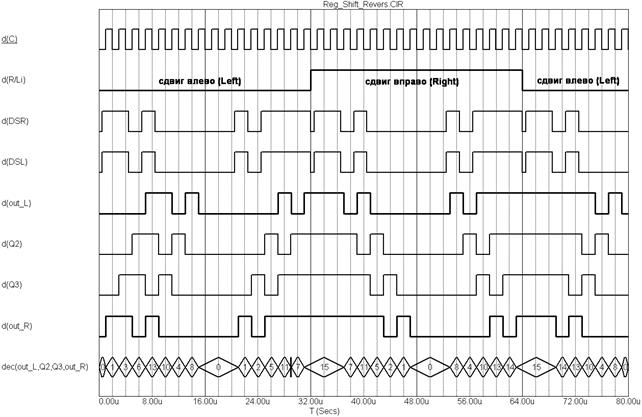

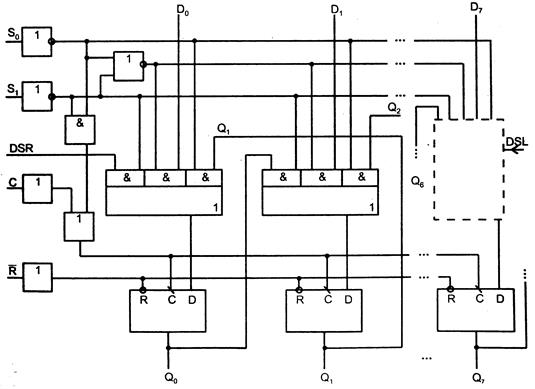

параллельным переносом