Редактирование программой части проекта

Основная циклическая программа располагается в организационном блоке OB1, расположенном в ветви Blocks. Открытие этого блока приведет к запуску утилиты редактора программы.

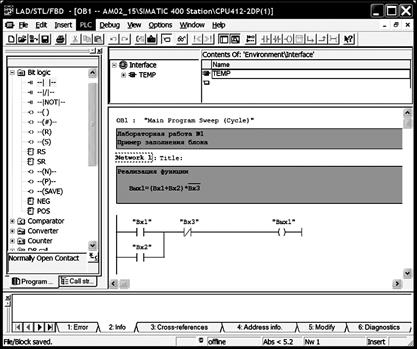

Вид окна утилиты редактора программы при редактировании языка S7 LAD показан на рис. 6.

Рис.6. Вид окна редактора программ

Общее окно программы разбито на четыре части. Центральная часть содержит графические элементы самой программы управления (Network).

Верхняя часть – заголовок блока. В нем указываются временные и локальные переменные блока. Нижняя часть окна предназначена для вывода ошибок и предупреждений. Слева (в некоторых случаях справа) располагается каталог графических элементов языка, разделенных по категориям. Установка элемента языка в Network происходит «перетаскиванием» из каталога с помощью указателя мыши. В качестве дополнительной информации в программе можно указать комментарии к каждому блоку и по всей программе в целом. После установки всех элементов программы необходимо сохранить блок ОВ1.

Загрузка и отладка проекта

Загрузка проекта в контроллер осуществляется командой Download, расположенной в пункте меню PLC. Загрузка должна производится только тогда, когда процессор находится в режиме STOP.

После окончания загрузки, для запуска программы необходимо перевести процессор в состояние RUN.

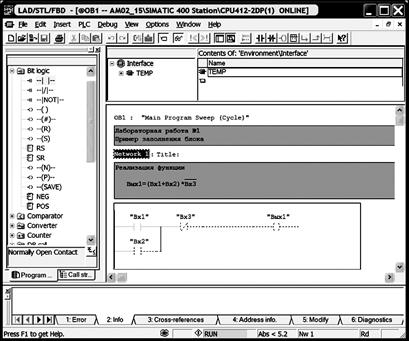

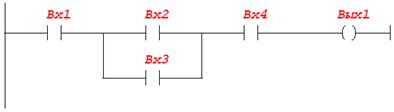

Для визуального просмотра хода выполнения операций в редакторе программ можно включить режим “Monitor” из пункта меню “Debug”. В этом случае производится оперативный обмен данными между Simatic Manager и областью рабочей памяти контроллера. Наличие логической “1” на релейном элементе и протекание тока обозначается в редакторе сплошной линией, логический “0” или отсутствие тока обозначается штриховой линией. Вид окна редактора программ при включенном режиме мониторинга показан на рис. 7.

|

|

|

Состояние входных сигналов Вх1=”1”, Вх2=”0”, Вх3=”1”. Выходной сигнал схемы Вых1=”0”.

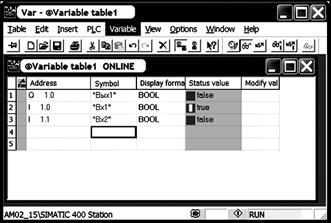

Вторым средством контроля переменных программы является таблица переменных - VAT. Вызов таблицы из редактора программ осуществляется командой Monitor/Modify Variables из меню утилиты – PLC. В Таблице переменных, вид которой представлен на рис. 8, в столбец Address или Symbol заносят адрес или символическое имя переменной, состояние которой необходимо контролировать, после чего включают режим мониторинга (команда Variable → monitor). В полях столбца Status value указывается текущие состояние переменной False – лог “0”, True – лог “1”.

Другим вариантом отладки программы, в случае если контроллер отсутствует, является использование специальной программы эмуляции процессора – PLCSIM. Запуск PLCSIM осуществляется командой Options / Simulate Modules из основного меню Simatic Manager. Вид окна утилиты эмуляции показан на рис.9.

|

|

|

Рис.7. Вид окна редактора программ с включенным режимом мониторинга

Рис.8. Вид окна таблицы переменных с включенным режимом мониторинга

Окна, через которые осуществляется ввод данных и контроль выходных сигналов являются настраиваемыми. Для этого необходимо указать тип памяти, переменные которой необходимо контролировать и адрес ячейки. Тип контролируемой памяти и открытие дополнительных окон контроля осуществляется через меню программы PLCSIM (Insert) или с помощью панели инструментов эмулятора. Режимы работы CPU переключаются в отдельном окне эмулятора.

Для удобства можно настроить окно эмулятора PLCSIM таким образом, чтобы в не зависимости от его активности окно располагалось всегда поверх всех остальных окон. Это действие осуществляется командой меню программы эмуляции View / Always On Top.

Рис.9. Вид окна программы эмуляции модулей контроллера

После загрузки эмулятора все действия по загрузке и мониторингу программы производятся так же, как и при работе с реальным контроллером.

2. Задание на лабораторную работу

Для заданной станции создать проект для реализации логической функции. После загрузки проекта в контроллер проверить правильность выполнения контроллером вычислений путем сравнения результата выполнения с таблицей истинности заданной функции.

|

|

|

Таблица 1

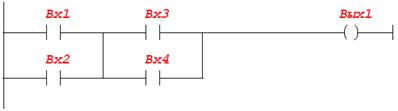

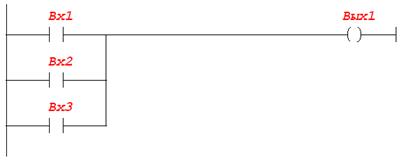

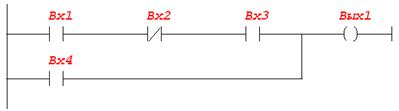

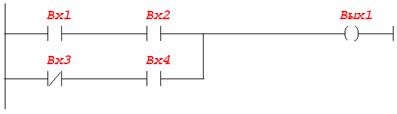

Варианты релейных функций

| Вариант | Функция |

| 1 |

|

| 2 |

|

| 3 |

|

| 4 |

|

| 5 |

|

| 6 |

|

3. Порядок выполнения работы

1. Для заданной релейной схемы составить таблицу истинности.

2. Создать проект для заданной станции с именем «Номер группы – номер варианта» (Например АМ02_6). (Внимание! Проекты имеющих имена отличные от предложенных будут удалены).

3. Для станции, на которой осуществляется выполнение проекта, произвести конфигурирование модулей. Для пустых модулей, расположенных в стойке контроллера, слоды должны оставаться пропущенными.

4. Составить логический блок вычисления заданной функции и заполнить Network в организационном блоке ОВ1.

5. Произвести сброс памяти контроллера. Загрузить проект в контроллер в режиме STOP и перевести контроллер в режим RUN и проверить правильность конфигурирования модулей по ламповым индикаторам лицевой панели CPU.

6. Перевести проект в режим мониторинга, и задавая кнопками пульта входные сигналы в соответствии с таблицей истинности контролировать выходные сигналы. При обнаружении несоответствия произвести поиск ошибок и их устранение.

|

|

|

7. Загрузить эмулятор контроллера - PLCSIM. Проверить работу релейной схемы на эмуляторе.

8. Загрузить программу имитации пульта, подключенного к контроллеру. Проверить правильность работы релейной схемы на пульте-имитаторе. Описание работы пульта-имитатора приведено в приложении.

4. Оформление отчета

Отчет должен содержать:

1. Заданную релейную схему и ее таблицу истинности.

2. Таблицу конфигурирования аппаратуры станции с указание адресации каждого модуля.

3. Программный логический блок с реализацией заданной логической функции.

4. Результаты проверки работы программного блока в соответствии с таблицей истинности.

Лабораторная работа №2

Изучение команд битовой логики языка STEP7 на примере синтеза комбинаторной переключательной схемы

Цель работы: освоить принцип составления схемы релейной логики на языке технологического программирования STEP7 по заданной таблице истинности

1. Общие понятия комбинаторных переключательных схем

Комбинаторная переключательная схема предназначена для преобразования входной комбинации дискретных (двоичных) сигналов в однозначно определенную выходную комбинацию.

Для синтеза комбинаторных переключательных схем используют различные методы. Цель синтеза состоит в том, чтобы составить из соответствующих двоичных элементов оптимальную (с определенной точки зрения) переключательную схему, которая реализовывала бы заранее заданное соотношение между входами и выходами.

Так как выходные сигналы комбинаторной схемы непосредственно зависят от входных сигналов, они могут быть представлены переключательными формулами, которые непосредственно дают всю информацию о поведении системы.

Чаще всего переключательные формулы комбинаторных схем включают в себя три основные логические операции:

- логическое сложение Å - дизъюнкция – логическое ИЛИ;

- логическое умножение Ä - конъюнкция – логическое И;

- отрицание ` - инверсия – логическое НЕ.

Другой формой описания комбинаторных схем является таблица истинности. Наиболее часто ее применяют для описания не очень сложных схем, в которых количество входных комбинаций ограничивается несколькими десятками. В таблице истинности в первых столбцах обычно содержится кодовые слова, соответствующие комбинациям входных переменных, расположенные в порядке роста десятичных эквивалентов. Наиболее просто это делается простановкой отдельных битов в соответствующих столбцах. Для каждого двоичного выходного сигнала предусмотрены свои столбцы, в которых для каждой комбинации входных сигналов содержатся значения 0 или 1 или, если не требуется определенного значения, знаки Æ или d (don’t cure - безразлично).

Преобразование комбинаторной схемы, представленной таблицей истинности в переключательную функцию рассмотрим на примере.

Пример: поведение комбинаторной схемы описывается следующей таблицей:

| Х1 | Х2 | Х3 | Y |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

Для представления в виде переключательной формулы оставим для рассмотрения только те строки таблицы, в которых выходной сигнал Y = 1(т.е. строки 2, 3, 8). Число таких строк будет определять количество операций логического сложения. Каждое слагаемое будет определяться произведением входных сигналов, причем, если входной сигнал в строке равен логическому “0”, то он берется со знаком инверсии, т.е.:

для строки 2:  Ä

Ä  Ä

Ä

для строки 3:  Ä

Ä  Ä

Ä

для строки 8:  Ä

Ä  Ä

Ä

Переключательная формула будет иметь вид:

=

=  Ä

Ä  Ä

Ä  Å

Å  Ä

Ä  Ä

Ä  Å

Å  Ä

Ä  Ä

Ä  .

.

Также используя обратную последовательность можно представить переключательную формулу в виде таблицы истинности, например, может быть получен следующий результат:

| Х1 | Х2 | Х3 | Y |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

| остальные | 0 | ||

После получения переключательной функции, ее можно упростить, воспользовавшись одним из методов [1]. Наиболее распространенным является метод диаграмм Карно [1,2].

Если система имеет несколько выходов, то для каждого выходного сигнала составляется своя переключательная формула.

1. Реализация комбинаторной переключательной схемы на языке LAD

Для реализации комбинаторной переключательной схемы на языке релейной логики следует придерживаться следующих правил:

1. Каждая переключательная функция, реализующая один выходной сигнал переключательной схемы, помещается в отдельном блоке (Network).

2. Каждая дизъюнкция (логическое сложение) образует параллельную цепочку из контактов реле.

3. Каждая конъюнкция образует цепочку последовательно соединенных контактов реле.

4. Входной сигнал в переключательной функции, к которому применена операция отрицания, представляется нормально замкнутым контактом, иначе - нормально разомкнутым.

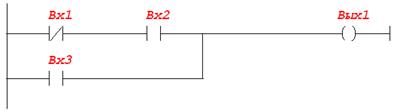

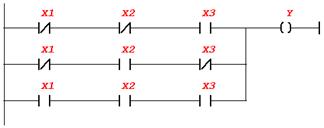

Для приведенной в примере переключательной формулы логический блок будет выглядеть следующим образом (рис.10):

Рис.10. Пример релейной схемы на языке LAD

Реализованный логический блок на языке LAD в среде SIMATIC MANAGER при условии, что адреса входных сигналов Х1= I 0.0; Х2= I 0.1; Х3= I 0.2, а адрес выходного сигнала Y = Q 0.0 приведен на рис.11.

Рис.11. Реализованный логический блок на языке LAD в среде SIMATIC MANAGER

Порядок выполнения работы

1. Создать проект с именем АМYY_ХХ где ХХ – номер варианта, YY – номер группы.

2. По заданной таблице истинности и по переключательной формуле составить схему релейной логики.

3. Заполнить таблицу истинности обозначениями входных и выходных сигналов. Входными и выходными сигналами выбрать соответствующие адреса.

4. Запрограммировать блок OB1, загрузить проект в эмулятор контроллера PLCSIM.

5. C помощью пульта-имитатора в соответствии с таблицей истинности подать входные сигналы и проконтролировать выходные.

6. Сравнить полученный результат с заданными условиями. В случае ошибки произвести исправления и повторить проверку.

7. После отладки на эмуляторе загрузить проект в контроллер и произвести проверку работы релейной схемы с помощью пульта.

8. Сделать выводы по работе.

Содержание отчета

Отчет должен содержать:

- Основные понятия комбинаторной переключательной схемы.

- Разработанную в соответствии с заданием релейную схему на языке LAD.

- Таблицу выходных сигналов для каждой комбинации входных сигналов, полученную с помощью пульта – имитатора.

- Выводы по работе, в которых отразить возможность упрощения полученной релейной схемы и исследование упрощенной схемы на соответствие заданию.

- Задание по вариантам

Спроектировать на языке LAD релейную схему системы имеющей следующую таблицу истинности

1.

|

|

|

|

|

|

|

| 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 | 1 | 1 |

| остальные | 0 | 0 | 0 | |||

2.

|

|

|

|

|

|

| 0 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 0 |

| остальные | 0 | 0 | 0 | ||

3.

|

|

|

|

|

|

|

| 1 | 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 1 | 0 |

| остальные | 0 | 0 | ||||

4

|

|

|

|

|

|

|

|

| 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 |

| остальные | 0 | 0 | 0 | ||||

5.

|

|

|

|

|

|

|

| 0 | 0 | 1 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| остальные | 0 | 0 | 0 | 0 | ||

6.

|

|

|

|

|

|

|

| 0 | 1 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 1 | 1 |

| остальные | 0 | 0 | 0 | |||

7.

|

|

|

|

|

|

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 |

| остальные | 0 | 0 | 0 | ||

Лабораторная работа №3

Использование битов маркерной памяти

Цель работы: изучить основные приемы построения релейных цепочек с обратными связями, используя промежуточные биты маркерной памяти

1. Общие сведения об использовании маркерной памяти

Область маркерной памяти расположена в системной области памяти процессора и доступна как для записи, так и для чтения. Элементы маркерной памяти предназначены для хранения промежуточных результатов вычислений и использование этих результатов в дальнейшем.

Результат вычисления, выведенный на катушку маркерной памяти, помещается в нее сразу и становится доступным для считывания уже в следующей строке. В релейной логике STEP 7 биты маркерной памяти используются одновременно для вывода результата на катушки реле и для ввода значений с контактов этих катушек.

Основное назначение битов маркерной памяти:

· сохранять промежуточный результат при разбиении длинных релейных цепочек или в некоторых команд;

· организовывать обратные связи или проверки условий в тактируемых схемах (в многотактных схемах).

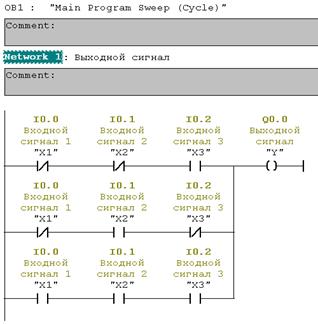

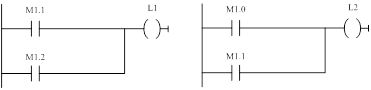

Например, на рис.12 показан вариант сохранения и использования промежуточного результата при разбиении длинной релейной цепочки.

Рис.12. Разбиение длинной релейной цепочки на короткие цепочка: а) исходная схема; б) после разбиения на три цепочки

Разбиение релейной схемы на ряд более коротких схем улучшает читабельность схемы и её лучшее понимание.

Вторым назначением маркерных битов в релейных схемах служит организация обратной связи для хранения результата.

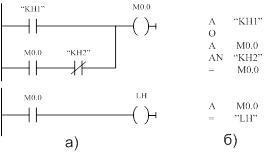

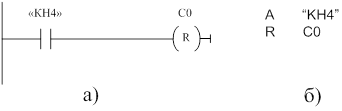

Например, на рис.13 приведен пример, в котором релейная схема реализует запоминание нажатия на кнопку «КН1». Сброс памяти осуществляется при нажатии на кнопку «КН2». Вывод результата осуществляется на катушку реле LH.

При нажатии на кнопку «КН1» катушка реле М0.0 принимает единичное значение, а контакт этой катушки через замкнутый контакт кнопки «КН1» «подхватывает» свою же катушку и не дает ей обесточится, даже если кнопка «КН1» отпускается. При нажатии на кнопку «КН2» цепь подхвата разрывается и реле выключается.

Рис.13. Релейная схема для запоминания нажатий на кнопку «КН1»: а) на языке LAD; б) на языке STL

Возможность реализации обратных связей позволяет реализовывать релейные схемы включения оборудования в строго определенной последовательности. Каждый следующий механизм оборудования может быть включен только после отработки действий предыдущим и формировании требуемых условий включения.

2. Задание на выполнение лабораторной работы

По заданию своего варианта составить релейную схему реализующую возможность последовательного включения выходных состояний. Каждое следующее выходное состояние реализуется только после того как будет реализовано предыдущее. Первое состояние реализуется всегда. Релейную схему разработать на языках LAD и STL.

3. Пример выполнения задания

Дана таблица истинности для последовательной реализации состояний.

Таблица 2

Таблица истинности для примера последовательной реализации состояний

| № состояния | К1 | К2 | К3 | L1 | L2 |

| 1 | 1 | 0 | 1 | 0 | 1 |

| 2 | 0 | 0 | 1 | 1 | 1 |

| 3 | 0 | 1 | 1 | 1 | 0 |

| 4 | 0 | 1 | 0 | 0 | 0 |

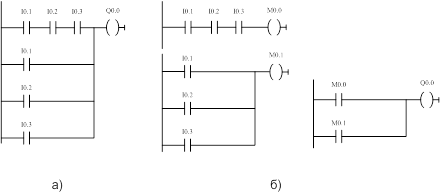

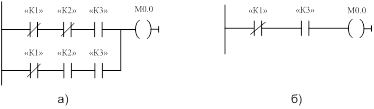

Так как выходных сигнала два (L1 и L2) то система будет содержать два блока реализации этих состояний. Для реализации Для реализации состояния выходного сигнала L1 релейная схема приведена на рис.14.

Рис.14. Схема реализации состояния сигнала L1: а) полная схема; б) после упрощения

Релейная схема реализации состояния сигнала L2 приведена на рис.15.

Рис.15. Схема реализации состояния сигнала L2: а) полная схема; б) упрощенная схема

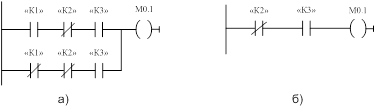

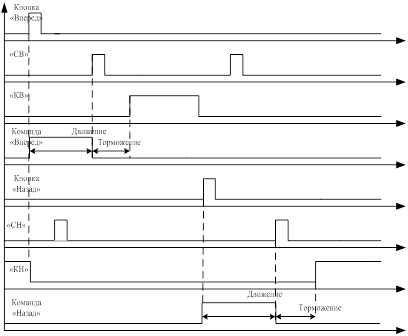

Промежуточные результаты состояний L1 и L2 были сохранены соответственно в маркерной области памяти M0.0 и М0.1. Реализация последовательности шагов по заданным входным сигналам приведена на рис.16.

Так как включение первого шага разрешено всегда, то маркер М1.0 взводится когда выполняется первая комбинация, т.е. L1=0, L2=1, после чего маркер М1.0 встает на самоподхват.

Условие второго шага (рис.5,б) формируется тогда, когда был выполнен первый (проверка маркера М1.0) и сформировалась входная комбинация при которой L1=1, L2=1. Формирование маркера выполнения второго шага (т.е. М1.1=1) сбрасывает первый шаг (М1.0=0) и формирует цепочку самоподхвата.

Условие третьего шага формируется в случае формирования входной комбинации L1=1 и L2=0 и при включенном втором шаге. Установленный в «1» маркер М1.2 разрывает цепь обратной связи второго шага и устанавливает цепь самоподхвата.

Рис.16. Реализация последовательности включения шагов: схемы а)-г) соответственно для шагов 1-4

По аналогии, цепь четвертого шага формируется при L1=0 и L2=0 и наличии условия выполнения третьего шага. Реализация четвертого шага М1.3 разрывает цепь самоподхвата в третьем шаге и устанавливает в четвертом.

Так как первый шаг по условию может выполняться всегда в любой момент, то в обратные связи (цепи самоподхвата) всех шагов введено условие сброса шага, если формируется первый шаг.

Таким образом, задача последовательной реализации состояний свелась к комбинаторной задаче, где входными сигналами являются промежуточные маркера реализации состояний, а выходными сигналами - заданная последовательность без учета необходимости последовательной реализации. Таблица истинности для такой задачи будет выглядеть следующим образом.

Таблица 3

Таблица истинности получившейся комбинаторной задачи

| M1.0 | M1.1 | M1.2 | M1.3 | L1 | L2 |

| 1 | 0 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 |

Релейные схемы, реализующие полученную таблицу истинности приведены на рис.17.

Рис.17. Релейная схема реализации выходных сигналов

4. Порядок выполнения работы

1. Для лабораторной работы создать новый проект, провести конфигурирование аппаратуры контроллера на лабораторном стенде и записать проект на диск.

2. Заполнить таблицу символов, составить релейную схему по номеру варианта. Для задания использовать таблицу истинности из варианта лабораторной работы №2.

3. Запустить последовательно эмулятор контроллера PLCSIM и модель пульта-имитатора.

4. Загрузить проект в эмулятор и с помощью пульта-имитатора проверить правильность работы релейной схемы.

5. Перенести проект в реальный контроллер и проверить работоспособность программы и выполнение шагов.

5. Оформление отчета

Отчет должен содержать:

1. Заданную таблицу истинности.

2. Релейную схему реализации последовательной реализации шагов на языках LAD и STL

3. Пояснение к каждой цепочки релейной схемы реализации шага.

Лабораторная работа №4

Синтез релейной схемы с использованием катушек с памятью

1. Общие сведения о катушках с памятью

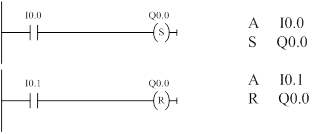

В отличие от обычной катушки реле катушка с памятью может сохранять свое состояние и при отключение сигнала на её входе. Катушка с памятью имеет два вида входов: вход установки (S - set) и вход сброса (R – reset). Состояние катушки определяется тем, на какой вход был подан сигнал. При подаче сигнала на вход установки (S) бит памяти, определяющий состояние катушки устанавливается в единицу, при подаче сигнала на вход сброса (R) происходит его сброс. Изменение состояния выходного бита происходит по переднему фронту входного сигнала. В качестве выходного бита памяти могут быть использованы как биты маркерной памяти, так и памяти выходного образа процесса.

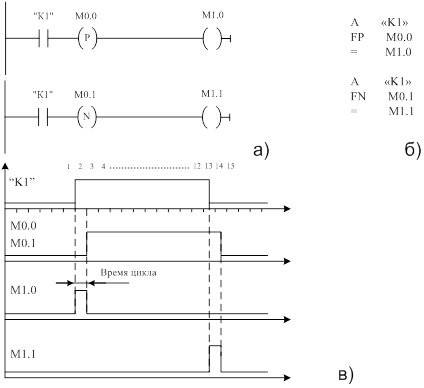

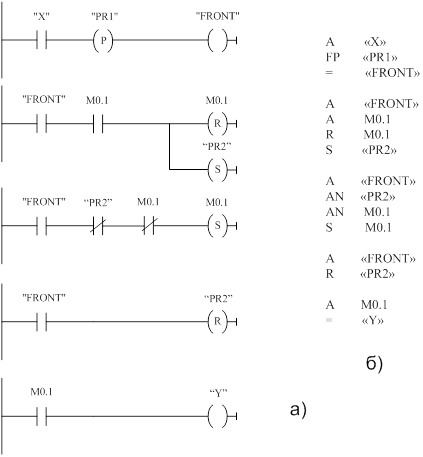

На рис.18,а показана релейная схема использование катушки с памятью.

В качестве входных сигналов используется сигналы с модуля дискретного ввода с адресами I0.0 и I0.1, а в качестве выходного сигнала катушки сигнал на модуль дискретного вывода Q0.0. На рис.18,б показана временная диаграмма включения катушки. На рис.18,в листинг программы реализации катушки с памятью на языке STL.

Из диаграммы видно, что по переднему фронту сигнала I0.0 бит Q0.0 устанавливается в 1 (взводится), а по переднему фронту сигнала I0.1 устанавливается в 0 (сбрасывается). При одновременной подаче сигналов на вход сброса и вход установки выходной сигнал катушки устанавливается в состояние логического нуля, т.е. приоритетной является команда сброса.

а) в)

б)

б)

Рис.18. Релейная схема (a), листинг на языке STL (в) и временная диаграмма работы катушек с памятью (б)

6. Назначение и применение катушек с памятью

Основное назначение катушек с памятью реализовывать комбинаторные схемы, состояние которых изменяется в момент изменения состояния входной цепочки. Причем в схеме должны быть реализованы как минимум две цепочки, одна на включение, а другая на отключение. Типовым примером использование катушек с памятью является управление каким-либо механизмом перемещения.

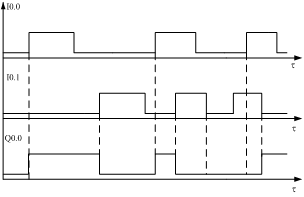

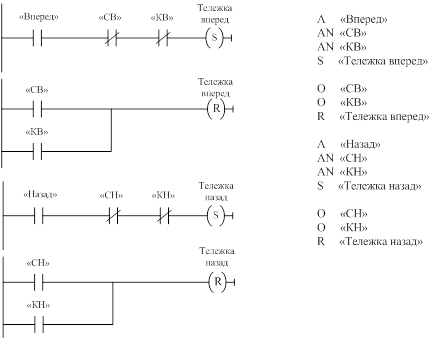

Например, на рис.19 показан механизм перемещения слябов со склада до рольганга (так называемая слябовая тележка) управление которой происходит по нажатию двух кнопок на посту оператора: кнопка «вперед» к рольгангу, кнопка «назад» на склад.

Рис.19. Структурная схема управления механизмом перемещения слябов – слябововой тележкой

Ограничение движения осуществляется путевыми выключателями (обычно фотоэлектрическими или ультразвуковыми): «стоп вперед – СВ» и «стоп назад – СН». Их кратковременное замыкание должно приводит к отключению сигнала управления, подающегося на электродвигатель тележки и тележка, пройдя по инерции еще, какой-то заранее определенный путь останавливается. Конечное положение тележки контролируется концевыми «вперед – КВ» и «назад – КН». Наличие пути остановки (который может составлять от 1 до 3 метров) делает использование только концевых выключателей проблематичным, из-за ограниченного их хода (обычно от 1 до 15 см).

На рис.20 показана релейная схема управления механизмом перемещения и листинг программы на языке STL. На рис. 21 приведена часть временной диаграммы её работы.

Срабатывание путевого выключателя «стоп назад – СН» при движении тележки от склада к рольгангу и «стоп вперед – СВ» при движении от рольганга к складу, объясняется прохождением тележки через них (см. рис.19). Не смотря на это включение этих путевых выключателей не влияет на движение тележки.

Также использование катушек с памятью позволяет реализовывать заданную последовательность включений механизмов. Например, для примера приведенного в лабораторной работе №3 релейная схема с использованием катушек с памятью выглядит следующим образом (см. рис.22).

Рис.20. Релейная схема и листинг программы на языке STL программы управления работой тележки

7. Задание на лабораторную работу

1. Реализовать задание лабораторной работы №3 с использованием катушек с памятью. Проверить правильность работы релейной схемы на контроллере с помощью пульта имитатора.

2. Реализовать релейную схему примера управления движением тележки. Проверить правильность работы с помощью пульта-имитатора или модели объекта. Порядок работы с пультом-имитатором и моделью слябовой тележки смотри в приложении 1 и 2 соответственно. Построить полную диаграмму работы схемы управления тележкой.

3. Модифицировать схему управления тележкой для исключения одновременного формирования команд управления «Вперед» и «Назад».

Рис.21. Часть временной диаграммы работы схемы управления слябовой тележкой

8. Порядок выполнения работы

Лабораторная работа выполняется в следующем порядке:

1) Создать проект, заполнить конфигурацию станции и сохранить созданный проект на диск.

2) Для выполнения первого задания заполнить таблицу символов в соответствии с программой рис.22, в редакторе программ реализовать релейную схему.

3) Запустить программу эмулятора PLCSIM, пульт-имитатор и создать соединение. Загрузить программу в режиме STOP, перевести в режим RUN и проверить соответствие работы программы таблице истинности.

4) Перенести проект на реальный контроллер и проверить работу релейной схемы с помощью пульта.

5) Для выполнения второго задания создать новый проект, в который скопировать конфигурацию оборудования из предыдущего. Заполнить таблицу символов для программы управления тележкой. Адреса устройств и работа с моделью тележки описана в прил.2. В редакторе программ реализовать релейную схему управления тележкой. Сохранить проект на диск.

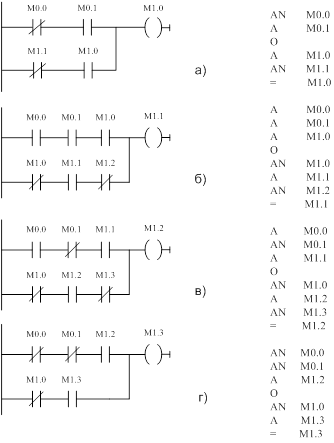

Рис.22. Релейная схема на LAD а) и листинг программы на STL б) реализации последовательного включения шагов

6) Запустить программу эмулятора PLCSIM, пульт-имитатор и создать соединение. Загрузить программу в режиме STOP, перевести в режим RUN и построить диаграмму работы системы управления слябовой тележкой.

7) Выгрузить пульт-имитатор и запустить программу модели слябовой тележки. Проверить работу программы на модели.

8) Внести исправления в программу управления слябовой тележки для исключения ситуаций одновременного формирования двух команд «Вперед» и «Назад» и реализовать управление подсветкой кнопок управления пульта.

9. Оформление отчета

Отчет по лабораторной работе должен содержать:

9) Краткие свеления о работе катушек с памятью

10) Релейные схемы последовательного включения исполнительных устройств и управления слябовой тележкой.

11) Временную диаграмму работы системы управления слябовой тележкой.

Лабораторная работа №5

Изучение команд выделения фронта

Цель работы: изучить работу команд выделения фронта, изучить принцип реализации многотактных релейных схемы с использованием команд выделения фронта

1. Общие сведения о командах выделения фронта

В некоторых случаях выполнение логической операции (включение или отключение катушки реле) должно происходить не по установки требуемого состояния входных сигналов, а по факту изменения их состояния.

Момент времени, в который происходит изменение состояния сигнала, называется фронтом сигнала: изменение с 0 на 1 - передний фронд (или положительный positive); изменение с 1 на 0 - задний фронт (или отрицательный negative).

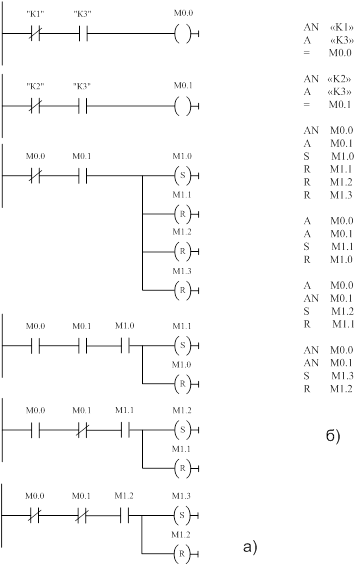

Для выделения фронта команды битовой логики содержат специальный катушки: катушка –(Р)- для выделения переднего фронта; катушка –( N)- для выделения заднего. Пример программы выделения переднего и заднего фронта входного сигнала и временная диаграмма состояния битов показана на рис.23.

Рис.23. Пример программы выделения переднего и заднего фронтов сигнала (а –LAD; б – STL) и временная диаграмма состояния используемых битов в)

Из диаграммы работы команд выделения фронта видно, что сигнал фронта (биты М1.0 и М1.1) формируется на время равное времени цикла выполнения программы. Промежуточные маркера полностью повторяют состояние входного сигнала сдвинутого во времени на один выполнения программы.

Рассмотрим алгоритм работы процессора при выделении переднего фронта.

Сначала (обозначен как цикл сканирования 1) состояния и входа К1, и маркера фронта М0.0 соответствуют уровню лог. "0". Маркер импульса М1.0 также сброшен, т.е. уровень его сигнала равен лог. "0".

На 2-ом цикле сканирования состояние входа К1 изменяется с "0" на "1". CPU обнаруживает это изменение при сравнении текущего значения RLO с состоянием маркера М0.0. Если К1 равен "1", а маркер М0.0 равен "0, то значение маркера фронта М1.0 устанавливается "1".

На 3-ем цикле сканирования маркер М0.0 устанавливается значению, равному значению входного сигнала К1 в предыдущий цикл сканирования т.е. «1». При сравнении текущего значения RLO с состоянием маркера М0.0 CPU обнаруживает, что они имеют один уровень. Поэтому он устанавливает для маркера фронта М1.0 значение "0".

С 4-ого по 12-ый цикл сканирования входной сигнал К1 равен «1», маркер М0.0 следует за этим сигналом и также равен «1». Значение маркера фронта М1.0 установлено «0».

На 13-ом цикле сканирования входной сигнал К1 устанавливается в «0», а маркер М0.0 содержит предыдущее значение входного сигнала и равен «1» до 14-ого цикла. Хотя значение входного сигнала и маркера М0.0 не равны команда выделения переднего фронта никак не реагирует на это изменение. (На такое состояние реагирует команда выделения заднего фронта). Поэтому значение маркера фронта М0.1 остается равным «1».

На 15-ом цикле восстанавливается исходное состояние рассматриваемых битов и в дальнейшем опять может быть выделен передний фронт.

Так как промежуточные маркера выделения фронта используются для хранения предыдущего состояния входного сигнала, то для правильного выполнения команды выделения фронта они должны использоваться в программе только один раз.

Основное назначение команд выделения фронта в битовой логике реализация релейных многотактных схем.

10. Основные понятия многотактной схемы

Если выходные состояния релейной схемы зависят не только от входных состояний (как в комбинаторной схеме), но и от предыдущего состояния релейной схемы, то такую схему называют многотактной.

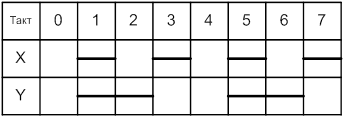

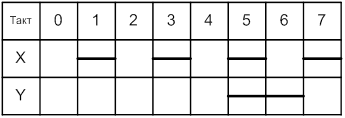

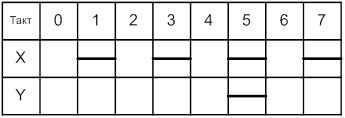

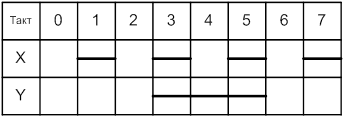

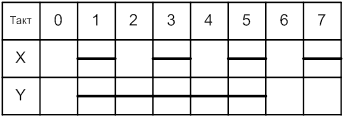

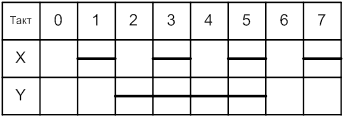

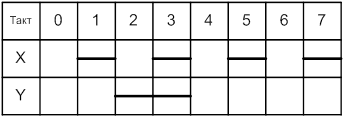

Обычно работу многотактной схемы представляют в виде таблицы включений, в которой состояния входных и выходных сигналов отображается во времени и разбивается на такты. Например, на рис.24 приведена таблица включений релейной схемы с одним входом и одним выходом. Состояние выхода меняется на противоположное на каждом такте при изменении входного сигнала с лог. «0» на «1».

Рис.24. Пример таблицы включений многотактной схемы

Существует несколько методов реализации многотактных схем. Во всех них предполагается, что в релейной схеме будет использоваться элемент памяти, в котором происходит запоминание переднего или заднего фронта входного сигнала или их логической комбинации.

Например, для приведенной таблицы включений реализация на языках LAD и STL приведена на рис.25.

11. Задание на лабораторную работу

1. Изучить работу катушек с памятью. Реализовать программу многотактной схемы (рис.23). По результату работы программы построить таблицу включений.

2. По заданной таблице включений разработать многотактную схему, проверить её работу путем экспериментального определения таблицы включений и сравнить её с заданной.

12. Порядок выполнения работы

1. Создать новый проект. Заполнить конфигурацию станции, таблицу символов и сохранить созданный проект на диск.

2. Реализовать многотактную схему по рис.25 и экспериментально, с использованием эмулятора PLCSIM и пульта-имитатора, определить таблицу (диаграмму включений). Сравнить полученную таблицу включений с исходной (рис.24).

3. Разработать релейную схему по заданной таблице включений. Реализовать её в том же проекте. Используя эмулятор PLCSIM и пульт-имитатор определить таблицу включений.

4. Перенести проект в контроллер и проверить его работу с помощью пульта.

Рис.25. Реализация заданной таблице включений на языках LAD (a) и STL (б)

13. Оформление отчета

Отчет по лабораторной работе должен содержать:

12) Краткие сведения о работе катушек выделения фронта и временные диаграммы их работы.

13) Релейные схемы реализации многотактных схем и их таблицы включений.

14. Задание на самостоятельную работу

По заданной таблице включений разработать релейную схему.

Вариант 1

Вариант 2

Вариант 3

Вариант 4

Вариант 5

Вариант 6

Лабораторная работа №6

Изучение команд работы с аккумулятором процессора и адресации данных

Цель работы: изучить возможности обмена данными через аккумуляторы процессора, представление данных в различных форматах, функций обмена и преобразования этих данных в аккумуляторах, адресацию различных типов данных

1. Общие сведения о регистрах аккумуляторов процессора

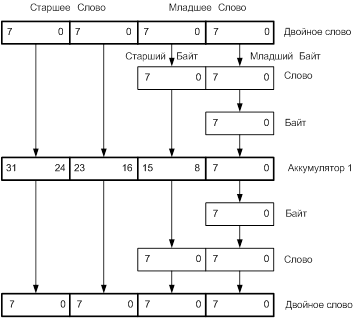

Аккумулятор процессора представляет собой специальный регистр (область памяти) расположенный непосредственно в процессоре и выполняющий функции промежуточного буфера. Размер аккумулятора составляет 32 бита, что соответствует 4-м байтам (по 8 бит) или двум словам (по 16 бит).

В зависимости от расположения слов и байт в аккумуляторе различают младший и старший байт и старшее и младшее слово. На рис.26 показано распределение байт и слов в аккумуляторе.

Рис.26. Распределение слов и байт информации в аккумуляторе

Основными командами на языке STL, которые производят обмен информации через аккумулятор, являются команды загрузки L (load) и выгрузки T (transfer) аккумулятора.

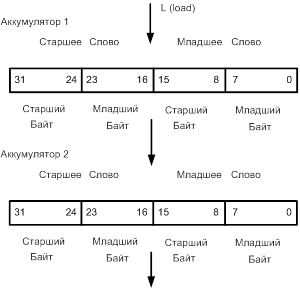

Кроме основного аккумулятора (обычно обозначаемого как АК1 или аккумулятор 1) с которым работают команды загрузки и выгрузки, процессор содержит второй аккумулятор – АК2 (или аккумулятор 2) предназначенный для хранения данных передаваемых из первого аккумулятора.

Команда загрузки (L) записывает (загружает) содержимое своего исходного адреса или константу в аккумулятор 1, сдвигая всю уже содержащуюся в нем информацию в аккумулятор 2. Старое содержимое аккумулятора 2 при этом заменяется.

Команда выгрузки (Т) только копирует содержимое аккумулятора 1 и записывает его в соответствующую целевую (назначенную) область памяти.

На рис.27 показаны изменения, происходящие в аккумуляторах при выполнении команды загрузки.

Рис.27. Передача данных из аккумулятора 1 в аккумулятор 2 при выполнении команды загрузки

Команды загрузки (L) и передачи (Т) аккумулятора можно использовать для обмена данными следующих размеров: байт (В, 8 бит); слово (W, 16 бит); двойное слово (D, 32 бита). Идентификаторы размера (B, W, D) используются для определения объема памяти занимаемых этими данными.

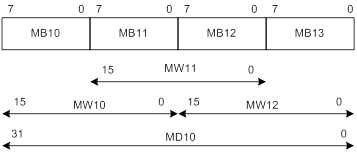

Если данные для обмена с аккумулятором составляет слово или двойное слово, то необходимо знать и четко представлять, как эти данные будут располагаться в области памяти. На рис. 28 показано как располагаются слова и двойные слова в маркерной области.

Адрес памяти, на который ссылаются при загрузки и выгрузки аккумулятора всегда представляет собой адрес байта, в котором расположен самые старшие биты слова или двойного слова. Остальные биты располагаются в следующих за ним байтах памяти. Поэтому при реализации функций работы с аккумуляторами необходимо следить, чтобы не произошло наложение информации при выгрузке информации в соседние ячейки.

Загрузка данных в аккумулятор может происходить из констант и адресов памяти. Для наглядности и удобства программирования загрузка констант может производиться в нескольких форматах. В табл.4 приведены операнды команд загрузки констант в зависимости от их представления. В табл.5 приведены варианты загрузки информации из адресов памяти.

Рис.28. Расположение данных в маркерной области памяти

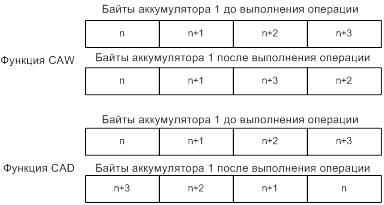

Над данными расположенные в аккумуляторе 1 могут быть проведены команды по перемещению байт и слов информации внутри аккумулятора 1. На рис.29 представлено действие команд по перемещению данных внутри аккумулятора 1: CAW – обмен местами байт младшего слова аккумулятора 1; CAD – обмен местами всех байт в аккумуляторе 1.

Рис.29. Обмен байтов в аккумуляторе АК1

Таблица 4

Операнды команд загрузки констант

| Операнд | Пример команды загрузки константы в аккумулятор | Описание команды |

| ± | L +27 | Загрузка 16-битовой целой константы в АКК1 представленной десятичным числом |

| В#(..,..) | L B#(100,12) L B#(1,10,5,4) | Загрузка двух байт в АКК1 (число 100 в старший байт, число 12 в младший байт) Загрузка четырех байт в АКК1 (число 5 в старший байт младшего слова, число 12 в младший байт младшего слова, 1 и 5 соответственно в старший и младший байт старшего слова) |

| L ‘ABCD’ | Загрузка 4-х байтной символьной константы | |

| 2#... | L 2#10011011 L 2#10011111_10101011 L 2#10101010_10101010 _01010110_10101011 | Загрузка 8-ми, 16-ти и 32-х битовых констант представленных двоичным числом |

| L#... | L L#+5 | Загрузка 32-х битовой целой константы представленную десятичным числом |

| (B,W,D) 16#... | L B#16#EF L W#16#FA6F L DW#16#1FAE56AE | Загрузка 8-ми, 16-ти и 32-х битовых констант представленных шестнадцатеричным числом |

| C#... | L C#100 | Загрузка 16-ти битового счетного значения |

| S5T#... | T S5T#1H23M46S250MS | Загрузка 16-ти битовой константы времени |

| L 1.0E+5 | Загрузка 32-х битовой константы с плавающей точкой |

Таблица 5

Примеры команд загрузки из адресов памяти

| Размерность данных | Пример команды загрузки | Описание команды |

| В | L MB10 L IB0 | Загрузка байта данных из маркерного байта MB10 и байта таблицы входного образа процесса IВ0 |

| W | L MW11 L IW2 L C0 | Загрузка слова данных из маркерного слова MW11, слова таблицы входного образа процесса IW2 и ячейки счетчика С0 |

| D | L MD0 L ID0 | Загрузка двойного слова из маркерной области MD0 и таблицы входного образа процесса ID0 |

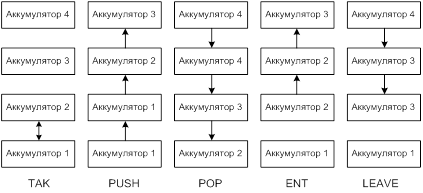

В некоторых типах процессоров дополнительно имеется еще два аккумулятора обозначаемых АК3 и АК4. На рис.30 приведено перемещение информации в аккумуляторах при действии команд TAK, PUSH, POP, ENT, LEAVE.

Рис.30. Действие команд пересылки данных между аккумуляторами процессора

15. Задание на лабораторную работу

Произвести, используя команды языка STL, перемещение данных в аккумуляторах процессора по заданной вариантом схеме. Задание выполнить в двух вариантах: с использованием только команд загрузки и передачи данных между аккумуляторами 1 и 2 и маркерной областью памяти; с использованием (по возможности) только аккумуляторов 1-4 и команд работы с аккумуляторами процессора.

К каждой команде каждого варианта задания составить подробное описание выполняемых действий.

16. Пример выполнения работы.

Произвести перемещения данных между аккумуляторами процессора и маркерным двойным словом по следующей схеме.

Двойное слово: (3с_54_1а_23Н) Þ (АК1=23_1а_54_3сН); (АК2=1а_23_3с_54); ( MW10=3 c_54 H); ( MW12=1а_23Н).

Исходную константу представленную в шестнадцатеричном виде (3с_54_1а_23Н), используя команды обмена с аккумуляторами процессора разместить в аккумуляторе 1 в виде (23_1а_54_3сН), в аккумуляторе 2 в виде (1а_23_3с_54), в маркерное слово MW10 выгрузить часть константы (3c_54H), в маркерное слово MW12 выгрузить часть константы (1а_23Н).

Вариант выполнения 1.

Программа на языке STL с использованием только команд загрузки и передачи с пояснением каждого действия приведена в табл.6.

Таблица 6

Пример первого варианта программы обмена данными с аккумуляторами

| № | Команда на STL | Действия |

| 1 | L DW#16#3C541A23 | АК1= 3 с 541 а 23h |

| 2 | T MD 10 | MD 10=3с541а23 h ( MW 10=3с54 h ; MW 12=1а23 h ) |

| 3 | L MB 13 | AK1=23h |

| 4 | T MB 20 | MB20=23h (MD20=23000000h) |

| 5 | L MB 12 | AK1=1 а h |

| 6 | T MB 21 | MB21=1 а h; (MD20=231 а 0000h) |

| 7 | L MB 11 | АК1=54 h |

| 8 | T MB 22 | MB22= 54 h (MD20=231 а 5400h) |

| 9 | L MB 10 | АК1=3с h |

| 10 | T MB 23 | MВ=3сh ; ( MD20=231 а 54 3с h ) |

| 11 | L MW 10 | AK1=MW10=3 с 54h |

| 12 | T MW 14 | MW14=3 с 54h; ( MD12= 1 а 233 с 54h ) |

| 13 | L MD 12 | АК1= MD12= 1 а 233 с 54h |

| 14 | L MD 20 | АК2=АК1; АК1= 231 а 54 3с h |

Последовательность работы программы следующая.

1) Исходная константа загружается в аккумулятор 1.

2) Аккумулятор АК1 выгружается в маркерное двойное слово MD10. Расположение байт в маркерном двойном слове будет иметь вид: MD 10=3с_54_1а_23 h , в маркерных словах MW 10=3с_54 h ; MW 12=1а_23 h , в маркерных байтах MВ10= 3с h , MB 11=54 h , MB 12=1 ah , MB 13=23 h .

3) Аккумулятор 1 загружается из маркерного байта MВ13.

4) Выгружается АК1 в маркерный байт MВ20, который является старшим байтом двойного слова МD20 (MD 20=23000000 h ).

5) Аккумулятор 1 загружается из маркерного байта MВ12.

6) Выгружается АК1 в маркерный байт MВ21 (MD 20=231 a 0000 h ).

7) Аккумулятор 1 загружается из маркерного байта MВ11.

8)Выгружается АК1 в маркерный байт MВ22 (MD 20=231 a 5400 h ).

9) Аккумулятор 1 загружается из маркерного байта MВ10.

10) Выгружается АК1 в маркерный байт MВ23 (MD 20=231 a 543 ch ).

После выполнения всех этих действий маркерное двойное слово MD20 содержит требуемую в соответствии с заданием последовательность байт.

11, 12) Для того чтобы поменять местами слова маркерного двойного слова MD10 перенесем слово МW10 в слово MW14.

13) Загрузим аккумулятор 1 из двойного слова MD12.

14) Для переноса этих данных в соответствии с заданием в аккумулятор 2 загрузим АК 1 данными из двойного слова MD20.

Вариант выполнения 2.

Программа на языке STL с использованием команды перемещения данных внутри аккумулятора с пояснением каждого действия приведена в табл.7.

Таблица 7

Пример второго варианта программы обмена данными с аккумуляторами

| № | Команда на STL | Действия |

| 1 | L DW#16#3C541A23 | АК1= 3 с _54_1 а _23h |

| 2 | T MD 10 | MD 10=3с_54_1а_23 h ( MW 10=3с_54 h ; MW 12=1а_23 h ) |

| 3 | L MW 10 | AK1=3c_54h |

| 4 | T MW 14 | MW14=3c_54h |

| 5 | L MD 12 | AK1= 1а _ 23 _3c_54h |

| 6 | L MD 10 | АК1=3с_54_1а_23 h AK 2=1а_23_3 c _54 h |

| 7 | CAD | АК1=23 _ 1а _ 54 _ 3с h |

Последовательность работы программы следующая.

1) Загрузка аккумулятора 1 константой 3с_54_1а_23 h .

2) Аккумулятор АК1 выгружается в маркерное двойное слово MD10. Расположение байт в маркерном двойном слове будет иметь вид: MD 10=3с_54_1а_23 h , в маркерных словах MW 10=3с_54 h ; MW 12=1а_23 h .

3) Аккумулятор 1 загружается из маркерного слова MW 10.

4) Выгружается в маркерное слово MW 14.

5) Аккумулятор 1 загружается из маркерного двойного слова MD12=1а_23_3 c _54 h .

6) Значение АК1 переносится в АК2. Аккумулятор 1 загружается из маркерного двойного слова MD10=3с_54_1а_23 h .

7) В аккумуляторе 1 происходит перемещение байт. Результат содержащийся в АК1=23_1а_54_3с h .

17. Содержание отчета

Отчет должен содержать:

6. Операнды команд загрузки констант

7. Два варианта исполнения своего варианта задания с описанием каждого действия по каждой команде.

18. Задание по вариантам

Произвести перемещения данных заданных константой (01_02_03_04h) между аккумуляторами процессора и маркерными словва по следующей схеме:

Вариант 1. (01_02_03_04 h) Þ (АК1=04_03_02_01 h); (АК2=03_04_02_01); (АК3=02_01_04_03 h); (АК4=01_02_03_04 h); ( MW10=02_03 h); ( MW12=01_04 h).

Вариант 2. (01_02_03_04 h) Þ (АК1=01_03_04_02 h); (АК2=02_04_03_01); (АК3=03_01_02_04 h); (АК4=04_02_01_03 h); ( MW10=04_03 h); ( MW12=02_01 h).

Вариант 3. (01_02_03_04 h) Þ (АК1=01_03_04_02 h); (АК2=02_04_03_01); (АК3=03_01_02_04 h); (АК4=04_02_01_03 h); ( MW10=02_03 h); ( MW12=01_04 h).

Вариант 4. (01_02_03_04 h) Þ (АК1=01_04_03_02 h); (АК2=02_03_01_04); (АК3=03_02_04_01 h); (АК4=04_01_02_03 h); ( MW10=04_01 h); ( MW12=02_03 h).

Вариант 5. (01_02_03_04 h) Þ (АК1=01_04_02_03 h); (АК2=02_03_04_01); (АК3=03_02_01_04 h); (АК4=04_01_03_02 h); ( MW10=03_01 h); ( MW12=04_02 h).

Вариант 6. (01_02_03_04 h) Þ (АК1=01_04_03_02 h); (АК2=02_03_01_04); (АК3=03_02_04_01 h); (АК4=04_01_02_03 h); ( MW10=02_04 h); ( MW12=01_03 h).

Лабораторная работа №7

Реализация счетчиков

Цель работы: изучить команды управления счетчиками и основные принципы использования счетных значений

1. Общие сведения о счетчиках языка STEP 7

Счетчики позволяют реализовывать вычислительные задачи по подсчету каких либо событий происходящих в системе. Счетчики могут вести прямой счет (счет по возрастанию - инкрементирование) и обратный счет (счет по убыванию – декрементирование). Счетчики располагаются в системной памяти CPU в области Counter – C.

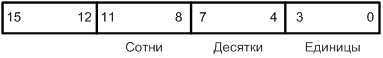

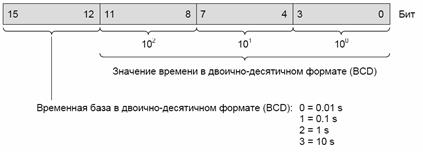

Счетчик занимает ячейку памяти размером 16 бит, которая называется словом счетчика и которая хранит счетное значение в двоично-десятичном формате (BCD) в диапазоне от 000 до 999. Размещение счетного значения в слове счетчика показано на рис.31.

Рис.31. Расположение счетного значения по тетрадам ячейки счетчика

Ячейки памяти счетчиков нумеруются, начиная с нуля до каково-то максимального значения, определяемого типом CPU. Например, CPU 315-2DP содержит 64 счетчика с диапазоном ячеек счетчиков от С0 до С63.

Для управления счетчиками используются следующие команды.

1. Установка счетчика (задание начального счетного значения).

2. Прямой счет.

3. Обратный счет.

4. Сброс счетчика.

5. Чтение состояния счетчика.

6. Чтение числового значения счетчика в двоичном и двоично-десятичном формате.

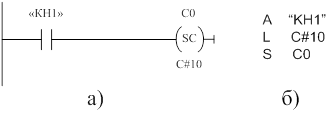

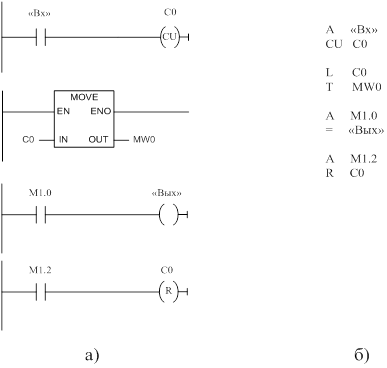

Установка счетчика производится через аккумулятор процессора АК1, в который до выполнения команды установки заносится число в счетном формате. Пример начальной установки счетчика на языках LAD и STL показан на рис.32.

Рис.32. Пример использования команды первоначальной установки счетчика на языках: а) LAD и б) STL

Установка счетчика производится по переднему фронту RLO, который в примере на рис.32 реализовывается нажатием на кнопку КН1.

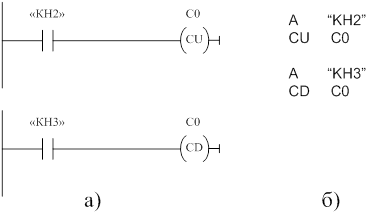

Прямой и обратный счет реализовывается командами: CU – увеличение счетчика на 1 (Counter Up) и CD – уменьшение счетчика на 1 (Counter Down). Пример схемы реализации команд на языках LAD и STL приведен на рис.33.

Рис.33. Реализация команд прямого и обратного счета на языках LAD и STL

Команда сброса обнуляет содержимое счетчика. Пример выполнения команды сброса на языках LAD и STL приведен на рис.34.

Рис.34. Реализация команды сброса счетчика на языках LAD и STL

Хотя счетчик представляет собой слово в системной памяти (16 бит) для него можно выполнить логическую операцию – опрос (чтение) состояния счетчика, т.е. например, на языке LAD состояние счетчика можно представить в виде нормально замкнутого контакта реле. Контакт считается замкнутым, если состояние слова счетчика отличается от нуля. Контакт размыкается, если счетчик обнуляется в результате обратного счета или сброса.

Значение слова можно счетчика можно загрузить в аккумулятор командой L (Load). В этом случае значение счетчика будет автоматически преобразовано из двоично-десятичного формата представления в двоичное и загружено в аккумулятор. Для сохранения двоично-десятичного формата представления счетного значения при загрузке служит команда загрузки LC (Load Counter).

Например, если счетчик содержит счетное значение равное 10, то команда L C0 загрузит аккумулятор двоичным значением АК1=00001010, а команда LС C0 загрузит АК1=00010000.

После загрузки слова счетчика в аккумулятор и последующей выгрузки аккумулятора в слово памяти (например, в маркерное слово) над битами слова счетчика могут быть проведены логические или арифметические операции. Это позволяет использовать счетчики не только в вычислительных операциях по подсчету событий, но и позволяет создавать схемы шагового или циклического управления оборудованием. Учитывая особенности работы счетчиков, могут быть реализованы самые разнообразные алгоритмы циклического управления.

Например, рассмотрим поведение счетчика при инкрементировании значения от 0 до 7. Слово счетчика при получении команды увеличения (CU) счетного значения будет последовательно принимать следующие значения:

0: 00000000

1: 00000001

2: 00000010

3: 00000011

4: 00000100

5: 00000101

6: 00000110

7: 00000111

Работая с каждым битом слова и применяя к ним логические операции можно получить практически любую циклическую последовательность. Так используя нулевой бит счетчика можно реализовать делитель на 2, используя первый бит – делитель на 4 и т.д.

Также можно реализовать циклический сброс счетчика при возникновении заданной комбинации бит слова. На рис.35 представлена программа реализации многотактного автомата - делителя на два.

Рис.35. Пример реализации делителя на два на счетчике: а) на языке LAD; б) на языке STL

Так как количество тактов в течении которого происходит полный цикл составляет 4, то в приведенном примере осуществляется сброс счетчика при достижении значения счета равного четырем (или при установке бита 2). Также можно использовать несколько счетчиков, которые производят счет разных последовательных событий и логически комбинируя их биты реализовывать более сложные циклические последовательности.

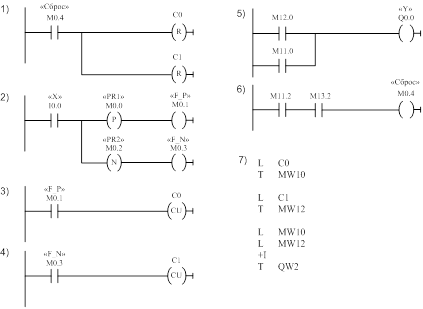

19. Задание на лабораторную работу

Реализовать многотактную схему из задания лабораторной работы №3 используя счетчики. Номер такта вывести на цифровой индикатор пульта (слово выходной таблицы образа процесса QW2). В качестве примера на рис. 36 приведено выполнение работы для реализации многотактной схемы лабораторной работы №5 (см. рис. 24).

Рис.36. Пример реализации многотактной схемы

20. Содержание отчета

Отчет должен содержать:

1. Основные операции работы со счетчиками

2. Выполнение лабораторной работы по заданиям рис.10 и 11 с описанием действий, выполняемых каждым блоком.

3. Вариант исполнения задания с описанием каждого действия по каждой команде.

Лабораторная работа №8

Изучение таймерных команд

Цель работы: изучить возможности языка STEP 7 по формированию временных интервалов с использованием таймеров, временные диаграммы работы различных типов таймеров, реализацию генераторов заданных последовательностей.

1. Общие сведения о командах работы с таймерами

Таймеры позволяют программно реализовать заданную выдержку времени от момента возникновения события запуска таймера. В зависимости от требуемого поведения таймера на событие запуска используются следующие типы таймеров:

1. Импульсный таймер (Pulse timer);

2. Расширенный импульсный таймер (Extended pulse timer);

3. Таймер задержки включения (On-delay timer);

4. Таймер задержки включения с запоминанием (Retentive on-delay timer);

5. Таймер задержки выключения (Off-delay timer).

Таймера располагаются в системной памяти CPU в области Timer (T). Таймер занимает ячейку памяти размером 16 бит (таймерное слово) в которой хранится длительность работы таймера.

Длительность работы таймера представляет собой интервал времени в течение которого таймер ведет отсчет времени («таймер работает»).

Структурно значение длительности работы состоит из двух значений: количества временных интервалов и временной базы (или длительности одного интервала). Таким образом, длительность работы таймера определяется как:

длительность:=число временных интервалов*временная база

На рис.37 приведена структура таймерного слова и указаны возможные варианты временной базы.

Значения длительности заносится в таймерное слово через аккумулятор процессора командой запуска таймера. Занесение значения времени в аккумулятор процессор должно быть произведено командой загрузки аккумулятора. Допускается использование двух вариантов занесения значения длительности: 1) с помощью шестнадцатиричной константы с соблюдением структуры таймерного слова; 2) с использованием специального формата для определения временных интервалов.

Рис.37. Структура таймерного слова

В первом варианте можно определить временную базу и число временных интервалов самостоятельно, во втором варианте расчет временной базы и числа временных интервалов происходит автоматически из значения заданного в единицах времени (часах, минутах, секундах, миллисекундах).

Например, для задания длительности времени в одну секунду возможно занесение в таймерное слово константы в следующих вариантах:

2001h: один отсчет, временная база 1 секунда;

1001h: 10 отсчетов, временная база 100 миллисекунд;

0100h: 100 отсчетов, временная база 10 миллисекунд;

S5T#1s: одна секунда.

Для более точного отсчета времени предпочтительнее использовать как можно меньшее значение базы времени. При автоматическом определении таймерного слова временная база выбирается исходя из наименьшего возможного значения. Так, например, в приведенном выше примере два последних значения таймерного слова будут идентичны.

Общий диапазон отсчета времени таймером составляет от 10 ms до 9990 s (2 часа 46 минут 30 секунд).

В зависимости от требуемого поведения таймера используются следующие команды запуска: (SP) - импульсный таймер; (SE) - расширенный импульсный таймер; (SD) - таймер задержки включения; (SS) - таймер задержки включения с запоминанием; (SF) - таймер задержки выключения.

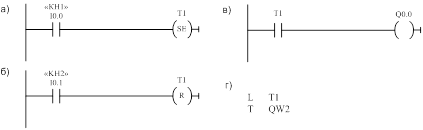

Запуск таймера по командам SP, SE, SD, SS осуществляется по переднему фронту RLO перед командой. Например, на рис.38,а показан пример запуска таймера командой SE при нажатии на кнопку КН1. Запуск таймера остальными командами производится аналогично.

Для установки таймерного слова в ноль используется команда сброса (Reset) применительно к катушке таймера. Сброс для всех таймеров производится по переднему фронту RLO перед командой сброса. Пример команды сброса приведен на рис.38.б.

Также как и счетчик, таймер можно опросить логической командой. Результат опроса зависит от примененной для этого таймера команды запуска. На рис. 38, в приведен пример опроса состояния таймера с выводом значения в выходной бит образа.

Рис.38. Команды управления и чтения состояния таймера

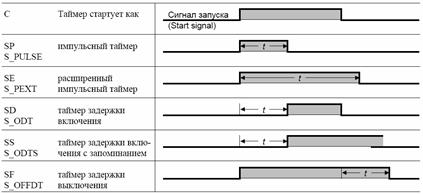

На рис.39 приведены временные диаграммы опроса таймера запущенного различными командами запуска. Также на этом же рисунке показано время работы таймера (время отсчета).

Прочитать значение текущего значения таймерного слова можно командой L (Load) загрузив его значение в аккумулятор и передать в маркерное слово (на рис.38, г передача осуществляется в слово выходной таблицы образа процесса).

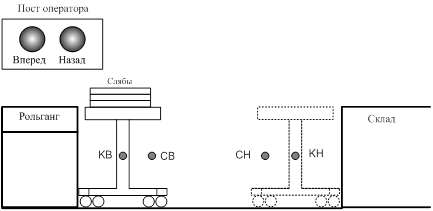

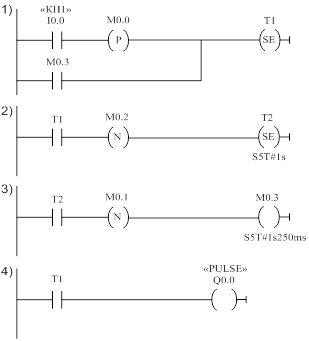

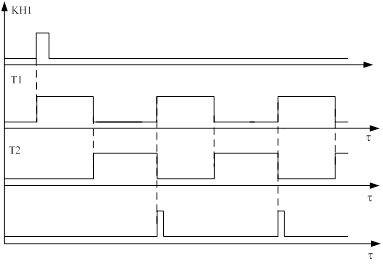

Кроме выполнения с помощью таймеров различного рода отсчетов времени и реализацию задержек таймера также часто используются для генерации различных циклических последовательностей во времени. Например, на рис.40,а приведен пример реализации генератора импульсов с использованием двух таймеров с задаваемым временем импульса и паузы (с задаваемой скважностью). На рис.41 приведена временная диаграмма его работы.

Рис.39. Временные диаграммы работы таймера запущенного различными командами запуска

Рис.40. Пример генератора с задаваемым временем импульса и паузы

Рис.41. Временная диаграмма работы генератора импульсов с регулируемым временем импульса и паузы

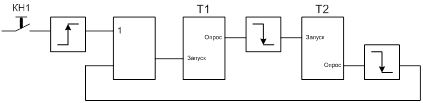

Кнопка КН1 предназначена для первоначального запуска схемы, и по переднему фронту её нажатия запускается таймер Т1. После отработки таймера Т1 по заднему фронту запускается таймер Т2. После отработки таймера Т2 формируется маркер заднего фронта М0.3 , который снова запускает таймер Т1 по параллельной цепочке. Выход генератора выводится в бит образа процесса Q0.0 обозначенного символическим именем «PULSE»

Для более наглядного представления схем взаимодействия групп таймеров и понимание их работы эти схемы удобно изображать в блочном виде, где таймер представляется элементом, имеющим вход запуска и выход, опрашиваемый логической командой. Промежуточные элементы представляются в виде стандартных блоков с обозначением по выполняемым ими действиям. Элементы, которые напрямую не участвуют в осуществлении работы таймеров на таких схемах, как правило, не показывают, и их оставляют «как есть».

Так как такие схемы обычно представляют собой замкнутые контура, то после разработки схемы взаимодействия нескольких таймеров производится их преобразование в схему на языке LAD или STL. Преобразование производится последовательно по циклу, начиная с любой удобной точки контура.

На рис.42 приведена блочная схема последовательного запуска двух таймеров для реализации генератора приведенного на рис.40.

Рис.42. Блочная схема представления работы таймеров генератора

Более сложные циклические последовательности реализовываются с использованием бóльшего количества таймеров и выполнением логических операций над результатами их опроса.

21. Задание на лабораторную работу

1. Разработать и реализовать схемы управления всеми видами таймеров (по аналогии для схемы управления SE рис.38 для таймеров SP, SS, SF, SD) и провести исследование их работы на различные комбинации команд запуска и сброса. По результатам исследований составить подробные временные диаграммы их работы.

2. Реализовать схему генератора импульсов и провести исследования его работы. Дополнить диаграмму его работы (см. рис. 41) другими его возможными состояниями, выявленными в результате исследования.

3. Реализовать циклическую схему управления для реализации временных последовательностей заданных диаграммой по вариантам.

22. Порядок выполнения работы

1. Каждую разработанную в соответствии с первым пунктом заданием схему реализовать в отдельном блоке.

2. Для отладки и исследования работы каждой схемы использовать программу эмуляции PLCSIM и пульт-имитатор.

3. Реализовать схему варианта: составить структурную схему запуска таймеров) и по ней составить программу на языке LAD или STL. После реализации и отладки задания варианта загрузить проект в контроллер и проверить его работу на пульте, подключенном к контроллеру.

23. Оформление отчета

Отчет должен содержать:

1. Все разработанные схемы в соответствии с заданием.

2. Временные диаграммы работы каждого типа таймера полученные при исследовании их работы.

3. Временную диаграмму генератора импульсов и выводы о полученных результатах его исследования.

4. Блочную схему циклической работы таймеров в соответствии с вариантам задания.

5. Релизацию варианта задания на языке LAD или STL.

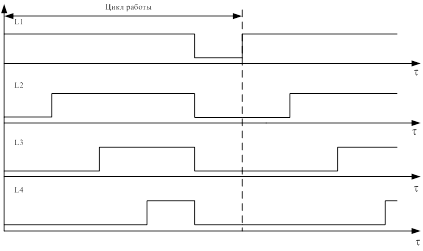

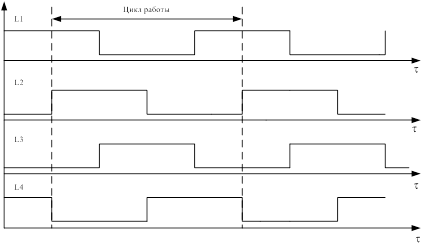

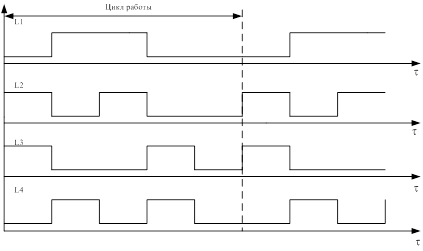

24. Задание по вариантам

Для всех вариантов задана временная диаграмма формирования выходных сигналов. Работа схемы должна быть осуществлена как в прямом времени формирования сигналов (по диаграмме слева на право), так и в обратом (по диаграмме справа налево). Направление работы схемы должно выбираться переключателем. Этим же переключателем должен осуществляться первоначальный запуск схемы.

Вариант 1.

Вариант 2.

Вариант 3.

Самостоятельная работа

Разработка релейных систем управления

Дата добавления: 2021-03-18; просмотров: 271; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!