О токоограничивающих резисторах в импульсных схемах

В схемах генераторов на рис. 16.2, формирователей на рис. 16.6 и одновибраторов на рис. 16.7 показан пунктиром дополнительный резистор, ограничивающий ток через защитные диоды микросхемы. С функциональной точки зрения он не требуется, но дело в том, что дифференцирующая RC‑цепочка, которая составляет основу этих схем, вырабатывает импульсы не только по нужному переключению сигнала, но и по противоположному, и при этом импульсы выходят за пределы питания, в чем вы можете убедиться, если взглянете на рис. 5.9.

Посмотрим, когда в этих схемах можно обойтись без токоограничивающих резисторов. Типовой допустимый постоянный ток через защитные диоды составляет порядка 10 мА для «классической» КМОП (20–30 мА для быстродействующих серий). Мы знаем, что в режиме короткого замыкания элемент «классической» КМОП выдает примерно 5 мА при 5 В питания, т. е. для серии 561 при низких напряжениях питания ограничительных резисторов не требует. Но та же серия при напряжениях питания 9 В и выше, и тем более серии быстродействующей КМОП, которые гораздо мощнее по выходу, могут перегружать защитные диоды. Тем не менее, как мы знаем, у диодов достаточно высокая перегрузочная способность, если только они не перегреваются, поэтому короткие импульсы им все равно не страшны. Так что при больших выдержках времени или при низких частотах при большом напряжении питания такой резистор лучше поставить, а в остальных случаях можно без него обойтись.

|

|

|

Триггеры, регистры и счетчики

Триггеры и построенные на их основе счетчики и регистры играют огромную роль в электронике. В состав любого процессора, кроме собственно АЛУ на основе комбинационной логики (рассмотренных в главе 15 сумматоров), входят регистры и память, которые являются прямыми родственниками счетчиков, – потому что для построения и тех и других используются триггеры. Вот со знакомства с классическими типами триггеров мы и начнем.

Между прочим, одно из главных «неэлектронных» значений слова «trigger » – спусковой крючок у огнестрельного оружия. В электронике триггер – это устройство для записи и хранения информации в количестве одного бита. Существуют и многостабильные триггеры, которые могут хранить более одного бита, но на практике они почти не используются. Любая элементарная ячейка памяти, будь то магнитный домен на пластинах жесткого диска, отражающая область на поверхности CD‑ROM, или конденсаторная ячейка электронного ОЗУ, обязательно обладает триггерными свойствами, т. е. может хранить информацию спустя еще долгое время после того, как она была в нее введена.

Самый простой триггер

|

|

|

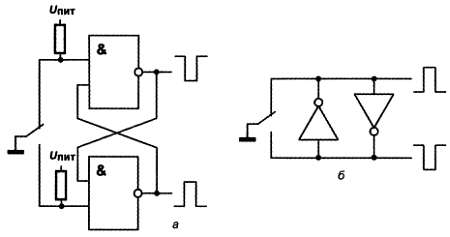

Самый простой триггер можно получить, если в схемах одновибраторов на рис. 16.7 удалить RC‑цепочку и соединить напрямую выход первого элемента со входом второго. Если схема находится в состоянии, при котором на выходе уровень логической единицы, то кратковременная подача отрицательного уровня на вход, как и в случае одновибратора, перебросит выход в состояние логического нуля. Но теперь уже нет конденсатора, который осуществляет отрицательную обратную связь и в конце концов возвращает схему в исходное состояние, потому в таком состоянии схема останется навечно, если мы что‑то не предпримем. Чтобы вернуть ее в исходное состояние, надо подать точно такой же сигнал, но на вход второго элемента, который (вход) в схеме одновибратора у нас отсутствует. Если мы его введем, то получим симметричную схему с двумя входами, которые обозначаются буквами R и S (от слов Reset и Set , т. е. «сброс» и «установка»). Само же устройство носит название RS‑триггера. Оба варианта такой схемы на элементах «И‑НЕ» и «ИЛИ‑НЕ» показаны на рис. 16.8.

Рис. 16.8. Схемы триггеров на элементах «И‑НЕ» (а ) и «ИЛИ‑НЕ» (б )

Нет нужды перебирать все состояния этих схем и приводить соответствующие таблицы истинности, нужно только твердо запомнить, что подача импульса на вход R всегда устанавливает на прямом выходе Q состояние логического нуля. (Легко сообразить, что если поменять все обозначения местами: R на S , а прямой выход Q на инверсный Q¯ , то в схеме ничего не изменится.)

|

|

|

Вход S , естественно, здесь означает ровно противоположное – установку выхода Q в состояние логической единицы, но, в отличие от входа R , который всегда означает обнуление, вход S в различных устройствах может использоваться и в несколько иных целях, а чаще вообще отсутствует. Входы R и S могут управляться различными полярностями сигнала в зависимости от построения триггера: для схемы на элементах «И‑НЕ» по рис. 16.8, а – это низкий уровень, поэтому входы R и S обозначены с инверсией. Уровни, которые меняют состояние триггера, называются активными , – так, для схемы по рис. 16.8, а активным является низкий уровень. «Более правильная» схема в этом смысле – на элементах «ИЛИ‑НЕ» по рис. 16.8, б , в ней активный уровень соответствует положительной логике, т. е. он высокий. Обратите внимание, что установка дополнительных инверторов по входу, казалось бы, превращает схему по рис. 16.8, а в схему по рис. 16.8, б , но только в смысле полярности активных уровней, прямой и инверсный выходы при этом останутся на своих местах.

|

|

|

В схемах RS‑триггеров подача активного уровня на R ‑вход ничего не меняет, если выход Q уже был в состоянии логического нуля, то же самое справедливо для S ‑входа при выходе в состоянии логической единицы. Однако, пока на соответствующем входе действует напряжение активного уровня, подача активного уровня на второй вход запрещена. Это не означает, что триггер при этом сгорит, просто он потеряет свои триггерные свойства – на обоих выходах установится один и тот же уровень, а после одновременного снятия активного уровня со входов состояние будет неопределенным (точнее, будет определяться тем элементом, который переключится чуть позже другого). Неопределенное состояние будет и после подачи питания, поэтому нужно принимать специальные меры для установки схемы в нужное состояние после включения. Наиболее распространенной такой мерой является подача определенного уровня в начальный момент времени на один из нужных входов с помощью RC‑цепочки.

Ввиду практической важности этого способа я приведу варианты соответствующей схемы, несмотря на ее очевидность (рис. 16.9). В них конденсатор в первый момент времени после подачи питания разряжен, и на входе логического элемента оказывается положительный уровень, который устанавливает триггер в состояние логического нуля на выходе Q . Затем конденсатор заряжается, и в дальнейшем RC‑цепочка больше не оказывает влияния на работу схемы. Постоянную времени RC лучше выбирать побольше, чтобы к моменту зарядки конденсатора успели пройти все переходные процессы, – на схемах по рис. 16.9 она равна примерно 0,5 мс. Естественно, при этом следует позаботиться, чтобы на «настоящих» RS‑входах к моменту окончания заряда конденсатора был неактивный уровень, иначе все пой дет насмарку.

Рис. 16.9. Схемы триггеров с предустановкой при включении питания: на двухвходовых элементах (а ) и на трехвходовых элементах (б )

Чтобы избежать нагромождения инверторов, можно в этой схеме использовать трехвходовые элементы (561ЛЕ10), как показано на рис. 16.9, б .

Естественно, RS‑триггеры выпускают и в интегральном исполнении (561ТР2 содержит четыре простых RS‑триггера). Все более сложные триггеры, а также счетчики в интегральном исполнении, обязательно имеют отдельные асинхронные RS ‑ или хотя бы только R ‑входы. Причем соответствующий вход у любого устройства, его имеющего – от микропроцессоров до счетчиков – является асинхронным, т. е. вся система обнуляется в момент подачи импульса по входу R , независимо от того, что в этот момент она делает. Говорят еще, что вход Reset – вход обнуления – имеет наивысший приоритет . Именно это происходит, скажем, когда вы нажимаете кнопку Reset на системном блоке вашего компьютера.

Использование RS‑триггера является самым кардинальным способом решения проблемы дребезга контактов. Стандартная схема показана на рис. 16.10, а , однако нет никакой нужды городить такую схему с резисторами, относительно которых еще нужно соображать, к чему их подключать (для варианта с «ИЛИ‑НЕ» их пришлось бы присоединять к «земле», а не к питанию). На рис. 16.10, б показана упрощенная схема, которая работает точно так же, и при этом в ней можно использовать любые инверторы, в том числе и одновходовые. Общим недостатком схем «антидребезга» как с RS‑триггерами, так и с использованием элемента «Исключающее ИЛИ» (см. рис. 15.8, б ) является необходимость применения переключающей кнопки с тремя выводами, которых в продаже предлагается гораздо меньше, чем обычных замыкающих и размыкающих с двумя контактами. Попробуйте приспособить двухвыводную кнопку к любой из указанных схем, и вы сами придете к выводу, что это невозможно. Поэтому на практике часто приходится использовать схему «антидребезга» с использованием одновибратора (в том числе реализованного программными способами в микроконтроллерах) – при всех ее недостатках.

Рис. 16.10. Схемы «антидребезга» на RS ‑триггерах

D‑триггеры

D‑триггеры получили свое название от слова «delay », что означает «задержка». На самом деле существуют две их разновидности, формально различающиеся только тем, что первая из них управляется уровнем сигнала (статический D‑триггер или триггер‑защелка), а вторая – фронтом импульса (динамический D‑триггер). Фактически же это разные по устройству и области использования схемы.

Для того чтобы отличить статический D‑триггер от динамического, мы в обозначении на схеме для первого поставим букву L (от слова «level » – уровень), а для второго – букву «Е » (от слова «edge » – фронт). Эти обозначения не являются общепринятыми, и в дальнейшем мы их использовать не будем, только здесь – для наглядности. Микросхема 561ТМЗ содержит четыре статических триггера‑защелки с общим входом синхронизации, а 561ТМ2 – два динамических D‑триггера с раздельными дополнительными входами R и S (мы с ней уже знакомы – см. рис. 16.5). Если тип вообще не указывается, то обычно по умолчанию предполагается, что речь идет о динамических D‑триггерах.

Статический D‑триггер легко получить из RS‑триггера путем небольшой модификации его схемы. Если из схемы на рис. 16.11, а исключить вход С (например, объединив входы каждого элемента и превратив их тем самым в простые инверторы), то получится довольно бесполезное устройство, которое на выходе Q будет просто повторять входные сигналы, а на втором выходе, соответственно – выдавать их инверсии. Наличие тактового входа С (от слова «clock », которое в цифровой электронике значит «тактовый импульс») все меняет.

Рис. 16.11. D‑триггеры :

а – схема статического D‑триггера;

б – схема динамического D‑триггера на основе двух статических,

в – счетный триггер на основе динамического D‑триггера

Если мы обратимся к диаграммам на рис. 15.8, а , то увидим, что при наличии на этом входе уровня логической единицы входные сигналы будут пропускаться на вход RS‑триггера, и схема станет повторять на выходе Q уровни на входе D . Если же мы установим на входе С уровень нуля, то схема немедленно «зависнет» в состоянии выхода, соответствующем входному уровню непосредственно перед приходом отрицательного фронта на вход С , – т. е. запомнит его! Поэтому такой триггер и называют защелкой – при подаче на вход С короткого положительного тактового импульса он как бы «защелкивает» состояние входа. Статический D‑триггер можно использовать в качестве буферного регистра для хранения данных – например, результатов счета импульсов на то время, пока идет сам процесс счета. Статическая энергозависимая память (SRAM) также, как правило, использует такие триггеры в качестве элементарных ячеек.

Динамические D‑триггеры более универсальны, и область применения у них куда шире, чем у статических. Динамический триггер устроен более сложно. Один из способов построения динамического D‑триггера из двух статических показан на рис. 16.11, б . Эта схема работает следующим образом: когда на общем входе С наличествует отрицательный уровень, состояние входа D переписывается на выход первого (слева) триггера, при этом второй триггер заперт. Сразу после положительного фронта на входе С это состояние переписывается во второй триггер и появляется на выходе Q , а первый триггер запирается. Таким образом, запоминание состояния общего D‑входа происходит в точности в момент положительного перепада уровней и никогда больше. Если изменить местоположение инвертора и присоединить его ко входу второго триггера, а на первый триггер подавать тактовые импульсы напрямую, то срабатывание станет происходить по отрицательному фронту, и такой тактовый вход будет считаться инверсным. Для того чтобы получить дополнительные входы асинхронной принудительной установки триггера в нулевое и единичное состояние (R ‑ и S ‑входы), нужно для обоих статических триггеров выходные (правые по схеме рис. 16.11, а ) элементы сделать трехвходовыми и объединить соответствующие входы у обоих триггеров. Устанавливать по входам R и S только выходной триггер недостаточно (подумайте почему?).

А на рис. 16.11, в показана самая простая схема счетного триггера на основе динамического D‑триггера, уже знакомая нам по рис. 16.5. Из описанного ясно, как она работает, – при каждом положительном перепаде на выход Q будет переписываться состояние противоположного выхода Q¯ , т. е. система станет с приходом каждого тактового импульса менять свое состояние на противоположное, в результате чего на выходе мы получим симметричный (независимо от скважности входных импульсов) меандр с частотой, вдвое меньшей, чем входная. Такой триггер можно считать делителем частоты на два или одноразрядным двоичным счетчиком – в зависимости от того, для чего он используется. В отличие от всех остальных типов триггеров (а кроме описанных, распространены еще, например, и так называемые JK‑триггеры , но мы их рассматривать не будем), счетные триггеры в интегральном исполнении отдельно не выпускаются (при случае их легко, как вы видели, соорудить, например, из D‑триггеров), а выпускаются только готовые многоразрядные двоичные счетчики, из таких триггеров составленные. К рассмотрению счетчиков мы перейдем чуть позднее, а пока кратко остановимся на регистрах.

Регистры

Регистрами называют устройства для хранения одного двоичного числа. Количество разрядов в регистрах, выпускаемых отдельно, обычно не превышает восьми, но в составе других микросхем могут быть и регистры с большей разрядностью – вплоть до 128 или 256 битов в «продвинутых» микропроцессорах. Большинство типов электронных запоминающих устройств, вообще говоря, можно рассматривать как совокупность регистров. Но собственно регистры, как входящие в состав процессоров, так и выпускаемые отдельно, отличаются тем, что позволяют не только записывать и считывать информацию, но и производить некоторые простейшие операции, – например, сдвиг разрядов.

Простейший регистр – это упомянутый ранее статический D‑триггер. Четыре таких триггера, входящих в микросхему 561ТМЗ, образуют четырехразрядный регистр с параллельной записью и считыванием, причем тактовый вход в этой микросхеме у всех четырех разрядов общий. Как и сам триггер, такой регистр называют «защелкой».

Если регистр‑защелка позволяет осуществлять только параллельную запись, то последовательный регистр (пример – 561ИР2), наоборот, имеет возможность записи только через один вход, который является D‑входом самого младшего разряда. Последовательный регистр является неким обобщением конструкции D‑триггера. Работу динамического D‑триггера можно рассматривать, как процесс сдвига информации от входа через первый триггер ко второму при поступлении соответствующих перепадов на тактовом входе. В последовательном регистре, который в простейшем случае представляет собой просто последовательное соединение таких триггеров, происходит нечто подобное – с каждым фронтом тактового импульса информация сдвигается от младшего разряда к старшему, при этом в младший разряд записывается состояние входа. Считывать информацию при этом можно из каждого разряда в отдельности, как и в случае регистра‑защелки. Такие регистры получили еще название сдвиговых. Они широко используются для последовательного ввода и вывода информации – скажем, для вывода восьми битов через последовательный порт RS‑232 достаточно записать их в такой регистр, а потом подать на него восемь тактовых импульсов с нужной частотой.

Сдвиговый регистр можно закольцевать – соединить выход старшего разряда со входом младшего и получить нечто подобное слону из анекдота, который засунул хобот себе в известное место. Однако в случае одного сдвигового регистра такое соединение приведет к тому же результату, что и для слона, т. е. оно довольно бесполезно практически, ибо мы без дополнительных ухищрений запись информации производить уже не сможем. Поэтому используют объединение параллельной и последовательной записи/считывания в одном устройстве (пример – четырехразрядный регистр 561ИР9 или восьмиразрядный 561ИР6).

* * *

Заметки на полях

Такие сдвиговые регистры с параллельной записью и последовательным считыванием информации – неотъемлемая часть устройств памяти большой емкости, без них чтение и запись в большие массивы запоминающих ячеек были бы невозможны. Имеются они, например, в матрицах цифровых камер. Интересное применение таких регистров – организация последовательного интерфейса SPI, широко используемого для скоростного обмена информацией между различными микросхемами (например, между энергонезависимой памятью вроде флэш‑карточек и микроконтроллером).

В SPI наличествуют два восьмибитовых регистра, соединенных в кольцо входами/выходами, но они разделены пространственно: один регистр находится в одном устройстве, другой – в другом. Если подавать тактовые импульсы на оба регистра одновременно (это осуществляет одно из устройств – ведущее), то после подачи ровно 8 импульсов устройства обменяются содержимым своих регистров.

* * *

Счетчики

Самый простой счетчик можно получить, если соединить последовательно ряд счетных триггеров, как показано на рис. 16.12, а . У этой схемы есть две особенности. В первой из них легко разобраться, если построить диаграмму работы такого счетчика, начиная с состояния, в котором все триггеры находятся в состоянии низкого уровня на выходе («0000»). В самом деле, при подаче первого же импульса триггеры перейдут в состояние со всеми единицами («1111»)! Если строить диаграмму дальше, то Мы увидим, что последовательные состояния будут такими: «1110», «1101» и т. д. В этом легко узнать последовательный ряд чисел 15, 14, 13 – т. е. счетчик получился вычитающим, а не суммирующим.

А как можно получить суммирующий счетчик? Очень просто – надо ко входу каждого следующего триггера подсоединить не прямой выход предыдущего, а инверсный. Порядка ради можно тактовые импульсы подавать также через инвертор (рис. 16.12, б ), тогда все разряды счетчика, включая самый младший, будут срабатывать по заднему (отрицательному) фронту входного импульса, а не по переднему (у «настоящих» счетчиков тактовый вход и делается инверсным). В этом случае будет все в порядке – входные импульсы будут суммироваться (см. диаграмму) и мы получим ряд последовательных состояний: «0000», «0001», «00010», «0011» и т. д.

* * *

Заметки на полях

Удивительная все же штука – электроника! Сначала мы получили полную аналогию между абстрактной математической теорией и состояниями переключателей на реле, теперь вот – между не менее абстрактным арифметическим счетом и последовательными состояниями счетчика на триггерах. Чем этот счетчик отличается от дикаря, раскладывающего на земле палочки? Ничем, кроме того, что он раскладывает не палочки, а уровни напряжений, причем выгодно отличается от первобытного сознания тем, что еще и «владеет» позиционной системой счисления. Начинаешь понимать, почему ученые середины прошлого века были так обольщены возможностями электронных схем, что даже заговорили о «машинном разуме». Но это уже другая тема…

* * *

Однако у счетчиков, построенных по такой простейшей схеме, есть один крупный недостаток, которого мы отчасти касались в этой главе. А именно – переключение триггеров происходит асинхронно, сигнал от входа должен пройти всю цепочку, пока на выходе также изменится уровень. Эти, казалось бы, незначительные задержки могут, однако, привести к существенным неприятностям вроде возникновения лишних «иголок» при дешифрировании состояний выхода. А при больших частотах входных импульсов, на пределе возможностей логических элементов, фронты сигналов на выходах могут приобрести совершенно хаотическое расположение относительно входного сигнала, так что дешифрировать состояние счетчика будет невозможно. Поэтому большинство счетчиков в интегральном исполнении делают по иным, синхронным, схемам, когда входной тактовый сигнал подается одновременно на все разряды, и фронты выстраиваются строго «по линеечке», независимо от задержек в том или ином триггере. Подробно изучать синхронные схемы мы не будем, т. к. самим нам их строить не придется, а здесь рассмотрим пару конкретных типов серийно выпускаемых счетчиков.

Рис. 16.12. Схемы асинхронных счетчиков на D ‑триггерах:

а – вычитающего; б – суммирующего

Первый из счетчиков, который мы рассмотрим подробно, – 561ИЕ10. Микросхема содержит два одинаковых четырехразрядных синхронных счетчика в одном корпусе. Разводка выводов ее показана на рис. 16.13, а , где вроде бы все понятно, кроме назначения вывода Е . Каждый четырехразрядный счетчик, входящий в состав этой микросхемы, работает так: если на выводе Е присутствует напряжение высокого уровня, то счетчик будет переключаться по положительному фронту на входе С .

Однако это касается только первого триггера, все остальные станут работать в соответствии с диаграммой по рис. 16.12, б , т. е. счетчик будет суммировать импульсы. Вывод Е тут является разрешающим («enable ») для тактового входа С .

Однако если оставить на входе С напряжение логического нуля, а тактовые импульсы подавать на вход Е , то счетчик будет срабатывать от отрицательного перепада напряжений на этом входе, т. е. диаграмма его окажется в полном соответствии с диаграммой на рис. 16.12, б . В этом варианте вход С будет разрешающим для входа Е . Как видите, можно было бы поменять обозначения Е и С местами, однако в этом случае их следует дополнить знаком инверсии. Поэтому если вы хотите каскадировать два счетчика из этой микросхемы, получив в результате один восьмиразрядный счетчик, то выход Q3 первого счетчика нужно присоединить именно ко входу Е второго, подав на вход С потенциал логического нуля. Учтите, однако, что при этом обе половинки результирующей конструкции (старшая и младшая тетрады) станут работать асинхронно относительно друг друга, и срабатывание четырех старших разрядов будет происходить позднее, чем срабатывание младших.

Рис. 16.13. Разводка выводов счетчиков 561ИЕ10 (а ) и 561ИЕ11 (б ); организация автоматической предустановки счетчиков типа ИЕ11 (в )

Вывод обнуления R обозначен без инверсии, что означает установку всех разрядов в состояние 0 при подаче высокого уровня на этот вход. Пока этот уровень присутствует, счетчик будет игнорировать любые изменения на тактовых входах. Максимальная рабочая частота микросхемы ИЕ10 при напряжении питания 5 В – 1,5 МГц, минимальная длительность импульса сброса – 250 нс. Кстати, при составлении таблицы в приложении 4 я с некоторым трудом разыскал для нее быстродействующий аналог, и соответствие счетчика 74хх393 (ИЕ19) микросхеме 561ИЕ10 неполное: хотя у них даже совпадают основные выводы корпуса, но ИЕ10 выпускается в корпусе с 16‑ю выводами, а 74хх393 – с 14‑ю. Отсутствующие в аналоге два вывода у ИЕ10 выполняют как раз функцию разрешения счета Е для двух половинок микросхемы, т. е. в аналоге он отсутствует, а входы тактовых импульсов С – инверсные.

Счетчик 561ИЕ11 более универсален, и управляющих выводов у него значительно больше, поэтому в 16‑выводном корпусе умещается только один четырехразрядный счетчик. Разводка и обозначение выводов для него показаны на рис. 16.13, б . Не правда ли, можно запутаться? Однако на самом деле все гораздо проще, чем выглядит.

Если на выводах R, SE, Р¯вх присутствуют низкие уровни напряжения, а на входе U /D¯ – высокий, то счетчик считает по положительному фронту на входе С , в точности так же, как это делает половинка ИЕ10 при высоком уровне на входе Е . Разберемся с действием остальных входов. Со входом обнуления R все понятно – при подаче на него высокого уровня все обнуляется. Вход U /D¯ служит для реверсии (потому такой счетчик еще называется реверсивным ) – если на него подать напряжение логического нуля, то счетчик будет не суммировать, а вычитать, подобно тому, как это делает счетчик, показанный на рис. 16.12, а .

Самый интересный – вход SE («set enable » – разрешение установки). Если на него подать напряжение логической единицы, то в триггеры счетчика запишутся значения, установленные на входах S0‑S3. Возможность такой параллельной предустановки значительно расширяет возможности счетчика. А вход и выход переноса Р¯ вх и Р¯вых предназначены для каскадирования счетчиков – для получения синхронного (в отличие от ИЕ10) счетчика большей разрядности, надо входы С у всех микросхем объединить, а выход Р¯вых предыдущего счетчика соединить со входом Р¯ вх следующего. У самого первого счетчика, естественно, Р¯ вх присоединяется к «земле».

Сколько удовольствия можно получить от этой схемы! Я покажу только один из вариантов того, как ее использовать. Наличие возможности предустановки произвольного значения позволяет соорудить из этой микросхемы счетчик с любым коэффициентом деления входной частоты (в пределах емкости исходного счетчика) – если используется один корпус ИЕ11, то это значения от 1 до 16. В самом деле, если счетчик считает в стандартном режиме, то частота на выходах Qx будет равна входной, поделенной на 2, 4, 8 и 16. Принцип установки другого коэффициента проще всего показать на примере обратного (вычитающего) режима счета.

Арифметика тут простая: предположим, мы установили на входах предустановки число 3 (0011) и организовали схему так, чтобы в состоянии, когда все выходы Qi равны нулю, это число каждый раз записывалось бы в счетчик. Поскольку режим вычитающий, то при подаче тактовых импульсов на вход счетчик будет последовательно проходить состояния: предустановка (0011) – фронт тактового импульса (0010) – фронт тактового импульса (0001) – фронт тактового импульса (0000) – предустановка (0011) и т. д. То есть после каждых трех тактовых импульсов счетчик будет возвращаться в исходное состояние (если предустановки нет, то он это делает после каждых 16 импульсов).

Таким образом мы получили коэффициент деления, равный 3. Можно резюмировать: в вычитающем режиме коэффициент деления будет такой, каково число на входах предустановки. А что будет, если запустить счетчик в обычном режиме, суммирующем? Нетрудно подсчитать, что коэффициент деления при этом будет равен разности между максимально возможным коэффициентом (16) и установленным числом (3) – в данном случае 13.

Я так подробно на этом останавливаюсь, кроме всего прочего, еще и потому, что счетчики‑таймеры в микропроцессорных системах (и в составе микроконтроллеров типа AVR, и в других микроконтроллерах, и системный счетчик в IBM PC, который без изменений воспроизводится во всех системах от Intel) работают совершенно аналогично ИЕ11. И для того чтобы успешно программировать микроконтроллерные системы, необходимо очень хорошо понимать принцип их работы, – без таймеров микроконтроллеры, можно сказать, вообще не нужны. Но в микроконтроллерах все остальное за нас уже сделали, а если вернуться к обычной интегральной логике, то сразу встают два вопроса. Первый их них звучит так: а откуда, собственно, считывать эту поделенную частоту?

При использовании вычитающего режима считывать частоту придется с того выхода счетчика, который соответствует реальной разрядности делителя, – по расписанной «диаграмме» видно, что в случае коэффициента, равного 3, старшие разряды вообще не используются. Это приемлемо, если мы хотим иметь раз и навсегда установленный коэффициент, но в общем случае неудобно – если коэффициент по ходу дела меняется. Поэтому нужно либо использовать суммирующий режим, при котором старший разряд всегда задействован, и результирующая частота снимается именно с него (например, при приведенных значениях счетчик будет все время считать от 3 до 15), либо… либо есть еще одна возможность, для знакомства с которой придется ответить сначала на второй вопрос: как организовать предустановку значения счетчика каждый раз при достижении им состояния «0000»?

Схема на рис. 16.13, в демонстрирует, как можно это сделать (это не единственный вариант, но нам подойдет). Диаграмма работы схемы (справа) показана, начиная с момента, когда вот‑вот должен прийти такт, при котором счетчик установится в состояние «0000». В любом другом состоянии на входе четырехвходового элемента «ИЛИ‑НЕ» присутствует хотя бы одна единица и на выходе его, соответственно, логический ноль. Выход же элемента «И‑НЕ» пребывает по этой причине в состоянии логической единицы, а на входе SE – логический ноль, как и положено при счете.

Как только с очередным положительным тактовым перепадом счетчик установится в состояние «0000», то на выходе элемента «ИЛИ‑НЕ» появится логическая единица. Поскольку тактовый импульс пропускается через инвертор, то на нижнем по схеме входе «И‑НЕ» в этот момент логический ноль, и на выходе его по‑прежнему единица. И только после отрицательного перепада на тактовом входе С (который для остальной схемы является нерабочим) на обоих входах «И‑НЕ» установится логическая единица, на выходе – логический ноль, и на SE появится, наконец, долгожданный высокий уровень, разрешающий запись значений, установленных по входам S0‑S3. Как только запись произойдет, все немедленно отработает назад, т. к. на выходе «ИЛИ‑НЕ» высокого уровня уже не будет. Импульс на входе SE окажется очень кратковременным, но нам длиннее и не надо.

Легко сообразить, что частота положительных импульсов на выходе «ИЛИ‑НЕ» (либо коротких импульсов перезаписи на входе SE ) как раз в точности равна частному от деления входной частоты на установленный коэффициент. И ее в этом качестве использовать удобнее, чем выходы разрядов, потому что не нужно гадать, с какого разряда снимать частоту при вычитающем режиме. Если поставить многопозиционный переключатель, меняющий код на входах предустановки S0‑S3, то можно получить счетчик с изменяемым коэффициентом деления от 1 до 16.

Микросхема 561ИЕ14 полностью аналогична ИЕ11, за исключением того, что у нее есть еще вход переключения двоичного/десятичного счета B /D . Так как все выводы 16‑выводного корпуса у ИЕ11 заняты, для этого пришлось пожертвовать входом R , вместо которого имеется вывод B /D . Если на этом входе напряжение низкого уровня, счетчик ИЕ14 считает в двоично‑десятичном коде, если высокого – становится полностью аналогичным ИЕ11. Постойте, а как же его обнулять, если вход R отсутствует? Очень просто – надо подать на все входы предустановки S0‑S3 потенциал «земли», а импульс обнуления подавать на вход SE вместо R .

Дата добавления: 2019-02-12; просмотров: 272; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!