Пример проектирования полусумматора на логических элементах.

Как видно из таблицы 9.7, для реализации функции Si необходим элемент “неравнозначность” (сумматор по модулю два), а для реализации функции Pi - логическое И. Булевы выражения для Si и Pi в СДНФ имеют вид:

.(9.11)

.(9.11)

На рисунке 9.20.1 приведена схема, реализующая выражение 9.11 на элементах И, ИЛИ, НЕ.

Рисунок 9.20.1

Для получения более простой схемы одноразрядного полусумматора на логических элементах функцию Si лучше представить в СКНФ (см. таблицу 9.7)

.(9.12)

.(9.12)

Выполнив преобразование по теореме де Моргана, получим:

,(9.13)

,(9.13)

где Ai∙Bi = Pi (см. 9.11).

Выражение (9.13) реализуется схемой, показанной на рисунке 9.20, а.

Рисунок 9.20

Если сравнить эту схему со схемой, реализующей выражение (9.11), то схема на рисунке 9.20, а выглядит проще.

Условные графические обозначения полусумматора и полного одноразрядного сумматора на электрических схемах показаны на рисунке 9.20 б, в, а схема полного одноразрядного сумматора, выполненного на двух полусумматорах, показана на рисунке 9.20, г.

Для сложения n-разрядных чисел необходимо (n-1) одноразрядных полных сумматоров и один полусумматор в нулевом разряде (рисунок 9.21).

В этом сумматоре реализована последовательная передача переноса из одного разряда в другой. При большом количестве разрядов суммируемых чисел длительность суммирования в сумматорах с последовательным переносом может оказаться недопустимо большой. Бульшим быстродействием обладают сумматоры с параллельным переносом, содержащие схему ускоренного переноса [3].

|

|

|

Рисунок 9.21

9.1.2.4 Устройства контроля четности (УКЧ)

Предназначены для проверки двоичных кодовых комбинаций, поступающих на их входы, на наличие в них четного (нечетного) числа единиц. Такое КЦУ имеет n входов, равное количеству разрядов входного ДК, и один выход. На выходе формируется напряжение высокого уровня только в том случае, если число единиц во входном коде нечетное. Основу схемы контроля четности составляет сумматор по модулю два, реализующий логическую операцию

.(9.14)

.(9.14)

Для двух переменных эта операция может быть выполнена логическим элементом “ИСКЛЮЧАЮЩЕЕ ИЛИ”, который реализует логическую функцию

.(9.15)

.(9.15)

Функция F имеет значение единица только в том случае, если в наборе из двух переменных имеется одна единица, в остальных случаях значение функции равно нулю.

Ниже показаны: состав микросхемы К555ЛП5, включающей 4 двухвходовых сумматора по модулю два (рисунок 9.22, а), пример построения на основе ИМС К555ЛП5 устройства контроля четности 8-разрядного ДК (рисунок 9.22,б) и обозначение микросхемы К561СА1, являющейся устройством контроля четности 12-разрядных двоичных кодов (рисунок 9.22, в).

|

|

|

Если V = 0, то:

чет à F = 0; ü

ý F дополняет до четности.

нечет à F = 1;þ

Если V = 1, то:

чет à F = 1; ü

ý F дополняет до нечетности.

нечет à F = 0;þ

А Б

В

Рисунок 9.22

9.1.2.5 Цифровые компараторы

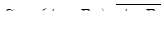

Сравнивают два числа, представленных в двоичном коде, А={an-1, an-2,..., a1, a0} и В= {вn-1, вn-2,..., в1, в0} и формируют признак результата сравнения в виде напряжения высокого уровня на одном из выходов: FA=B , FA<B , FA>B.

Рисунок 9.23

Наиболее простой является схема формирования признака равенства двух чисел (рисунок 9.23).

Такой компаратор включает логический элемент ИЛИ-НЕ, на входы которого подаются результаты поразрядного сложения по модулю два. Схема реализует логическую функцию

.(9.16)

.(9.16)

После преобразования (9.13.1) по теореме де Моргана получим:

. (9.17)

. (9.17)

Учитывая, что  =

=  – неэквивалентность (и сумма по модулю два для двух переменных), выражение (9.17) примет вид:

– неэквивалентность (и сумма по модулю два для двух переменных), выражение (9.17) примет вид:

,(9.18)

,(9.18)

что соответствует рисунку 9.23.

Если А=В, то F=1, если А ¹ В, то F=0.

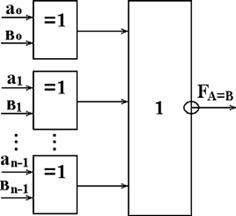

Ниже показаны: обозначение 4-входового компаратора на электрических схемах (рисунок 9.24, а) и пример его реализации на сумматоре и логических элементах И, ИЛИ-НЕ, НЕ (рисунок 9.24, б).

|

|

|

А

Б

Рисунок 9.24

9.1.3 Использование для проектирования КЦУ мультиплексоров, дешифраторов и постоянных запоминающих устройств

В связи с тем, что многие серии ИМС содержат в своем составе мультиплексоры, дешифраторы и постоянные запоминающие устройства (ПЗУ), то рассмотрим возможность реализации на их основе различных КЦУ. В ряде случаев, особенно при большом числе входных переменных и значительном количестве выходов это позволяет уменьшить общее число требуемых корпусов микросхем.

9.1.3.1 Построение КЦУ на мультиплексорах

В качестве примера рассмотрим реализацию с помощью восьмивходового мультиплексора (рисунок 9.25) мажоритарного элемента, функционирование которого описано таблицей истинности (таблица 9.8).

На адресные входы мультиплексора подаются входные логические переменные Х1, Х2, Х3, а на информационных входах D0...D7зафиксированы значения реализуемой логической функции на наборах логических переменных, номера которых совпадают с номерами информационных входов мультиплексора.

Рисунок 9.25

Таблица 9.8

| № набора | X3 | X2 | X1 | F | |

| 0 | 0 | 0 | 0 | 0 | Y0 |

| 1 | 0 | 0 | 1 | 0 | Y1 |

| 2 | 0 | 1 | 0 | 0 | Y2 |

| 3 | 0 | 1 | 1 | 1 | Y3 |

| 4 | 1 | 0 | 0 | 0 | Y4 |

| 5 | 1 | 0 | 1 | 1 | Y5 |

| 6 | 1 | 1 | 0 | 1 | Y6 |

| 7 | 1 | 1 | 1 | 1 | Y7 |

Имеется возможность вдвое сократить требуемое число информационных входов мультиплексора (а, следовательно, использовать более простую его структуру), если на эти входы подать не только фиксированные уровни логических единиц и нулей, но и значения отдельных входных переменных Х.

|

|

|

Таблица 9.9

| (A2) | (A1) | Информационные входы мультиплексора 4x1 (рисунок 9.26) | ||||

| № набора | X3 | X2 | X1 | F | D | |

| Гр.1 | 0 | 0 | 0 | 0 | 0 | D0=0 |

| 1 | 0 | 0 | 1 | 0 | ||

| Гр.2 | 2 | 0 | 1 | 0 | 0 | D1=X1 |

| 3 | 0 | 1 | 1 | 1 | ||

| Гр.3 | 4 | 1 | 0 | 0 | 0 | D2=X1 |

| 5 | 1 | 0 | 1 | 1 | ||

| Гр.4 | 6 | 1 | 1 | 0 | 1 | D3=1 |

| 7 | 1 | 1 | 1 | 1 |

Для этого еще раз изобразим таблицу истинности проектируемого мажоритарного элемента, разделив ее на четыре группы по две строки в каждой (таблица 9.9).

В пределах каждой группы возможны только четыре значения выходной булевой функции F: нулевое значение на обоих наборах – гр. 1; единичное значение на обоих наборах – гр.4: совпадение функции F с переменной Х1 (наборы 2, 3, 4, 5): противоположные значения функции F и переменной Х1 (в данном примере отсутствуют).

Следовательно, для реализации соответствующего КЦУ можно использовать четырехвходовой мультиплексор, на адресные входы которого подаются переменные Х3 и Х2, а на информационные входы D – значения в соответствии с последним столбцом таблицы 9.9 (рисунок 9.26).

Рисунок 9.26

В результате имеется возможность уменьшить аппаратные затраты используя для реализации трехвходового мажоритарного элемента лишь половину микросхемы К555КП2.

9.1.3.2 Построение КЦУ на дешифраторах

Для построения КЦУ можно использовать дешифраторы. Так как активное значение сигнала на каждом выходе дешифратора определяет одну из комбинаций входных сигналов, то, объединяя с помощью соответствующих логических элементов некоторые выходные сигналы дешифратора, можно реализовать КЦУ, заданное любой таблицей истинности, с числом наборов, не превышающим число выходов используемого дешифратора.

Рассмотрим пример реализации трехвходового мажоритарного элемента (таблица 9.8) на трехвходовом дешифраторе.

Для выходов дешифратора Yi с активными единичными значениями выходных сигналов (рисунок 9.27, а) можно записать:

;

;  ;

;

;

;  ;

;

;

;  ;

;

;

;  .

.

В таком случае в СДНФ функция мажоритарность в соответствии с таблицей 9.8 может быть представлена в виде

.(9.17)

.(9.17)

Это выражение и реализует схема на рисунке 9.27, а.

Представим ту же функцию в СКНФ и произведем некоторые преобразования по теореме де Моргана:

.

.

Проанализировав полученное выражение, а также выражения для Yi, приведенные выше, можно окончательно записать:

.(9.18)

.(9.18)

В этом случае трехвходовой мажоритарный элемент может быть реализован на трехвходовом дешифраторе с активными нулевыми значениями выходных сигналов (рисунок 9.27, б).

Рисунок 9.27

Если сравнить между собой реализации КЦУ на основе мультиплексоров и дешифраторов, то можно отметить меньшие аппаратные затраты при использовании мультиплексоров. Однако в конкретных условиях проектирования КЦУ может оказаться целесообразным применение для этих целей и дешифраторов, например, когда половина микросхемы сдвоенного дешифратора уже использована в составе проектируемого устройства, а другая половина осталась свободной и может быть применена для построения какого-либо КЦУ.

9.1.3.3 Построение КЦУ на постоянном запоминающем устройстве (ПЗУ)

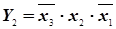

ПЗУ представляет собой большую интегральную схему (БИС), имеющую N входов и М выходов. Упрощенная структура ПЗУ при Nвх=2 и Мвых=3 приведена на рисунке 9.28, а. На входе схемы установлен дешифратор, преобразующий комбинации двухразрядного двоичного кода в четырехпозиционный унитарный (десятичный) код. При каждой комбинации входного ДК на одном из выходов дешифратора появляется логическая 1, а на остальных – нули.

Между выходами дешифратора k, l, m, n и выходными шинами ПЗУ X, Y, Z включены цепочки из двух последовательно включенных диодов VD1 и VD2. На рисунке 9.28, б в качестве примера показана связь между выходной шиной К дешифратора и выходом Х ПЗУ. В исходном состоянии цепочки, связывающие выходы дешифратора и выходы ПЗУ, ток не проводят и связи между шинами k, l, m, n и Х, Y, Z отсутствуют. При этом со всех выходов X , Y , Z снимаются логические нули.

Пользователь на специальном устройстве – программаторе – создает нужные связи между шинами, подавая пробивные напряжения между определенными точками. При этом соответствующие диоды пробиваются, например VD2 (рисунок 9.28, б), и в дальнейшем могут рассматриваться как короткозамкнутые.

На рисунке 9.28, а кружочками показаны созданные постоянные связи, реализующие таблицу истинности комбинационного устройства с тремя выходами (таблица 9.10).

Таблица 9.10

| N | B | A | X | Y | Z | |

| 0 | 0 | 0 | 1 | 0 | 1 | k |

| 1 | 0 | 1 | 0 | 1 | 0 | l |

| 2 | 1 | 0 | 1 | 1 | 1 | m |

| 3 | 1 | 1 | 1 | 0 | 0 | n |

Рисунок 9.28

Например, при комбинации входных логических переменных А=1, В=0 с выходов снимаются сигналы Х=0; Y=1; Z=0. Таким образом на ПЗУ можно реализовать нужную таблицу истинности комбинационного устройства, имеющего несколько выходов. Одна схема ПЗУ может заменить большое число логических микросхем малого и среднего уровня интеграции, поэтому ПЗУ могут эффективно использоваться для создания сложных комбинационных устройств. Кроме того, ПЗУ находят широкое применение как элементы постоянной памяти, в которые заносятся программы, управляющие работой микропроцессоров и однокристальных микроЭВМ.

9.2 Последовательностные цифровые устройства

Выше были рассмотрены комбинационные цифровые устройства, в которых имеется однозначная связь между входными и выходными сигналами, и отсутствуют элементы памяти.

В цифровой электронике существует еще одна группа устройств, содержащих элементы памяти. Поэтому их выходные сигналы в общем случае зависят не только от сигналов, приложенных к входам в данный момент времени, но и от сигналов, воздействующих на них ранее. Поскольку наличие памяти позволяет задавать последовательность выполнения определенных логических операций, то такие логические устройства называются последовательными или последовательностными [3, 11].

К ним, прежде всего, относятся триггеры, а также схемы, которые выполняются на их основе: регистры, счетчики, распределители, полупроводниковые запоминающие устройства (ЗУ) и другие.

Рассмотрим более подробно основные последовательностные цифровые устройства (ПЦУ).

9.2.1 Триггеры

Триггером называется устройство, имеющее два устойчивых состояния равновесия и способное под действием управляющих сигналов быстро (скачкообразно) переходить из одного состояния в другое. При включении напряжения питания и отсутствии внешних управляющих сигналов триггер произвольно занимает одно из двух состояний и может находиться в нем как угодно долго. Триггер является элементом памяти и способен хранить 1 бит информации.

Существует четыре разновидности схемной реализации (исполнения) триггеров:

1. На дискретных компонентах с использованием транзисторов (полупроводниковые импульсные триггеры).

2. На интегральных микросхемах операционных усилителей (триггеры Шмитта).

3. На логических элементах.

4. В виде специализированной интегральной микросхемы.

Первые две группы были рассмотрены в курсе “ЭМСТ (ч.2)”. Ниже остановимся более подробно на двух последних вариантах исполнения триггеров (на цифровых триггерах).

В зависимости от свойств, числа входов и функционального назначения цифровые триггеры можно разделить на несколько видов.

Прежде всего, следует различать нетактируемые (асинхронные) и тактируемые (синхронные) триггеры. Изменение состояния асинхронного триггера происходит сразу же после соответствующего изменения потенциалов на его управляющих входах.

В синхронном триггере переключение может произойти только в момент присутствия соответствующего сигнала на тактовом (синхро) входе.

Тактирование может осуществляться импульсом (потенциалом) или фронтом (перепадом потенциала). В первом случае, сигналы на управляющих входах оказывают влияние на состояние триггера только при разрешающем потенциале на тактовом входе. Во втором случае, воздействие управляющих сигналов проявляется в момент перехода единица-нуль или нуль-единица на синхровходе.

Существуют также универсальные триггеры, которые могут работать как в синхронном, так и в асинхронном режиме.

Основными типами триггеров в зависимости от функционального назначения являются:

- RS - триггеры;

- Т - триггеры;

- D - триггеры;

- JК - триггеры.

9.2.1.1 Триггеры на логических элементах

9.2.1.1.1 RS - триггеры

Делятся на асинхронные и синхронные.

9.2.1.1.1.1 Асинхронные RS - триггеры

Могут быть выполнены на логических элементах базисов ИЛИ-НЕ и И-НЕ.

Ниже показаны: принципиальная схема (рисунок 9.29, а), обозначение на электрических схемах (рисунок 9.29, б) и таблица истинности (таблица 9.11) асинхронного RS - триггера на логических элементах ИЛИ-НЕ.

А Б

Рисунок 9.29

В таблице 9.11 приняты следующие обозначения: R и S - сигналы на входах триггера; Qt – выходной сигнал триггера до поступления входных управляющих сигналов; Qt+1 – выходной сигнал после воздействия управляющих сигналов.

Таблица 9.11

| № | S | R | Qt+1 |

| 0 | 0 | 0 | Qt |

| 1 | 0 | 1 | 0 |

| 2 | 1 | 0 | 1 |

| 3 | 1 | 1 | Неопределенность |

Триггер называется асинхронным, т.к. он переходит в новое состояние немедленно после изменения комбинации входных сигналов. Входы S и R названы по первым буквам английских слов set – установка и reset – предустановка (сброс). Триггер устанавливается в единицу (  ) при комбинации входных сигналов S=1, R=0. Сброс в нуль (

) при комбинации входных сигналов S=1, R=0. Сброс в нуль (  ) происходит при S=0, R=1. Если S=R=0, то состояние схемы не меняется (Qt = Qt+1). Комбинация S=R=1, является запрещенной, т.к. положение триггера в этом случае не определено. В схеме выполняется условие возникновения скачков: баланс фаз (триггер содержит положительную обратную связь (ПОС)) и баланс амплитуд (суммарное усиление схемы больше суммарного затухания, вносимого пассивными элементами). Поэтому при изменении входных управляющих сигналов триггер быстро (лавинообразно) изменяет свое состояние. При включении питания и пассивном значении управляющих сигналов R=S=0 схема занимает произвольное положение (нулевое –

) происходит при S=0, R=1. Если S=R=0, то состояние схемы не меняется (Qt = Qt+1). Комбинация S=R=1, является запрещенной, т.к. положение триггера в этом случае не определено. В схеме выполняется условие возникновения скачков: баланс фаз (триггер содержит положительную обратную связь (ПОС)) и баланс амплитуд (суммарное усиление схемы больше суммарного затухания, вносимого пассивными элементами). Поэтому при изменении входных управляющих сигналов триггер быстро (лавинообразно) изменяет свое состояние. При включении питания и пассивном значении управляющих сигналов R=S=0 схема занимает произвольное положение (нулевое –  или единичное –

или единичное –  ).

).

Для проектирования RS - триггера могут быть использованы также логические элементы базиса И-НЕ.

Ниже показаны: принципиальная схема (рисунок 9.30, а), обозначение на электрических схемах (рисунок 9.30, б) и таблица истинности (таблица 9.12) асинхронного RS - триггера на логических элементах И-НЕ.

А Б

Рисунок 9.30

Таблица 9.12

| № | S | R | Qt+1 |

| 0 | 0 | 0 | Неопределенность |

| 1 | 0 | 1 | 1 |

| 2 | 1 | 0 | 0 |

| 3 | 1 | 1 | Qt |

Отличие этого триггера от предыдущего состоит в том, что активным значением управляющих сигналов является логический нуль, а пассивным – логическая единица.

9.2.1.1.1.2 Синхронные RS - триггеры

В результате явления “состязаний” (“гонок”) на входах асинхронного RS - триггера временно могут появляться ложные комбинации, которые вызовут ошибочные срабатывания (переключения) схемы и будут ложно зафиксированы логическим устройством обработки выходных сигналов триггера. Для устранения этого недостатка используют синхронные RS-триггеры, содержащие дополнительный тактовый (синхро) вход.

Синхронные RS - триггеры делятся на одноступенчатые (однотактные) и двухступенчатые (двухтактные).

Ниже показаны: обозначение на электрических схемах (рисунок 9.31,а) и принципиальные схемы (рисунок 9.31, б, в) однотактного синхронного RS-триггера.

А Б

В

Рисунок 9.31

Однотактный синхронный RS-триггер (рисунок 9.31, б, в) включает асинхронный RS-триггер DD3 и два дополнительных логических элемента DD1, DD2: И (рисунок 9.31, б) или И-НЕ (рисунок 9.31, в). Более предпочтительной является вторая схема (рисунок 9.31, в), т.к. она содержит элементы одного базиса И-НЕ (см. рисунок 9.30).

Однотактный (одноступенчатый) синхронный RS-триггер (рисунок 9.31) тактируется (синхронизируется) потенциалом или единичным импульсом на входе С.

Часто нужно осуществлять переключение триггера перепадом потенциала на его синхровходе С из 1 в 0 или из 0 в 1 (срезом или фронтом входного импульса). Синхронный RS-триггер, обладающий такой способностью, называется двухступенчатым (двухтактным).

Ниже показаны: обозначение на электрических схемах (рисунок 9.32, а) и принципиальная схема (рисунок 9.32, б) двухтактного синхронного RS-триггера, переключающегося перепадом из 1 в 0 на динамическом тактовом (синхро) входе.

А Б

Рисунок 9.32

Триггер выполнен на двух однотактных синхронных RS-триггерах, рассмотренных выше, и инверторе DD3. Вход С (рисунок 9.32, а) называется динамическим, т.к. активным сигналом на нем является перепад из 1 в 0. Переключение триггера происходит за два такта: в первом такте входная информация записывается в первый триггер DD1, а состояние второго триггера DD2 не изменяется, т.к. на его синхровход с выхода инвертора подается нулевой импульс. Во втором такте в момент окончания единичного импульса на входе (при перепаде из 1 в 0) с выхода инвертора на синхровход триггера DD2 начинает поступать единичный потенциал и информация из первого триггера DD1 переписывается во второй DD2. Таким образом, состояние выхода меняется лишь в момент перепада из 1 в 0 входного синхросигнала.

Ниже показаны: обозначение на электрических схемах (рисунок 9.33, а) и принципиальная схема (рисунок 9.33, б) двухтактного синхронного RS-триггера, переключающегося перепадом из 0 в 1 на динамическом синхровходе.

А Б

Рисунок 9.33

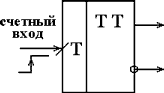

9.2.1.1.2 Т-триггеры (триггеры со счетным входом)

Такой триггер содержит счетный вход, обозначаемый буквой Т, и переключается каждым импульсом на этом входе (счетным импульсом).

Ниже показаны: обозначение на электрических схемах (рисунок 9.34, а) и принципиальная схема (рисунок 9.34, в) Т-триггера, переключающегося перепадом из 1 в 0 каждого входного импульса.

А Б

В

Рисунок 9.34

Триггер выполнен на основе двухтактного синхронного двухступенчатого RSC-триггера с динамическим синхровходом, охваченного двумя обратными связями.

В момент среза счетных входных импульсов триггер переключается в противоположное состояние  . На рисунке 9.35 приведены временные диаграммы, поясняющие работу Т-триггера. Исходное состояние схемы – единичное (UQ=1). Срезом каждого счетного импульса выходной сигнал меняет свое значение. Период выходных импульсов ТВЫХ = 2 ТВХ, а частота следования fВЫХ = fВХ/2, т.е. Т-триггер делит входную частоту на 2.

. На рисунке 9.35 приведены временные диаграммы, поясняющие работу Т-триггера. Исходное состояние схемы – единичное (UQ=1). Срезом каждого счетного импульса выходной сигнал меняет свое значение. Период выходных импульсов ТВЫХ = 2 ТВХ, а частота следования fВЫХ = fВХ/2, т.е. Т-триггер делит входную частоту на 2.

Рисунок 9.35

На рисунке 9.34, б приведено обозначение на электрических схемах Т-триггера, переключающегося перепадом из 1 в 0 на счетном входе.

9.2.1.1.3 D-триггеры (триггеры задержки)

Содержат информационный (D) вход и тактовый (синхро, С) вход (рисунок 9.36).

А Б

Рисунок 9.36

Существуют однотактные D-триггеры (рисунок 9.36, а), которые переключаются потенциалом или импульсом на тактовом входе, и двухтактные D-триггеры, которые переключаются динамическим сигналом (перепадом), например, из 1 в 0 (рисунок 9.36, б).

Ниже показаны: принципиальная схема (рисунок 9.37, а) и временные диаграммы работы (рисунок 9.37, б) однотактного D-триггера, выполненного на однотактном синхронном RS-триггере (RSC-триггере - DD1) и логическом элементе DD2.

А Б

Рисунок 9.37

В момент прихода тактового импульса D-триггер переключается в состояние, определяемое сигналом на информационном входе D, т.е. схема запоминает сигнал на входе D в момент поступления синхроимпульса (Qt+1 = D) и хранит его до следующего тактового импульса. Задержка равна интервалу времени между моментами прихода информационного сигнала на D-вход и поступлением синхросигнала на С-вход: tзад1 = t2 - t1; tзад2 = t4 - t3 (рисунок 9.37, б). D-триггеры широко применяются в качестве элементов памяти, способных хранить 1 бит информации.

Ниже показаны: обозначение на электрических схемах (рисунок 9.38, а) и принципиальная схема (рисунок 9.38, б) двухтактного D-триггера, переключающегося перепадом из 1 в 0 на динамическом синхровходе С.

А Б

В

Рисунок 9.38

Триггер выполнен на основе двух однотактных RSC-триггеров (DD1, DD2) и двух инверторов (DD3, DD4).

D-триггер можно использовать в качестве триггера со счетным входом (Т-триггера), если соединить его выводы как показано на рисунке 9.38, в.

9.2.1.1.4 JK-триггеры

Является наиболее универсальным среди синхронных триггеров.

Ниже показаны: обозначение на электрических схемах (рисунок 9.40, а), принципиальная схема (рисунок 9.40, б), таблица истинности (таблица 9.13) и временные диаграммы работы (рисунок 9.40, в) двухтактного синхронного JK-триггера, переключающегося перепадом из 1 в 0 на динамическом синхровходе С.

А Б

В

Рисунок 9.40

Таблица 9.13

| № набора | J | K | C | Qt+1 |

| 0 | 0 | 0 |

| Qt |

| 1 | 0 | 1 |

| 0 |

| 2 | 1 | 0 |

| 1 |

| 3 | 1 | 1 |

|

|

Рассмотрим работу JK-триггера. Исходное состояние схемы - нулевое (UQ = 0) (рисунок 9.40, в). При поступлении среза первого тактового импульса (момент t1) сигнал на J-входе равен 1, а на К-входе - 0. Поэтому триггер переключается в единичное состояние. Срезом второго тактового импульса схема переключается в нулевое состояние (момент t2), т.к. в это время J=0, а К=1. В момент t3 оба управляющих сигнала J=K=0, поэтому состояние схемы не изменяется (Qt+1 = Qt). При поступлении среза 4-го синхроимпульса (момент t4) J=K=1, поэтому триггер переключается в положение, противоположное исходному:

На основе универсального JK-триггера может быть построен ряд других триггеров.

Синхронный RS-триггер. Отождествим J=S и K=R. При запрете комбинации J=S=1 и K=R=1 таблица 9.13 сводится к таблице истинности RS-триггера (таблица 9.11). Поэтому рассмотренная схема (рисунок 9.40) может использоваться в качестве двухтактного синхронного RS-триггера.

Счетный Т-триггер. В нем используется только 4-я строка таблицы 9.13. Для этого входы J и K присоединяются к потенциалу, соответствующему логической единице: J=K=1 (рисунок 9.41, а).

А Б

Рисунок 9.41

D-триггер. В этом триггере  , т.е. помимо тактового имеется только один вход D (рисунок 9.41, б). Из таблицы 9.13 (2-я и 3-я строки) видно, что в D-триггере Qt+1 = D, т.е. последний запоминает сигнал на входе D в момент среза тактового импульса и хранит его до следующего синхросигнала.

, т.е. помимо тактового имеется только один вход D (рисунок 9.41, б). Из таблицы 9.13 (2-я и 3-я строки) видно, что в D-триггере Qt+1 = D, т.е. последний запоминает сигнал на входе D в момент среза тактового импульса и хранит его до следующего синхросигнала.

9.2.1.2 Триггеры в интегральном исполнении

В современных сериях ИМС существует большое число различных триггеров.

Ниже в качестве примера показаны обозначения двух широко используемых триггеров, выпускаемых в виде интегральной микросхемы (рисунок 9.42). Микросхема К555 ТМ2 включает два D-триггера с дополнительными S и R входами для установки схемы в исходное состояние (рисунок 9.42, а). Активными сигналами на S и R входах являются низкие уровни напряжений (логические нули).

Микросхема К555 ТВ1 (рисунок 9.42, б) содержит один JK-триггер, включающий два асинхронных R и S входа для установки схемы в исходное состояние и два дополнительных трехвходовых конъюнктора, включенных на J и K входах. Дополнительные элементы И реализуют логические функции

J = J 1. J 2. J 3 , K = K 1. K2. K3.(9.19)

Рисунок 9.42

Это расширяет возможности JK-триггера, например, упрощает построение синхронных счетчиков на подобных микросхемах.

9.2.2 Регистры

Регистрами называют последовательностные цифровые устройства, предназначенные для запоминания многоразрядных цифровых кодов и выполнения над ними некоторых логических преобразований. Основу регистров составляют триггеры, количество которых равно числу разрядов цифрового кода. Один триггер хранит 1 бит информации (один двоичный разряд), соответственно N-разрядный регистр способен хранить N бит информации. Кроме триггеров регистры содержат вспомогательные схемы, обеспечивающие прием кода в регистр, выдачу кода из регистра, сдвиг кода вправо или влево на требуемое число разрядов, преобразованиепараллельного кода в последовательный и наоборот, выполнение над отдельными разрядами регистра логических операций, например, И, ИЛИ, исключающее ИЛИ, установку регистра в начальное состояние (“СБРОС”) и др.

В зависимости от способа ввода и вывода разрядов числа регистры делятся на:

параллельные;

последовательные;

последовательно-параллельные;

параллельно-последовательные.

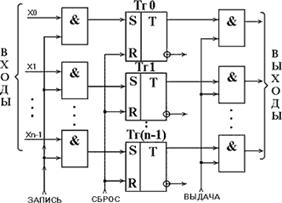

9.2.2.1 Параллельные регистры

В таких регистрах ввод и вывод информации осуществляется в параллельной форме – одновременно всех разрядов.

Рисунок 9.43

В зависимости от числа входных и выходных каналов параллельные регистры делятся на однофазные (каждый разряд передается по одному каналу в прямом коде) и парафазные (разряды передаются по двум каналам в прямом и обратном кодах).

На рисунке 9.43 показан пример двух параллельных регистров с парафазным вводом-выводом, выполненных на однотактных синхронных RSC-триггерах.

Рисунок 9.44

При парафазном обмене информацией на R, S входах любого триггера всегда присутствует комбинациясигналов Xi=1,  , либо

, либо  , устанавливающая его в требуемое состояние независимо от того, в каком состоянии этот триггер находился до этого, т.е. установка регистра в исходное состояние не требуется.

, устанавливающая его в требуемое состояние независимо от того, в каком состоянии этот триггер находился до этого, т.е. установка регистра в исходное состояние не требуется.

Под действием сигнала ПРМ Рг1 (прием в регистр 1) n-разрядный код записывается в регистр Рг1, а сигналом ПД Рг2 (передача в регистр 2) – передается в Рг2.

На рисунке 9.44 показан параллельный регистр, с однофазным обменом информации, выполненный на асинхронных RS-триггерах и конъюнкторах.

Так как информационные сигналы, поступающие только на S входы, не могут установить соответствующие триггеры в состояние 0 (из-за чего число может быть записано с ошибкой), то перед записью все триггеры регистра обнуляются сигналом “СБРОС”.

Следует отметить, что данная особенность характерна только для регистров с однофазной записью, выполненных на RS-триггерах. Если в качестве элемента памяти использовать D-триггеры, то их предварительное обнуление при однофазной записи не требуется (рисунок 9.45).

Рисунок 9.45

9.2.2.2 Последовательные (сдвигающие) регистры

В таких регистрах триггеры соединены последовательно, и число вводится и выводится последовательно разряд за разрядом (рисунок 9.46).

Рисунок 9.46

Рассматриваемый в примере последовательный регистр выполнен на D-триггерах. Записываемое в него число поступает по одному общему информационному входу Х в последовательном коде (значения разрядов передаются последовательно друг за другом). При поступлении первого импульса сдвига на синхровходы в каждом триггере записывается значение логического сигнала на его входе: Q 0 t +1 = X ; Q 1 t +1 = Q 0 t ; Q 2 t +1 = Q 1 t .

Эта информация хранится до поступления второго импульса сдвига, после чего записанный перед этим код сдвинется вправо на один разряд, а в триггер Тг0 запишется новое значение входного информационного сигнала. Третий импульс сдвига вновь сдвинет содержимое регистра вправо на один разряд и запишет в Тг0 информационный бит.

Сказанное иллюстрируют временные диаграммы работы, на которых предполагается, что все триггеры регистра находятся в нулевом исходном состоянии (рисунок 9.47).

Рисунок 9.47

Анализируя работу последовательного регистра можно отметить следующее:

1) поступившее на вход Х регистра число 101 после третьего импульса на входе С оказываетсязаписанным в разрядах триггера: Q 3 =1, Q 2 =0, Q 1 =1. В общем случае, n - разрядный регистр заполняется n - разрядным числом за n тактовых импульсов;

2) поступивший на вход Х последовательный код преобразуется в регистре в параллельный код, и записанное число может быть считано с выходов триггеров Q3, Q2, Q1 параллельно (одновременно);

3) с поступлением каждого тактового импульса на вход С записанная в регистр информация сдвигается (движение происходит от входа к выходу), поэтому последовательный регистр называется сдвигающим регистром (регистром сдвига);

4) информация, записанная в последовательный регистр, может быть считана с его выхода (на рисунке 9.46 – Q2) в последовательном коде. Для этого после записи данных в регистр необходимо вновь подавать тактовые импульсы на вход С. Число поразрядно будет появляться на выходе (Q2 на рисунке 9.46) и оттуда может приниматься считывающим устройством.

Последовательный регистр осуществляет не только запись и хранение информации, но и преобразование формы ее представления.

9.2.2.3 Регистры сдвига

Эти регистры широко применяются в микропроцессорах, однокристальных микро ЭВМ, устройствах управления для сдвига записанной в них информации влево и вправо на заданное количество разрядов. Сдвиг кодов может использоваться при выполнении операций умножения и деления. Известно, что сдвиг двоичного числа влево на один разряд эквивалентен умножению на два, а сдвиг вправо на один разряд – делению на два. При этом разряды, выходящие за пределы разрядной сетки, теряются, а в освободившиеся в процессе сдвига младшие разряды записываются нули. На рисунке 9.48 приведена схема трехразрядного регистра сдвига вправо на двухтактных D-триггерах, содержащих S-входы для записи исходного числа (а0 – МЗР ДК, а а2 – СЗР ДК).

Рисунок 9.48

Если, например, записать в регистр двоичное число 110В=6D и подать на С-вход один импульс сдвига, то после этого схема займет состояние: Q2 =0, Q1 = Q0 =1, что соответствует числу 3. Т.е. произошло деление исходного числа шесть на два.

Если соединить выход крайнего правого разряда регистра с входом крайнего левого разряда, то получим схему кольцевого (циклического) регистра сдвига.

9.2.2.4 Последовательно-параллельные и параллельно-последовательные регистры

Эти устройства выполняются на основе последовательного регистра, дополненного соответствующей логикой, и предназначены для преобразования последовательного кода в параллельный и наоборот.

В последовательно-параллельный регистр информация записывается в последовательном многоразрядном коде, а затем параллельно считывается со всех разрядов сигналом управления.

В параллельно-последовательный регистр данные записываются параллельно во все разряды, а считывание информации осуществляется в последовательной форме разряд за разрядом.

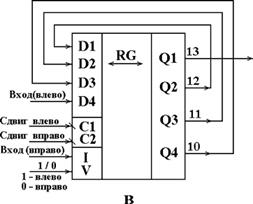

9.2.2.5 Регистры в интегральном исполнении

В современных сериях ИМС широко представлены разнообразные регистры. Рассмотрим в качестве примера один из них - К555ИР1, представляющий 4-разрядный универсальный регистр (рисунок 9.49, а, б). Эта микросхема содержит четыре тактируемые перепадом из 1 в 0 D-триггера, соединенные последовательно с помощью элементов И-ИЛИ. Если на вход V регистра подан сигнал “нуль”, то выход каждого предыдущего триггера через ячейку И-ИЛИ соединяется с входом D последующего. При этом импульсы, приходящие на тактовый вход С2, будут каждый раз устанавливать последующий триггер в состояние, в котором до этого находился предыдущий. Вход I регистра, связанный с входом D первого триггера, служит для приема информации в последовательном коде. Перед приходом очередного тактового импульса на вход I должно подаваться новое значение входного двоичного разряда. После приема четырех бит последовательного кода соответствующий ему параллельный код может быть получен с выходов триггеров Q1...Q4.

Запись в регистр информации в параллельной форме осуществляется с входов D1...D4 при подаче тактового импульса на вход С1 и значении управляющего сигнала V=1. Устанавливая затем V=0 и подавая тактовые импульсы на вход С2, можно осуществлять сдвиг записанного кода. При этом с выхода Q4 снимается последовательный двоичный код.

Рассматриваемые регистры могут использоваться для сдвига информации как вправо, так и влево (как реверсивные). Для этого необходимо попарно соединить выводы Q4 и D3, Q3 и D2, Q2 и D1 (рисунок 9.49, в). Вход V в этом случае играет роль переключателя направления сдвига. При V=0 и поступлении сигналов синхронизации на вход С2 последовательный код подается на вход I и осуществляется сдвиг вправо. Если V=1, а последовательный код поступает на вход D4, то синхросигналами на входе С1 производится сдвиг кода влево.

Рисунок 9.49

Это ПЦУ, предназначенные для счета поступающих на их вход импульсов. В паузах между импульсами счетчик хранит в двоичном коде информацию о количестве уже поступивших импульсов. Максимальное число, которое может быть записано в счетчике, равно (2n-1), где n – число разрядов счетчика. Каждый разряд включает триггер. Наиболее просто счетчики строятся на триггерах со счетным входом (Т-триггерах).

Однако для их построения могут применяться не только триггеры со счетным входом, но также D- и JK-триггеры.

Основным параметром счетчика является модуль счета (коэффициент пересчета) Ксч, определяемый максимальным числом единичных сигналов, которое может быть посчитано. N-разрядный двоичный счетчик может находиться в состояниях 0, 1, 2,..., (2n-1). При поступлении на вход суммирующего счетчика 2n -й единицы он переходит из состояния (2n-1) в состояние 0. Следовательно, его модуль счета Ксч = 2n. Т. е. в зависимости от числа разрядов такой счетчик может посчитать 2, 4, 8, 16,... единиц и сформировать на выходе сигнал переноса. Через 2, 4, 8, 16... импульсов на входе, на выходе Q (или  ) будет перепад из 1 в 0 или из 0 в 1, который сигнализирует о конце счета. Однако в ряде случаев требуется, чтобы коэффициент пересчета отличался от 2n. Широкое распространение получили, например, десятичные счетчики, для которых Ксч = 10. Такой счетчик после каждого 10-го импульса возвращается в исходное состояние, формируя при этом на выходе сигнал переноса. Количество разрядов n счетчика с произвольным коэффициентом пересчета определяется из условия

) будет перепад из 1 в 0 или из 0 в 1, который сигнализирует о конце счета. Однако в ряде случаев требуется, чтобы коэффициент пересчета отличался от 2n. Широкое распространение получили, например, десятичные счетчики, для которых Ксч = 10. Такой счетчик после каждого 10-го импульса возвращается в исходное состояние, формируя при этом на выходе сигнал переноса. Количество разрядов n счетчика с произвольным коэффициентом пересчета определяется из условия

2n-1 < Ксч < 2n . (9.20)

Очевидно, что для Ксч = 10 требуемое число разрядов n = 4. Обычный двоичный четырехразрядный счетчик имеет 24 = 16 различных устойчивых состояний. Следовательно, для Ксч = 10 имеется N = 16 - 10 = 6 избыточных состояний, которые необходимо исключить.

Кроме значения модуля счета счетчики можно классифицировать еще по ряду признаков.

В зависимости от направления счета различают

суммирующие (с прямым счетом),

вычитающие (с обратным счетом),

реверсивные (с прямым и обратным счетом)

счетчики.

По способу организации схемы переноса различают счетчики с

последовательным,

параллельным (сквозным),

параллельно-последовательным

переносом.

В зависимости от особенностей переключения отдельных триггеров счетчики делятся на:

асинхронные,

синхронные.

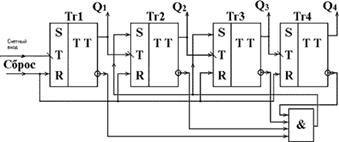

9.2.3.1 Асинхронный суммирующий двоичный счетчик с последовательным переносом

В качестве примера рассмотрим 3-х разрядный счетчик, выполненный на двухтактных Т-триггерах с дополнительным R-входом для установки исходного нулевого состояния (рисунок 9.50).

Рисунок 9.50

На рисунке 9.51 показаны временные диаграммы работы схемы.

Рисунок 9.51

Подачей единичного сигнала на вход УИС все триггеры устанавливаются в исходное нулевое состояние. Срезом каждого входного импульса переключается триггер младшего разряда Тг1. Срезом сигналов UQ1 переключается триггер второго разряда Тг2. Срез импульсов на выходе Q2 вызывает переключение триггера третьего разряда Тг3 (рисунок 9.51).

Анализируя временные диаграммы можно сделать ряд выводов:

1) частота импульсов на выходе каждого триггера вдвое меньше частотыимпульсов на его входе. N-разрядный счетчик делит частоту входных импульсов в 2n раз. С наибольшей частотой, равной частоте входных импульсов, переключается входной триггер счетчика;

2) в момент, предшествующий переключению очередного триггера, все предыдущие разряды счетчика находятся в единичном состоянии;

3) восьмой импульс для трехразрядного счетчика (рисунок 9.51) является импульсом переполнения, которым все триггеры устанавливаются в нуль (счетчик “обнуляется”). Девятым импульсом счетчик вновь начинает заполняться;

4) максимальное число импульсов, которое может зафиксировать схема, равно (2n - 1). В нашем примере n = 3 и в счетчик можно записать 7 импульсов.

5) если использовать сигнал переноса, формируемый на выходе, то счетчик может посчитать 2 n импульсов. Если n=3, то Ксч=23=8.

Работу счетчика отражает таблица 9.14.

Таблица 9.14

| № импульса | Q3 | Q2 | Q1 |

| 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 2 | 0 | 1 | 0 |

| 3 | 0 | 1 | 1 |

| 4 | 1 | 0 | 0 |

| 5 | 1 | 0 | 1 |

| 6 | 1 | 1 | 0 |

| 7 | 1 | 1 | 1 |

| 8 | 0 | 0 | 0 |

Нетрудно заметить, что состояние триггеров (разрядов) представляет собой запись числа поступивших импульсов в двоичном коде.

В рассмотренном счетчике каждый последующий триггер переключается сигналом переноса, формируемым на выходе предыдущего разряда, поэтому схема называется счетчиком с последовательным переносом. Переключение отдельных триггеров происходит последовательно друг за другом (не одновременно, асинхронно), поэтому такой счетчик называется асинхронным.

9.2.3.2 Асинхронный вычитающий двоичный счетчик с последовательным переносом

Счетчик, работающий на вычитание, строится аналогично суммирующему, рассмотренному выше. Отличие состоит лишь в том, что на счетный вход триггера i-го разряда (i = 1, 2, 3,...(n-1), где n-число разрядов счетчика) подается сигнал с инверсного выхода предыдущего разряда, т.е.  (рисунок 9.52).

(рисунок 9.52).

Рисунок 9.52

Т-триггеры, на которых выполнена рассматриваемая схема, переключаются перепадом сигнала из 1 в 0 на входе. Это значит, что переключение триггера i-го разряда будет происходить при срезе импульса  , т.е. при фронте Q i-1 (момент нарастания Q i-1 от 0 к 1). Работу вычитающего счетчика отражает таблица 9.15. В начале работы подачей единичных сигналов на установочные S-входы триггеров установлено исходное состояние счетчика Q1=Q2=Q3=1.

, т.е. при фронте Q i-1 (момент нарастания Q i-1 от 0 к 1). Работу вычитающего счетчика отражает таблица 9.15. В начале работы подачей единичных сигналов на установочные S-входы триггеров установлено исходное состояние счетчика Q1=Q2=Q3=1.

Таблица 9.15

| № импульса | Q3 | Q2 | Q1 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 1 | 0 |

| 2 | 1 | 0 | 1 |

| 3 | 1 | 0 | 0 |

| 4 | 0 | 1 | 1 |

| 5 | 0 | 1 | 0 |

| 6 | 0 | 0 | 1 |

| 7 | 0 | 0 | 0 |

| 8 | 1 | 1 | 1 |

Каждым входным импульсом число, записанное в счетчик, уменьшается на единицу. Состояния разрядов счетчика представляют собой двоичную запись линейно-убывающих чисел. Следует обратить внимание, что если при поступлении очередного импульса в счетчике записаны нули, то очередным состоянием схемы будут все единицы.

9.2.3.3 Асинхронные реверсивные двоичные счетчики с последовательным переносом

Часто возникает необходимость, чтобы счетчики обладали способностью выполнять сложение или вычитание, т.е. были реверсивными.

В таких счетчиках объединяются схемы суммирующего и вычитающегосчетчиков. Реверсивные счетчики могут иметь два или один входа для подачи счетных сигналов.

Ниже показана схема реверсивного асинхронного счетчика имеющегоодин счетный вход (рисунок 9.53).

Рисунок 9.53

Единичным управляющим сигналом на входе +1 или -1 счетчик настраивается на работу в режиме суммирования (на входе +1 – единица, а на выходе -1 – нуль) или в режиме вычитания (на входе +1 – нуль, -1 – единица).

Асинхронные счетчики имеют простую структуру, но обладают рядом недостатков:

1) схема имеет сравнительно низкое быстродействие, т.к. при поступлении каждого счетного импульса триггеры переключаются последовательно и к i-му разряду переключающий сигнал проходит через (i-1) предыдущих. Поэтому интервал меду соседними входными импульсами должен превышать tпер∙(n-1), где tпер - время переключения одного триггера, а n - число разрядов счетчика.

2) в ходе переключения младшие разряды принимают уже новые состояния, в то время как старшие еще находятся в прежнем. Т.е. при смене одного числа другим счетчик проходит ряд промежуточных состояний, каждоеиз которых может быть ошибочно принято за двоичный код числа поступивших на вход импульсов.

Когда для устройства, в состав которого входит счетчик, отмеченные недостатки являются существенными, используют синхронные счетчики.

9.2.3.4 Синхронный счетчик со сквозным переносом

В таких счетчиках состояние триггеров изменяется одновременно под действием сигналов синхронизации на входах всех триггеров.

На рисунке 9.54 приведен суммирующий синхронный счетчик, выполненный на JK-триггерах.

Рисунок 9.54

В схеме с помощью конъюнкторов организован так называемый сквозной (параллельный) перенос. Его идея состоит в том, что сигнал переноса поступает на J, K входы последующих триггеров лишь в том случае, если предыдущие находятся в состоянии единица. Триггер Тг1 переключается каждым счетным импульсом, т.к. на его J и K входы постоянно подается единица. Остальные триггеры переключаются счетными импульсамипри следующих условиях: Тг2 - при Q1=1; Тг3 - при Q1=1; Q2=1; Тг4 - при Q1=1; Q2=1; Q3=1.

Недостатком описанного счетчика является необходимость иметь конъюнкторы с большим количеством входов, число которых возрастает с увеличением числа разрядов. Если число разрядов синхронного счетчика не превышает четыре, то схему можно реализовать без внешних конъюнкторов, используя JK-триггеры с входной логикой И.

Ниже показана схема суммирующего синхронного счетчика, у которого число разрядов равно трем (рисунок 9.55).

Рисунок 9.55

Аналогично может быть построен вычитающий синхронный счетчик со сквозным переносом (рисунок 9.56).

Рисунок 9.56

Реверсивный синхронный счетчик со сквозным переносом приведен на рисунке 9.57.

Рисунок 9.57

Схема содержит один источник сигналов счета и два управляющих входа для переключения счетчика на суммирование (+1) или вычитание (-1). На выходе счетчика, обозначенном >7, единичный сигнал появляется при поступлении седьмого импульса и переходе счетчика в состояние, в котором все триггеры установлены в 1. Следующим восьмым импульсом на этом выходе появляется сигнал переноса в следующий разряд в виде перепада из 1 в 0.

На выходе <0 единичный сигнал появляется при установке всех триггеров в нулевое состояние и приходе очередного вычитающего импульса. При этом все триггеры устанавливаются в единицу, а на выходе <0 появляетсясигнал заема в виде перепада из 1 в 0.

9.2.3.5 Десятичные счетчики

Как отмечалось ранее, в двоичных счетчиках коэффициент пересчета (счета), т.е. число различных устойчивых состояний, равен 2n, где n - число разрядов. Однако в ряде случаев требуется, чтобы коэффициент пересчета счетчика был отличным от этого значения. Широкое распространение получили, например, десятичные счетчики, для которых Ксч = 10. Такой счетчик после каждого десятого импульса возвращается в исходное состояние, формируя при этом на выходе импульс переноса. Разрядность счетчика с произвольным коэффициентом пересчета (не равным 2n) определяется из условия

2n-1 < Ксч < 2n. (9.21)

Очевидно, что для Ксч = 10 требуется число разрядов n = 4. Поскольку двоичный 4-х разрядный счетчик имеет 16 различных устойчивых состояний, то для реализации схемы с Ксч = 10 необходимо исключить N = 16 - 10 = 6 избыточных состояний. Это можно осуществить путем введения обратных связей с выхода счетчика на единичные входы триггеров тех разрядов, которые в двоичномпредставлении числа N содержат единицы. Так, для N = 610 = 01102 сигнал обратной связи следует подать на единичные входы триггеров второго и третьего разрядов.

Рисунок 9.58

На рисунке 9.58 изображена функциональная схема, а в таблице 9.16 приведены состояния десятичного счетчика.

Одновибратор необходим, так как без него на выходе Q 4 после прихода каждого десятого импульса будет 0, а на  – 1. Если эту единицу использовать как установку Тг2 и Тг3 в единицу, то при приходе очередного счетного импульса на S входе будет 1, чего допустить нельзя.

– 1. Если эту единицу использовать как установку Тг2 и Тг3 в единицу, то при приходе очередного счетного импульса на S входе будет 1, чего допустить нельзя.

Таблица 9.16

| № импульса | Состояние триггеров | № импульса | Состояние триггеров | ||||||

| Q4 | Q3 | Q2 | Q1 | Q4 | Q3 | Q2 | Q1 | ||

| 0 | 0 | 1 | 1 | 0 | 6 | 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 | 7 | 1 | 1 | 0 | 1 |

| 2 | 1 | 0 | 0 | 0 | 8 | 1 | 1 | 1 | 0 |

| 3 | 1 | 0 | 0 | 1 | 9 | 1 | 1 | 1 | 1 |

| 4 | 1 | 0 | 1 | 0 | 10 | 0 | 1 | 1 | 0 |

| 5 | 1 | 0 | 1 | 1 | 11 | 0 | 1 | 1 | 1 |

Перед началом работы импульсом “сброс” счетчик обнуляется, а затем сигналом УИС в триггеры ТГ1, Тг3 записываются единицы, т.е. счетчик устанавливается в исходное состояние 01102, что соответствует числу 6D. Послеприхода девятого импульса схема переключится в состояние 11112, а затем очередной (десятый) импульс формирует на выходе (Q4) сигнал переноса (перепад из 1 в 0). Этим сигналом запускается одновибратор ОВ, формирующий короткий единичный импульс, который до прихода очередного счетного импульса вновь установит счетчик в исходное состояние 01102.

Далее описанный процесс повторяется, и счетчик имеет 10 устойчивых состояний (Ксч = 10) и формирует на выходе сигнал переноса после прихода каждого 10-го импульса.

Рисунок 9.59

Рассмотренную схему (рисунок 9.58) можно упростить без изменения логики ее функционирования. Вместо одновибратора и двух дизъюнкторов вводится один четырехвходовый конъюнктор (рисунок 9.59), который обеспечивает установку счетчика в состояние 01102 вначале работы и при поступлении 10-го импульса, когда все триггеры переключаются в нулевое состояние.

Существует еще ряд способов исключения избыточных состояний, например, используя принудительное обнуление схемы при достижении счетчиком состояния, равного Ксч.

Схема десятичного счетчика, построенная по данному способу, показана на рисунке 9.60.

Рисунок 9.60

Перед началом счета сигналом УИС все триггеры счетчика устанавливаются в исходное нулевое состояние. При поступлении на счетный вход 10 импульсов навыходах Q2 и Q4 установятся единицы, благодаря чему единичным сигналом с выхода конъюнктора все триггеры вновь будут сброшены в 0. При этом на выходе счетчика (Q4) первый раз появится сигнал переноса (перепад из 1 в 0), свидетельствующий о том, что на вход счетчика пришло десять импульсов. Далее описанный процесс повторяется.

9.2.3.6 Счетчики в интегральном исполнении

В различных сериях интегральных микросхем широко представлены счетчики [3, 4]. В качестве примера рассмотрим ИМС К555ИЕ7, которая представляет собой двоичный 4-х разрядный реверсивный счетчик (рисунок 9.61).

Рисунок 9.61

Микросхема содержит два входа для счетных импульсов. Если счетчик работает как суммирующий, то счетные импульсы подаются на вход С+, а если как вычитающий – то на С-, причем на неиспользуемом счетном входе должно быть напряжение высокого уровня. В качестве очередного счетного импульса на одном из входов С+ или С- воспринимается срез нулевого импульса (перепад из 0 в 1).

Счетчик содержит асинхронный вход установки в нуль R и входы параллельной записиисходной кодовой комбинации D1...D4. Эта запись производится при наличиинулевых сигналов на входах R и V (загрузка).

На выходе >15 формируется сигнал переноса при суммировании входных импульсов, когда их число превышает 15, а на выводе <0 - сигнал заема привычитании, когда очередной импульс на вход С - поступает при нулевом состоянии счетчика. Эти сигналы представляют перепад из 0 в 1 и являются ответными на срез (перепад из 0 в 1) нулевых входных счетных импульсов.

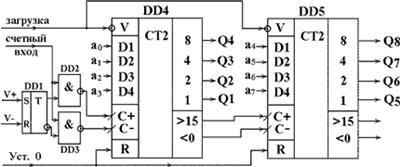

Путем последовательного соединения четырехразрядных счетчиков К555ИЕ7 можно построить двоичные реверсивные счетчики с большим числом разрядов.

На рисунке 9.62 показан пример построения 8-разрядного реверсивного счетчика на двух 4-разрядных типа К555ИЕ7.

Рисунок 9.62

Счетчик содержит один счетный вход и два сигнала управления V+ и V-, определяющие, в каком режиме предполагается использовать схему - в режиме суммирования (V+=1, V- =0) или вычитания (V+=0, V- =1). Для управления микросхемой К555ИЕ7, содержащей два счетных входа С+ и С-, в устройство включены асинхронный RS-триггер (DD1) и два конъюнктора (DD2, DD3).

При подаче единичного сигнала на вход V+ (при V- =0) RS-триггерустанавливается в 1 и счетные импульсы через DD2 поступают на вход С+ микросхемы СТ2 (DD4). При поступлении единичного сигнала на вход V- (при V+=0) RS-триггер сбрасывается в нуль и счетные импульсы через DD3 подаются на вход С - микросхемы СТ2(DD4). Когда рассматриваемая схема производит суммирование входных импульсов, то сигнал переноса (перепад из0 в 1) появляется на выходе >15 второй микросхемы СТ2(DD5) при поступлении на вход 256-гоимпульса (при условии, что счет начинался с нулевого значения). Сигнал заема на выходе <0 второй схемы СТ2(DD5) (перепад из 0 в 1) появляется припоступлении на счетный вход 256-го вычитающего импульса (при условии, что вычитание начиналось с единичных значений во всех разрядах). При этом происходит вычитание из нуля единицы, и все триггеры счетчика вновь устанавливаютсяв единицу.

9.2.4 Делители частоты

В делителях частоты входная периодическая последовательность импульсовделится на заданное число.

В качестве делителя частоты можно использовать счетчик, коэффициент пересчета которого Ксч определяет число, на которое делится частота входных счетных импульсов. Особенность делителя состоит в том, что он имеет один выход.

Коэффициент деления Кдел=Ксч может иметь постоянное или изменяемое (переменное) значение.

Делители с переменным коэффициентом деления (ДПКД) могут быть построены по различным схемотехническим вариантам. Например, с предустановкой исходного состояния, от которого ведется счет, до переполнения счетчика, либо с установкой заданного промежуточного значения, до которого, начиная с нулевого, ведется счет входных импульсов, а затем результат сбрасывается и начинаетсяновый счетный цикл. Примеры счетчиков работающих по описанным правилам рассмотрены в [3, 4].

Пример ДПКД, построенного по первому варианту (с предустановкой исходного состояния) приведены на рисунке 9.63.

Рисунок 9.63

Делитель выполнен на основе микросхемы четырехразрядного двоично/десятичного реверсивного счетчика К561ИЕ14. На входы предустановки D1...D4 подается код, соответствующий числу “лишних”состояний (24 - Кдел). Выход сигнала переноса Р соединяют через инвертор DD1 с управляющим входом V (загрузка). Сигналом 1 на этом входе число с входов D1...D4 записывается втриггеры счетчика. На входы +/- и 2/10 подаются единичные сигналы,настраивающие ИМС на работу в режиме суммирующего двоичного счетчика. Чтобы разрешить счет вход Po соединяют с землей (нулевым потенциалом). Подвоздействием входных импульсов на входе С счетчик-делительпоследовательно проходит состояния от исходного, предварительно установленного по входам D1...D4, до конечного, когда он заполняется единицами во всех четырех разрядах. Следующим импульсом после этого схема сбрасывается в нуль и формируется сигнал переноса на выходе Р. Этим сигналом разрешается запись в счетчик исходного кода и цикл вновь повторяется. С выхода схемы снимается последовательность импульсов с частотой

f вых = f вх / Кдел.(9.22)

Для рассматриваемого устройства Кдел принимает значения от 1 до 16.

На рисунке 9.64 приведен пример делителя, построенного по второму варианту.

Рисунок 9.64

Основу ДПКД составляет двоичный счетчик (DD2), который начинает счет с нулевого значения и продолжает работу до установленного промежуточного состояния, равного требуемому коэффициенту деления Кдел. После этого счетчик вновь сбрасывается нуль и начинается новый цикл счета. Для определения момента достижения равенства кодов, определяющих промежуточное состояние счетчика и значение Кдел, в схеме использован цифровой компаратор (DD1). В момент равенства кодов А=В на выходе компаратора появляется логическая единица, сбрасывающая счетчик в исходное нулевое состояние. Дополнительный триггер (DD3) необходим для исключения возможности сбоя при установке нулевого состояния СТ2 из-за разброса временных параметров триггеровсчетчика. Сигналом с выхода компаратора FА=В триггер устанавливается в 1 и поддерживает на входе R счетчика единичный сигнал на время, достаточное для сброса всех разрядов DD2. Следующим входным импульсом триггер сбрасывается в нулевое состояние.Если разброс временных параметров триггеров счетчика невелик, то DD3 можно исключить.

Делитель с постоянным коэффициентом деления можно построить проще. Для этого компаратор заменяют конъюнктором, на входы которого подают выходные сигналы с тех разрядов счетчика, которые в кодовой комбинации, соответствующей Кдел, имеют высокий уровень. Пример делителя с Кдел = 9 показан на рисунке 9.65.

Рисунок 9.65

9.2.5 Распределители

ПЦУ, которое последовательно распределяет по выходам сигналы, поступающие на его вход, называется распределителем.

Ниже показаны: функциональная схема распределителя, выполненного на двоичном счетчике (DD1) и дешифраторе двоичного кода (DD2) (рисунок 9.66,а) и временные диаграммы, поясняющие его работу (рисунок 9.66,б).

Распределитель поочередно формирует импульсы на выходах.

Рисунок 9.66

Дата добавления: 2019-02-12; просмотров: 1149; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!