ФУНКЦИОНАЛЬНЫЕ УСТРОЙСТВА КОМПЬЮТЕРНОЙ (ЦИФРОВОЙ) ЭЛЕКТРОНИКИ

9.1 Комбинационные цифровые устройства (КЦУ)

Логические устройства, выходные сигналы которых однозначно определяются комбинацией входных логических переменных в рассматриваемый момент времени, называются комбинационными.

9.1.1 Анализ и синтез КЦУ

В процессе проектирования любого устройства выполняется ряд действий, которые можно отнести к задачам анализа и синтеза.

9.1.1.1 Анализ КЦУ

Выполнение задач анализа КЦУ предполагает наличие готовой функциональной схемы устройства на логических элементах заданного базиса. В процессе анализа оцениваются некоторые характеристики имеющейся схемы КЦУ. Например, можно составить булево выражение и таблицу истинности, определяющие преобразование информации в КЦУ; минимизировать логическую функцию, которую выполняет анализируемая схема; оценить аппаратные затраты на реализацию схемы; её быстродействие; потребляемую мощность; рассмотреть возможность образования в схеме ложных опасных состояний в результате состязаний (гонок) и др.

9.1.1.2 Синтез КЦУ

Синтез КЦУ предусматривает построение функциональной схемы устройства, т.е. определение состава необходимых логических элементов и соединений между ними, при которых обеспечивается преобразование входных цифровых сигналов в выходные в соответствии с заданными условиями работы устройства. В процессе синтеза необходимо минимизировать аппаратные затраты на реализацию устройства. Рассмотрим особенности синтеза КЦУ с одним выходом. Последовательность синтеза целесообразно разбить на ряд этапов.

|

|

|

Этап 1. Задание логической функции, определяющей функционирование синтезируемого КЦУ. Как отмечалось ранее, это можно сделать словесно, с помощью таблиц истинности или булевых выражений.

Этап 2. Минимизация логической функции, которая осуществляется алгебраическим или графическим методом (с помощью диаграмм Вейча, карт Карно).

Этап 3. Запись булевого выражения минимизированной переключательной функции.

Этап 4. Преобразование булевого выражения минимизированной ПФ для реализации её в заданном базисе И-НЕ или ИЛИ-НЕ.

Этап 5. Составление функциональной схемы КЦУ, т.е. изображение нужных логических элементов и связей между ними.

Проиллюстрируем этапы синтеза КЦУ на примере.

Необходимо синтезировать на элементах И-НЕ КЦУ на три входа, выходной сигнал которого совпадает с большинством входных сигналов.

Данное словесное описание задает логическую функцию МАЖОРИТАРНОСТЬ. Её работу отражает таблица истинности (таблица 9.1).

Таблица 9.1

| № набора | С | В | А | F |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 2 | 0 | 1 | 0 | 0 |

| 3 | 0 | 1 | 1 | 1 |

| 4 | 1 | 0 | 0 | 0 |

| 5 | 1 | 0 | 1 | 1 |

| 6 | 1 | 1 | 0 | 1 |

| 7 | 1 | 1 | 1 | 1 |

|

|

|

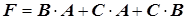

Булево выражение ПФ в СДНФ имеет вид

(9.1)

(9.1)

Минимизируя данное выражение, используя тождества и теоремы булевой алгебры, получим

.(9.2)

.(9.2)

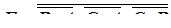

Преобразуем данное выражение для его реализации в базисе И - НЕ.

Применяя теорему де Моргана, получим

.(9.3)

.(9.3)

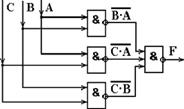

Функциональная схема синтезируемого КЦУ, реализующего выражение (9.3) на элементах И-НЕ, приведена на рисунке 9.1.

Рисунок 9.1

На практике широко применяются КЦУ, имеющие несколько выходов. При проектировании таких устройств можно воспользоваться рассмотренными выше правилами синтеза, если представить устройство в виде совокупности соответствующего числа КЦУ с общими входами.

Функционирование КЦУ с m-выходами описывается (задается) аналогичным количеством переключательных функций, над каждой из которых в процессе синтеза выполняются действия, описанные выше.

9.1.2 Типовые КЦУ

В цифровой технике при построении сложных устройств широко применяются не только отдельные логические элементы, реализующие элементарные булевы функции, но и их комбинации в виде типовых структур, выполняемых как единое целое в виде интегральных микросхем (ИМС). На входы таких структур могут подаваться информационные логические сигналы и сигналы управления. Последние могут определять, например, порядок передачи информационных входных сигналов на выход или играть роль сигналов синхронизации. Во многих случаях, особенно при использовании в устройствах выходных цепей с тремя состояниями, в качестве сигналов синхронизации выступают сигналы “Выбор микросхемы” (CS). Наличие активного значения такого сигнала управления (в одних схемах это логический нуль, в других - логическая единица) разрешает устройству выполнение заданных функций, отсутствие его - переводит схему в “невыбранное” состояние, при котором она не выполняет обработку информации, а её выходы отключены от нагрузки.

|

|

|

9.1.2.1 Шифраторы и дешифраторы

В повседневной жизни для представления чисел мы применяем десятичную систему счисления. Если последняя используется для представления дискретных сообщений (дискретной информации - данных), то говорят о кодировании – установлении соответствия между элементами данных и совокупностью символов, называемых кодовой комбинацией. В большинстве современных компьютеризированных систем управления и автоматики входная дискретная информация представлена в десятичном (унитарном) коде, а обработка информации цифровым компьютером осуществляется над данными, представленными в двоичном коде. Возникает задача преобразования десятичного (унитарного) кода в двоичный при вводе в систему и обратного перевода двоичного кода в десятичный (унитарный) при выводе из цифровой системы результатов обработки информации.

|

|

|

Комбинационное цифровое устройство (КЦУ), выполняющее перевод десятичного (унитарного) кода в двоичный, называется шифратором (кодером) двоичного кода, а осуществляющее преобразование двоичного кода в десятичный (унитарный) – дешифратором (декодером) двоичного кода.

Очень часто десятичные коды преобразуются в двоично-десятичные, которые называют BCD (Binary Code Decimal)-кодами или кодами 8421. В этом случае КЦУ, преобразующие десятичный код в BCD-код и наоборот, называют соответственно шифратором (кодером) и дешифратором (декодером) двоично-десятичного кода (BCD-кода).

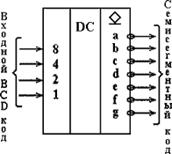

Распространенным выходным устройством, отображающим десятичные числа, является семисегментный индикатор. Его работой управляет дешифратор, преобразующий BCD-код в семисегментный. Рассмотрим названные устройства более подробно.

9.1.2.1.1 Шифраторы двоичного кода

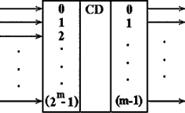

Шифраторы двоичного кода преобразуют десятичный (унитарный) код в двоичный. Если число разрядов выходного ДК (выходов шифратора) равно m, то максимальное число входных шин определяется числом возможных кодовых комбинаций ДК и составляет 2m .

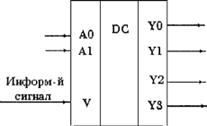

Условное обозначение шифратора показано на рисунке 9.2.

Рисунок 9.2

На выходных шинах устанавливается ДК, десятичный эквивалент которого соответствует номеру входа, на котором появилась логическая 1. На остальных входах при этом присутствуют нули. Такой код называют унитарным (десятичным).

Рассмотрим пример проектирования шифратора, у которого число разрядов выходного ДК m=2. Максимальное число входов равно 2m=22=4, что позволяет отобразить двухразрядным выходным двоичным кодом четыре десятичные цифры 0, 1, 2, 3. Иногда при проектировании шифраторов нулевой вход опускают, считая, что нулевой цифре на входе соответствуют пассивные сигналы (нули) на всех оставшихся входах. Активный входной сигнал – логическая 1. Принимая такой подход, составим таблицу истинности рассматриваемого в примере (рисунок 9.2.1) шифратора (таблица 9.2).

Таблица 9.2

| № набора | С | В | А | F2 | F1 |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 |

| 2 | 0 | 1 | 0 | 1 | 0 |

| 3 | 0 | 1 | 1 | – | – |

| 4 | 1 | 0 | 0 | 1 | 1 |

| 5 | 1 | 0 | 1 | – | – |

| 6 | 1 | 1 | 0 | – | – |

| 7 | 1 | 1 | 1 | – | – |

Рисунок 9.2.1

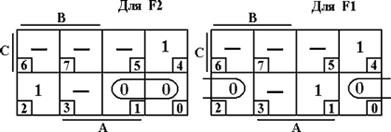

Минимизируем функции F2, F1 с помощью диаграмм Вейча (рисунок 9.3)

Рисунок 9.3

Если провести минимизацию по нулевым значениям функций F2, F1, получим минимальные КНФ:

F 2 = B + C , F 1 = C + A .(9.4)

В результирующие конъюнкции входят те переменные, которые в пределах накрытия не меняют своего значения (входят в прямой или инверсной форме). Переменные, которые находятся в столбцах и строках, не помеченных черточкой входят в прямой форме, а помеченные – в инверсной.

Принципиальная схема шифратора, реализующего эти уравнения, показана на рисунке 9.4.

Рисунок 9.4

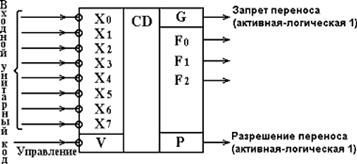

В цифровой электронике существует много ИМС, выполняющих функцию шифратора, например, К555ИВ1. Ниже показаны ее функциональное обозначение (рисунок 9.5) и таблица истинности (таблица 9.3)

Рисунок 9.5

Кодируемый сигнал низкого уровня (логический 0) поступает на один из входов X0...Х7. На остальных входах должны быть сигналы высокого уровня (таблица 9.3).

Микросхема имеет управляющий (стробированый) вход V и два дополнительных выхода: Р – разрешение переноса и G – запрет переноса. Активными сигналами на этих выходах являются логические единицы. Сигналы на входе V разрешают работу ИМС в режиме кодирования (V=0) или запрещают работу (V=1). В случае запрета (V=1) на всех выходах устанавливаются напряжения высокого уровня независимо от сигналов на входах. Сигнал запрета переноса (Р=0) появляется тогда, когда на всех информационных входах X0...Х7 будут сигналы высокого уровня (логические единицы). В этом случае появляется единица на выходе G.

Сигналы с выходов G и P используют для управления схемой, которая принимает сигналы с выходов шифратора.

Некоторые шифраторы основную функцию совмещают с возможностью введения приоритетов кодируемых сигналов. Микросхема К555ИВ1 (рисунок 9.5) обладает такой возможностью. Функция приоритета реализуется следующим образом. В ИМС допускается одновременное поступление активных сигналов (логических нулей) на несколько входов. Приоритетом обладает активный сигнал на входе с меньшим номером, и выходной двоичный код будет соответствовать этому выбранному сигналу. Например, при комбинациях входных сигналов 11110111, 00000111, 10100111, записанных в порядке принятом в таблице 9.3, результат будет один и тот же: на выходе будет сформирован код 011, поскольку приоритетом обладает нулевой сигнал на входе Х3.

Таблица 9.3

| X7 | X6 | X5 | X4 | X3 | X2 | X1 | X0 | F2 | F1 | F0 | G | P |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

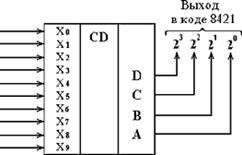

9.1.2.1.2 Шифраторы двоично-десятичного кода

Шифраторы двоично-десятичного кода преобразуют входной десятичный (унитарный) код в двоично-десятичный (BCD)-код (код 8421). С выхода такого шифратора параллельно снимается группа двоичных сигналов, из которых каждые четыре (тетрада) отображают в двоичном коде десятичную цифру. Отличие четырехразрядного двоичного кода от четырехразрядного BCD-кода заключается в диапазоне изменения комбинаций выходного кода: в первом случае выходной код изменяется от 0000 до 1111, а во втором – от 0000 до 1001.

В одном байте (восьми битах) можно упаковать (уложить) две десятичные цифры в BCD-коде. Такой формат представления десятичных чисел называется упакованным.

На рисунке 9.6 приведено функциональное обозначение шифратора BCD-кода.

На вход системы поступают двоичные цифры от 0 до 9, которые отображаются на выходе одной тетрадой двоичного кода, принимающей значения от 0000 В до 1001 В.

Рисунок 9.6

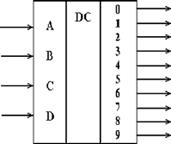

9.1.2.1.3 Дешифраторы двоичного кода

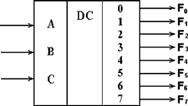

Дешифратором (декодером) двоичного кода называют КЦУ, преобразующее входной двоичный код в десятичный (унитарный). Полный дешифратор с m входами имеет 2m выходов. Каждой комбинации входных сигналов соответствует активное значение только одного определенного выходного сигнала. Ниже показана таблица истинности (таблица 9.4) и условное обозначение (рисунок 9.7) трехвходового полного дешифратора с единичными активными значениями выходных сигналов F0...F7.

Рисунок 9.7

Дешифратор реализует восемь различных логических функций:

Таблица 9.4

| № набора | C | B | A | F0 | F1 | F2 | F3 | F4 | F5 | F6 | F7 |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 2 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 3 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 4 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 5 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 6 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 7 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

Если входные переменные рассматривать как двоичную запись чисел, то логическая единица формируется на том выходе, номер которого соответствует десятичному эквиваленту входного двоичного числа.

Рассмотренный дешифратор (таблица 9.4) является преобразователем двоичного кода в унитарный (десятичный).

Приведенные булевы выражения функций F0...F7 можно реализовать на логических элементах в базисах И, ИЛИ, НЕ; И-НЕ или ИЛИ-НЕ, пользуясь методикой изложенной ранее.

В интегральном исполнении выпускаются различные структуры дешифраторов, в которых имеются 2, 3 или 4 входа. В одном корпусе может быть несколько дешифраторов.

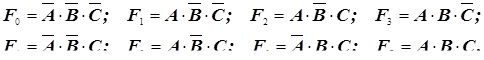

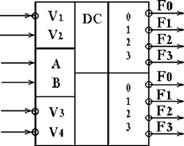

Для увеличения функциональных возможностей устройств часто предусматривается использование нескольких дополнительных сигналов управления. В качестве примера на рисунке 9.8 дано изображение микросхемы К555ИД4, содержащей сдвоенный двухвходовый дешифратор с активными нулевыми выходными сигналами.

Рисунок 9.8

Выходные сигналы обоих дешифраторов зависят от комбинации входных сигналов А, В. Синхронизация процесса формирования выходных сигналов F0...F3 для каждого дешифратора задается комбинациями управляющих сигналов V. Работу верхнего дешифратора разрешает комбинация V1=0, V2=1, а работу нижнего- V3=0, V4=0. Введение такого управления расширяет возможности микросхемы при построении более сложных устройств, например, дешифраторов с увеличенным числом входов и выходов.

На рисунке 9.9 показан пример включения двух микросхем К555ИД4 для реализации дешифратора четырехразрядного входного двоичного кода в выходной шестнадцатипозиционный унитарный (десятичный) код. Работу этого дешифратора поясняют таблицы 9.4.1 и 9.4.2.

Рисунок 9.9

Таблица 9.4.1

| X3 | X2 | Рабочий дешифратор |

| 0 | 0 | Нижний ИМС DD1 |

| 0 | 1 | Верхний ИМС DD1 |

| 1 | 0 | Нижний ИМС DD2 |

| 1 | 1 | Верхний ИМС DD2 |

Таблица 9.4.2

| № набора | X3 | X2 | X1 | X0 | F0 | F1 | F2 | F3 | F4 | F5 | F6 | F7 | F8 | F9 | F10 | F11 | F12 | F13 | F14 | F15 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 2 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 3 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 4 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 5 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 6 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 7 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 8 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 10 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 11 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 12 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 13 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 14 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 15 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

Дешифраторы могут быть неполными (имеющими число выходов N вых<2m, где m – число входных переменных). Например, такие дешифраторы могут использоваться для преобразования двоично-десятичного кода в код, предназначенный для управления десятичным индикатором (дешифраторы 4х10). На рисунке 9.10 показано условное обозначение дешифратора 4х10 (например, микросхемы К555ИД1 или К564ИД1). Схема имеет активные единичные выходные сигналы.

Рисунок 9.10

9.1.2.1.4 Дешифратор BCD-кода в семисегментный код

Подобное название имеет преобразователь двоично-десятичного (BCD) кода в код семисегментного индикатора десятичных цифр.

9.1.2.1.4.1 Семисегментные индикаторы на светодиодах

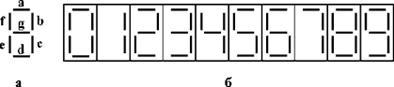

Очень распространенным выходным устройством отображения десятичных чисел является семисегментный индикатор. Семь сегментов индикатора обозначены буквами от а до g (рисунок 9.11, а).

Рисунок 9.11

Способ изображения десятичных цифр от 0 до 9 показан на рисунке 9.11,б. Например, если светятся сегменты a, b и c, то на индикаторе появляется десятичная цифра 7. Если светятся все сегменты от a до g, то появляется цифра 8. Существует несколько разновидностей индикаторов: на жидких кристаллах (ЖКИ), накальные (подобен обычным лампам накаливания), светодиодные и т.д.

Основной частью светодиода [18] является диод с плоскостным p-n - переходом. Когда диод включен в прямом направлении, через p-n - переход протекает ток и возникает излучение, которое фокусируется в индикаторе специальной линзой, чтобы его можно было наблюдать в виде загорания определенного сегмента.

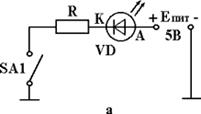

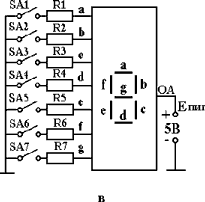

Схема включения одного светодиода (сегмента) приведена на рисунке 9.12,а.

Рисунок 9.12

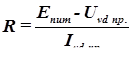

.(9.4.1)

.(9.4.1)

Когда ключ SA1 замкнут, ток от источника Епит=+5В течет через светодиод, вызывая его свечение. Последовательно включенный резистор ограничивает ток до уровня примерно (10…20) мА. Без ограничивающего резистора светодиод может выйти из строя. Обычно на выводах светодиодов при излучении допускается напряжение (UVD.пр) не более (1,7…2) В. Как и всякий диод, светодиод чувствителен к полярности приложенного напряжения. Чтобы он был включен в прямом направлении катод (К) должен быть подключен к отрицательному полюсу источника питания (земле), а анод (А) – к его положительному полюсу.

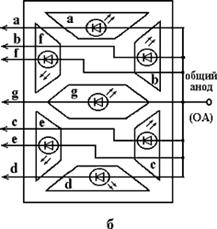

Устройство семисегментного индикатора на светодиодах показано на рисунке 9.12, б. В каждом сегменте (от а до g) содержится светодиод и фокусирующая линза. Аноды всех светодиодов соединены вместе и подключены с правой стороны индикатора к одному выводу - общему аноду (ОА). Катоды каждого светодиода связаны с внешними выводами, обозначенными a, b, c, ... g. Индикатор (рисунок 9.12, б) относится к семисегментным светодиодным индикаторам с общим анодом. Существуют индикаторы с общим катодом [15].

На рисунке 9.12, в показано управление сегментами индикатора с помощью механических переключателей. При замыкании одного из ключей SA1...SA7 ток от Епит=+5В течет: через выбранный сегмент, ограничительный резистор и замкнутые контакты переключателя – на землю (-Епит). При этом выбранный сегмент будет светиться (излучать). Если, например, мы захотим высветить на индикаторе десятичную цифру 7, то необходимо замкнуть ключи SA1, SA2 и SA3, чтобы излучали сегменты а, b и с. Если хотим высветить цифру 5, необходимо замкнуть ключи SA1, SA3, SA4, SA6 и SA7, которые заземляют катоды сегментов a, c, d, f и g. Следует обратить внимание, что в светодиодном индикаторе с общим анодом для активизации (зажигания) сегментов необходимо подать потенциал земли (логический нуль) на вывод, соответствующий выбранному сегменту.

Для управления работой индикатора на рисунке 9.12, в использовались механические переключатели. Обычно управляющие сигналы формируются интегральными микросхемами, например, дешифратором BCD-кода в семисегментный код.

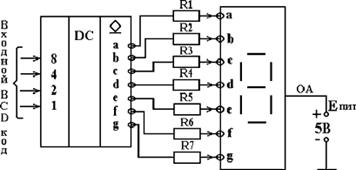

Ниже показано изображение такого дешифратора на электрических схемах (рисунок 9.13,а) и его подключение к семисегментному светодиодному индикатору с общим анодом (рисунок 9.13,б).

А Б

Рисунок 9.13

В качестве дешифраторов BCD-кода в семисегментный могут использоваться различные микросхемы, приведенные в [4, 15].

Например, ИМС К514ИД2, обозначение которой дано на рисунке 9.13,а, имеет открытые коллекторные выходы и используется совместно с индикаторами, имеющими общий анод. При этом требуется применение внешних резисторов, включаемых между выходами дешифратора и входами индикатора (см. рисунок 9.13,б). Допустимый ток микросхемы дешифратора по каждому выходу составляет 22 мА.

Помимо информационных входов, на которые поступает двоично-десятичный код, индикаторы могут содержать ряд управляющих входов [4, 15, 18], например, для подавления нулей, гашения, контроля свечения, синхронизации и т.д.

9.1.2.2 Мультиплексоры и демультиплексоры

В современных микропроцессорных устройствах управления и однокристальных микроЭВМ широко применяются КЦУ, осуществляющие подключение (коммутирование) выхода одного из параллельно включенных цифровых устройств на общую шину или, наоборот, соединение общей шины с входом одного из нескольких параллельно включенных устройств. Эти функции выполняют устройства, называемые мультиплексорами и демультиплексорами.

9.1.2.2.1 Мультиплексоры

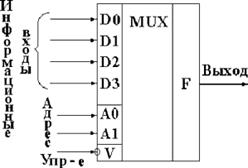

Мультиплексор – это комбинационное цифровое устройство, которое соединяет (коммутирует) один из нескольких информационных входных сигналов с одним общим выходом. Пример обозначения мультиплексора на электрических схемах показан на рисунке 9.14, а.

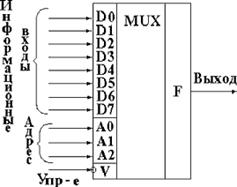

Устройство содержит восемь информационных входов: D0, D1, ..., D7; три адресных входа: А0, А1, А2 и один синхронизирующий (управляющий) вход V.

Рисунок 9.14 а

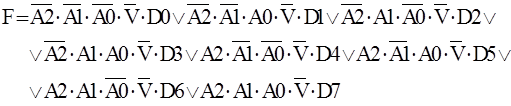

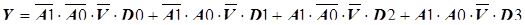

В зависимости от комбинации адресных сигналов А0, А1, А2 он обеспечивает коммутацию одного из восьми информационных входных сигналов Di на общий выход F. Нулевой синхросигнал на входе V разрешает передачу информации с выбранного входа на выход. Булево выражение, описывающее функционирование рассматриваемого мультиплексора имеет вид

(9.5)

(9.5)

Пример реализации мультиплексора 4x1.

Мультиплексор можно реализовать с помощью логических элементов заданного базиса. В его структуру можно ввести и более сложные цифровые устройства, например, преобразователь двоичного кода в десятичный (дешифратор).

На рисунке 9.14, б приведен пример реализации мультиплексора с четырьмя информационными входами на ЛЭ базиса И, ИЛИ, НЕ и дешифраторе, а на рисунке 9.14, в показано его функциональное обозначение. Если V=0, то F = 0 независимо от информационных сигналов.

Б

В

Рисунок 9.14

Схема реализует булево выражение

. (9.6)

. (9.6)

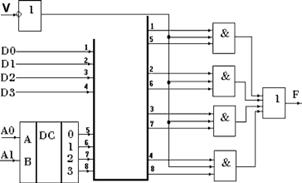

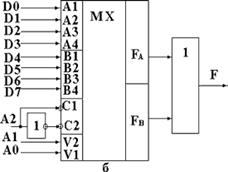

Существуют мультиплексоры в интегральном исполнении, например, ИМС К555КП2 (рисунок 9.15).

Рисунок 9.15

Мультиплексор КП2 (рисунок 9.15,а) содержит два мультиплексора 4x1 с общими адресными входами. Он состоит из двух частей, каждая из которых содержит четыре информационных канала А1 ... А4 (В1 ... В4); и один выход FА (FВ). Управляющие (адресные) входы V2, V1 являются общими, т.е. сигналы на них оказывают одновременное воздействие на обе части ИМС. Правила работы схемы отражает таблица 9.5.

Таблица 9.5

| Стробированые входы С1, С2 | Управляющие входы | Выход FA | Выход FB | |

| V 2 | V1 | |||

| 0 | 0 | 0 | A1 | B1 |

| 0 | 0 | 1 | A2 | B2 |

| 0 | 1 | 0 | A3 | B3 |

| 0 | 1 | 1 | A4 | B4 |

| 1 | X | X | 0 | 0 |

| Примечание: X – любое значение: 0 или 1 | ||||

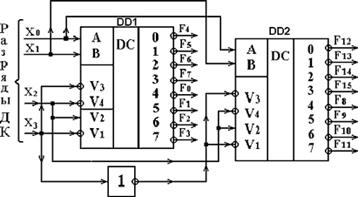

Для увеличения числа каналов объединяют несколько мультиплексоров, используя для этой цели стробированые входы, как это показано на рисунке 9.15, б. Эта схема реализует мультиплексор 8х1 (таблица 9.5.1).

Таблица 9.5.1

| № | А2 | А1 (V2) | А0 (V1) | F |

| 0 | 0 | 0 | 0 | D0 |

| 1 | 0 | 0 | 1 | D1 |

| 2 | 0 | 1 | 0 | D2 |

| 3 | 0 | 1 | 1 | D3 |

| 4 | 1 | 0 | 0 | D4 |

| 5 | 1 | 0 | 1 | D5 |

| 6 | 1 | 1 | 0 | D6 |

| 7 | 1 | 1 | 1 | D7 |

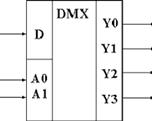

9.1.2.2.2 Демультиплексоры

Демультиплексор – это КЦУ, которое соединяет (коммутирует) общий информационный вход с одним из нескольких выходов в соответствии с заданным кодом на управляющих (адресных) входах. Иными словами, демультиплексоры решают задачи, обратные мультиплексированию. Пример обозначения демультиплексора на электрических схемах показан на рисунке 9.16, a.

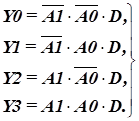

Схема имеет четыре информационных выхода и два адресных входа А0 и А1. Булевы выражения, описывающие работу данного демультиплексора, имеют вид:

(9.7)

(9.7)

Такими же выражениями определяется работа дешифратора с синхровходом V (рисунок 9.16, б). Поэтому его можно использовать в качестве демультиплексора, если информационный входной сигнал подавать на вход V.

А Б

Рисунок 9.16

9.1.2.2.3 Мультиплексоры–селекторы (мультиплексоры-демультиплексоры)

Мультиплексоры – селекторы являются двунаправленными, поскольку позволяют коммутировать цифровые и аналоговые сигналы в обоих направлениях, и поэтому могут быть использованы не только в качестве мультиплексора для коммутации одного из входов на выход, но и в качестве селектора (демультиплексора) для коммутации входа на один из выходов.

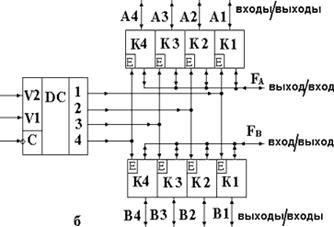

Ниже показаны: обозначение мультиплексора-селектора (демультиплексора) на электрических схемах (рисунок 9.17, а) и его упрощенная внутренняя структура (рисунок 9.17, б).

Рисунок 9.17

Устройство содержит две группы двунаправленных ключей (К1...К4) и дешифратор. Выходные сигналы дешифратора воздействуют на управляющие входы ключей (Е) и определяют их состояние. При Е=0 ключ закрыт, а при Е=1 – открыт и образует низкоомную цепь распространения сигнала через него. Такой ключ называют аналоговым, поскольку он обеспечивает неискаженную двухстороннюю передачу сигналов. Каждый ключ К имеет два равнозначных вывода, любой из которых может быть входом или выходом. По одному из выводов ключи объединены в две группы FА и FВ, которые образуют выходы мультиплексоров и входы демультиплексоров.

Структуру, представленную на рисунке 9.17, б, имеет микросхема К561(564)КП1, выполненная по КМОП-технологии и содержащая два мультиплексора - селектора, управляемые от общих входов V1, V2 и С (рисунок 9.17, а). При единичном управляющем сигнале на входе С ключи разомкнуты и выходы находятся в 3-м состоянии.

9.1.2.3 Сумматоры и полусумматоры

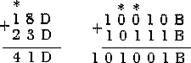

Сумматор предназначен для сложения двух чисел, заданных в двоичном коде. Из примера, приведенного на рисунке 9.18, видно, что правила сложения десятичных и двоичных чисел одинаковы:

1) сложение производится поразрядно от младшего разряда к старшему;

2) сумма младших разрядов слагаемых А0 и В0 записывается в соответствующей системе счисления однозначным числом S0 либо двухзначным числом P0S0, где Р0 называется переносом из нулевого разряда в соседний первый;

3) во всех последующих разрядах находится сумма данных разрядов слагаемых Ai, Bi и переноса Pi-1 от сложения предыдущих разрядов (в примерах на рисунке 9.18 этот случай помечен звездочкой).

Рисунок 9.18

Cказанное отражает таблица истинности одноразрядного двоичного полного сумматора (таблица 9.6).

Таблица 9.6

| N набора | Аi | Bi | Pi-1 | Si | Pi |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 |

| 2 | 0 | 1 | 0 | 1 | 0 |

| 3 | 0 | 1 | 1 | 0 | 1 |

| 4 | 1 | 0 | 0 | 1 | 0 |

| 5 | 1 | 0 | 1 | 0 | 1 |

| 6 | 1 | 1 | 0 | 0 | 1 |

| 7 | 1 | 1 | 1 | 1 | 1 |

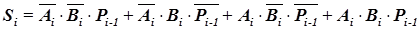

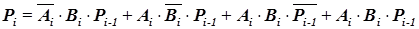

Булевы выражения логических функций Si и Pi в СДНФ имеют вид

,(9.8)

,(9.8)

.(9.9)

.(9.9)

Выражение (9.9) можно минимизировать. В результате получим

.(9.10)

.(9.10)

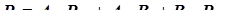

На основании выражений (9.8, 9.10) одноразрядный двоичный полный сумматор может быть реализован в базисе И, ИЛИ, НЕ (рисунок 9.19).

Рисунок 9.19

Используя правила перехода из базиса И, ИЛИ, НЕ в базис И-НЕ и ИЛИ-НЕ (5.1), можно построить одноразрядный полный сумматор в двух других базисах.

Обозначение одноразрядного сумматора на электрических схемах приведено на рисунке 9.20, в.

Полусумматор, в отличие от полного сумматора, обеспечивает выполнение операции суммирования двух одноразрядных двоичных чисел Ai и Bi без учета сигнала переноса. В результате сложения наряду с суммой может получиться перенос. Функционирование полусумматора описывается таблица 9.7.

Таблица 9.7

| N набора | Аi | Bi | Si | Pi |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 2 | 1 | 0 | 1 | 0 |

| 3 | 1 | 1 | 0 | 1 |

Дата добавления: 2019-02-12; просмотров: 347; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!