Архитектура процессора ADSP-2189M

Содержание

ВВЕДЕНИЕ..................................................................................................... 3

1 СТРУКТУРА И ЦЕЛИ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ............ 5

1.1 Форматы представления чисел....................................................... 10

1.2 Архитектура процессора ADSP-2189M......................................... 14

1.3 Организация циклического буфера................................................ 20

2 ВВОД-ВЫВОД ДАННЫХ ПО ПРЕРЫВАНИЯМ................................... 24

2.1 Встроенная и внешняя память......................................................... 29

2.2 Последовательный кодек AD73322................................................ 32

2.3 Последовательный интерфейс процессора..................................... 36

2.4 Обработка аналоговых сигналов процессором ADSP-2189M...... 38

ЗАКЛЮЧЕНИЕ............................................................................................. 41

ГЛОССАРИЙ................................................................................................ 42

СПИСОК ИСПОЛЬЗУЕМЫХ ИСТОЧНИКОВ........................................... 43

ПРИЛОЖЕНИЕ А ПРИМЕР СИСТЕМЫ НА БАЗЕ ADSP-2189M........... 45

ПРИЛОЖЕНИЕ Б Процессор ADSP-2189M.............................................. 46

ВВЕДЕНИЕ

Применение цифровых процессоров обработки сигналов (ЦПОС) в радиотехнических системах позволяет выполнять обработку поступающей информации в реальном времени. Это означает, что все операции алгоритма обработки сигнала должны выполняться за время, не превышающее период дискретизации входного сигнала.

Отличительной особенностью сигнальных процессоров является обработка больших массивов поточной цифровой информации с высокой производительностью. Выполнение этого требования достигается за счет высокой специализации сигнальных процессоров. Для них характерно разделение шин команд и шин данных (гарвардская архитектура), аппаратная поддержка программных циклов, наличие аппаратного умножителя, включение в систему команд операции умножения с накоплением МАС (С = A * B + C) с указанным в команде правилом изменения индекса элементов массивов.

|

|

|

Использование однотактного умножителя и ячеек памяти в качестве операндов обуславливает относительно низкие тактовые частоты работы этих процессоров. За счет быстрого выполнения команд межрегистрового обмена Ri→Rj не удается повысить производительность вычислений, как это делается в универсальных процессорах.

Малая разрядность (32 двоичных разряда и менее) сигнальных процессоров с фиксированной запятой может привести к неустойчивости рекурсивных фильтров. Более удобными для проектирования систем обработки являются микропроцессоры с плавающей запятой, так как они не требуют выполнения операций округления и нормализации данных, контроля переполнения суммы в программе. Ведущие компании выпускают как дешевые сигнальные процессоры с фиксированной запятой, так и более дорогие процессоры с плавающей запятой.

|

|

|

Примеры наиболее распространенных сигнальных процессоров: Motorola 56002,96002, Intel i960, Analog Devices 21xx,210xx, Texas Instruments TMS320Cxx.

Области применения

· Коммуникационное оборудование:

· Уплотнение каналов передачи данных;

· Кодирование аудио и видеопотоков;

· Системы гидро и радиолокации;

· Распознавание речи и изображений;

· Речевые и музыкальные синтезаторы;

· Анализаторы спектра;

· Управление технологическими процессами;

· Другие области, где необходима быстродействующая обработка сигналов, в том числе в реальном времени.

1 СТРУКТУРА И ЦЕЛИ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ

1 СТРУКТУРА И ЦЕЛИ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ

Структурная схема цифровой обработки аналогового сигнала Х(t) состоит из антиэлайсингового фильтра (АФ), аналого-цифрового преобразователя (АЦП), центрального процессора (ЦП), цифро-аналогового преобразователя (ЦАП) и сглаживающего фильтра (СФ) (рис. 1).

|

Рисунок 1. Схема цифровой обработки сигнала

В радиотехнических устройствах цифровая обработка обычно применяется в низкочастотных блоках. Сигналом X(t) может быть выходное напряжение микрофонного усилителя или выходное напряжение детектора (амплитудного, частотного, фазового). В настоящее время разработаны высокопроизводительные процессоры для обработки радиосигналов промежуточной частоты.

|

|

|

Отфильтрованный аналоговый сигнал Xф(t) преобразуется в пропорциональный двоичный m-разрядный код аналого-цифровым преобразователем. На выходе АЦП получается двоичное представление аналогового сигнала (рис. 2), которое затем обрабатывается арифметически цифровым сигнальным процессором (ЦП). Для 16-разрядного сигнального процессора ADSP 2189M разработаны микросхемы параллельных и последовательных АЦП и ЦАП соответствующей разрядности. В данном примере m=n=16. Количество ступеней квантования 16-разрядного АЦП равно 216-1= 65535. Типовые частоты квантования данного процессора составляют 8,16,32 и 64 кГц. Одно из указанных значений частоты задается в программе обработки данных при начальной инициализации процессора.

|

Рисунок 2. Квантование аналогового сигнала по времени и уровню.

Дискретные отсчеты аналогового сигнала хранятся в виде массива 16-разрядных двоичных чисел в специально отведенной области памяти – памяти данных (Data Memory), расположенной внутри микросхемы сигнального процессора. Объем памяти данных ADSP-2189M составляет 48К 16-разрядных слов. Максимальное количество дискретных отсчетов АЦП, хранящихся во внутренней оперативной памяти данных процессора, не может превышать 49 152 (48х1024) точек. При выполнении программы элементы массива можно циклически читать одной ассемблерной командой

|

|

|

MХ0 = DM (I0,M1),

где MX0 – регистр умножителя–накопителя, I0 и M1 – индексные регистры генератора адреса, которые хранят адрес ячейки памяти (I0) и – шаг изменения адреса (М1). Например, если перед первым выполнением команды DM в регистрах были записаны значения I0=5, М1=1, то после выполнения команды в регистр MХ0 процессор запишет 16-разрядное двоичное число пятой ячейки буфера данных (I0=5) и увеличит адрес на единицу (М1=1). При повторном проходе этой ветви программы выполнение команды MХ0 = DM (I0,M1) вызовет запись в регистр МХ0 шестого элемента буфера в памяти и т.д.

Основной особенностью сигнальных процессоров является обработка накопленного массива данных за время между соседними отсчетами TS. При стандартной частоте квантования FS = 8 кГц, принятой в телефонии, на обработку массива данных отводится время TS = 1/FS = 125 мкс.

Система, представленная на рис. 1, работает в реальном масштабе времени. В ней АЦП непрерывно дискретизирует сигнал с частотой, равной FS, и выдает новый отсчет процессору с такой же частотой. Для обеспечения работы в реальном масштабе времени процессор должен закончить все вычисления в пределах интервала дискретизации и передать выходной отсчет на ЦАП до поступления следующего отсчета с АЦП.

В сотовых радиотелефонах массив цифровых данных звукового сигнала накапливается в течение интервала времени 10-20 мс и на обработку отводится намного большее время, чем период дискретизации TS. Тем не менее, программа выполнятся также в темпе поступающей информации и должна закончиться до поступления нового блока данных.

Типичной функцией ЦП может быть реализация цифрового фильтра. В случае использования алгоритма быстрого преобразования Фурье (БПФ), блок данных загружается в оперативную память данных процессора. Пока работает алгоритм БПФ, тем временем новый блок данных загружается в память для обеспечения работы в реальном масштабе времени. Процессор должен вычислить преобразования Фурье в течение интервала передачи данных, чтобы быть готовым к процессу обработки следующего блока данных.

Обычно, прежде чем подвергнуться реальному аналого-цифровому преобразованию, аналоговый сигнал проходит через цепи нормализации, которые выполняют такие функции, как усиление, ослабление и фильтрацию. Для подавления нежелательных сигналов вне полосы пропускания и предотвращения наложения спектров (aliasing) необходим фильтр нижних частот или полосовой фильтр. Эту функцию выполняет аналоговый антиэлайсинговый фильтр (АФ). Блок АФ необходим в системе и в том случае, когда процессор выполняет программу цифровой фильтрации. На рис. 3 показаны графики АЧХ цифрового фильтра и аналогового антиэлайсингового фильтра нижних частот. Цифровой фильтр должен пропустить сигнал с частотами, расположенными в пределах полосы пропускания, т.е. от нуля до f=fН. Кроме необходимого участка в полосе от нуля до FS/2 график имеет и копию при частотах, превышающих половину частоты дискретизации. Задачей антиэлайсингового фильтра является устранение копии АЧХ проектируемого цифрового фильтра. Характеристика АФ рассчитывается так, чтобы не пропустить сигналы с частотами, большими половины частоты дискретизации.

Рисунок 3. Амплитудно-частотные характеристики фильтров

После обработки процессором содержащаяся в сигнале информация преобразуется обратно в аналоговую форму с использованием n-разрядного цифро-аналогового преобразователя (ЦАП). Сглаживающий фильтр необходим для преобразования дискретного сигнала в непрерывный. Показанный на рис. 1 цифро-аналоговый преобразователь может не использоваться, если обработанный процессором сигнал передается по радиоканалу в цифровой форме.

Главная цель цифровой обработки сигналов (ЦОС) заключается в получении содержащейся в них информации. Эта информация обычно присутствует в амплитуде сигнала (абсолютной или относительной), в частоте или в спектральном составе, в фазе или в относительных временных зависимостях нескольких сигналов. Как только желаемая информация будет извлечена из сигнала, она может быть использована различными способами.

В некоторых случаях желательно переформатировать информацию, содержащуюся в сигнале. В частности, смена формата имеет место при передаче звукового сигнала в телефонной системе с многоканальным доступом и частотным разделением (FDMA). В этом случае аналоговые методы используются, чтобы разместить несколько голосовых каналов в частотном спектре для передачи через радиорелейную станцию микроволнового диапазона, коаксиальный или оптоволоконный кабель. В случае цифровой связи аналоговая звуковая информация сначала преобразуется в цифровую с использованием АЦП. Цифровая информация, представляющая индивидуальные звуковые каналы, мультиплексируется во времени (многоканальный доступ с временным разделением, TDMA) и передается по последовательной цифровой линии связи .

Цифровая фильтрация является одним из наиболее мощных инструментальных средств ЦОС. Кроме очевидных преимуществ устранения ошибок в аналоговом фильтре, связанных с флуктуациями параметров компонентов во времени и по температуре, цифровые фильтры способны удовлетворять таким техническим требованиям по своим параметрам, которых, в лучшем случае, было бы чрезвычайно трудно или даже невозможно достичь в аналоговом исполнении. Кроме того, характеристики цифрового фильтра могут быть легко изменены программно. Поэтому они широко используются в телекоммуникациях, в приложениях адаптивной фильтрации, таких как подавление шума и распознавание речи, подавление эха в модемах. Современные высокопроизводительные модемы используют также методы цифровой обработки для выполнения таких функций, как модуляция, демодуляция, обнаружение и исправление ошибок, настройка параметров передачи.

Еще одна причина обработки сигналов заключается в сжатии полосы частот сигнала (без существенной потери информации) с последующим форматированием и передачей информации на пониженных скоростях, что позволяет сузить требуемую полосу пропускания канала. В высокоскоростных модемах и системах адаптивной импульсно-кодовой модуляции (ADPCM) широко используются алгоритмы устранения избыточности данных (сжатия), также как и в цифровых системах мобильной связи, системах записи звука MPEG, в телевидении высокой четкости (HDTV).

Форматы представления чисел

При разработке устройств, использующих сигнальные процессоры, необходимо учитывать конечную точность представления чисел в цифровых системах. Математический пакет MATLAB при синтезе проектируемого устройства позволяет анализировать эффекты, связанные с шумами квантования аналого-цифрового преобразования, учитывать переполнение разрядной сетки в процессе вычислений и искажения характеристик из-за квантования коэффициентов цифровых фильтров.

В процессорах семейства ADSP 21xx максимальная скорость вычислений достигается для чисел, представленных в формате с фиксированной запятой 1.15. Формат используется 16-разрядными процессорами и означает, что целая часть числа содержит только один разряд – знаковый. Дробная часть использует 15 разрядов (рис. 4). Числа, которые можно представить в данном

формате, по модулю не превосходят единицы.

Рисунок 4. Дробное число со знаком в формате 1.15

Двоичный код после запятой делится на постоянный коэффициент 215 = 32768. Ноль в знаковом разряде соответствует положительным числам, единица – отрицательным. Пятнадцать разрядов после запятой обеспечивают дискретность представления, равную единице в младшем разряде 2-15 = 1/32768 ≈ 3∙10-5. Из таблицы 1 видно, что максимальное положительное число в формате 1.15 равно 32767/32768 ≈ 0,9999695.

При проектировании цифровых устройств, использующих формат 1.х, необходимо масштабирование коэффициентов уравнений с той целью, чтобы привести их значения к диапазону [-1,1]. Для масштабирования все коэффициенты уравнения делятся на одну и ту же константу, затем на нее же умножается правая часть уравнения. В качестве масштабирующего множителя удобно выбирать степень двойки, поскольку умножение в этом случае сводится к поразрядному сдвигу двоичного числа влево. Рассмотрим пример масштабирования коэффициентов эллиптического фильтра нижних частот 4-го порядка с частотой среза, равной 20 % от частоты Найквиста, пульсациями в полосе пропускания 1 дБ и подавлением сигнала в полосе задерживания 60 дБ. Перечисленные параметры фильтра зададим в командной строке MATLAB с помощью функции ellip

>> [b, a] = ellip(4, 1, 60, 0.2)

b = 0.00590.0053 0.0096 0.0053 0.0059

a =1.0000-3.0477 3.8240 -2.2926 0.5523

Из полученного решения видно, что максимальный по модулю коэффициент больше единицы и равен 3,824. Уравнение рекурсивного фильтра

y(k) = 0,0059 x(k) + 0,0053 x(k - 1) + 0.0096 x(k - 2) + 0.0053 x(k - 3) + + 0.0059 x(k - 4) + 3.0477 y(k – 1) - 3.8240 y(k – 2) + 2.2926 y(k – 3) -

- 0.5523 y(k – 4).

Для масштабирования разделим и умножим правую часть уравнения на 4

y(k) = 4(0,0015 x(k) + 0,0013 x(k - 1) + 0,0024 x(k - 2) + 0,0013 x(k - 3) +

+ 0,0015 x(k - 4) + 0,7619 y(k – 1) – 0,9560 y(k – 2) + 0,5731 y(k – 3) -

- 0,1381 y(k – 4)).

Округление коэффициентов из-за конечной разрядности процессора может заметно сказаться на рекурсивных фильтрах с крутым спадом АЧХ между полосами пропускания и задерживания. Предположим, что фильтр реализован на 9-разрядном процессоре в формате 1.8. В этом случае коэффициенты округляются с точностью до 1/256, так как у них остаются 8 двоичных разрядов после запятой.

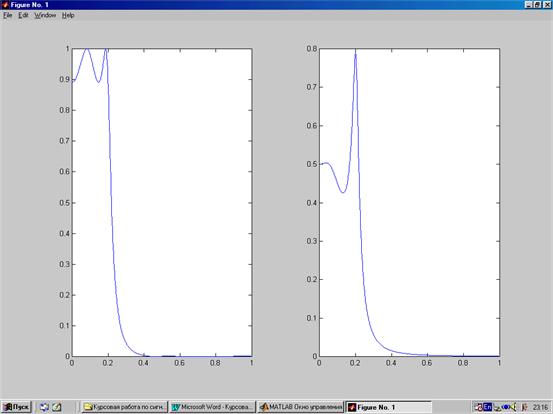

» bm=b/4; масштабирование коэффициентов числителя

» am=a/4; масштабирование коэффициентов знаменателя

» [h,f]=freqz(b,a); АЧХ до округления

» hm=freqz(bm,am);

» subplot(1,2,1)

» plot(f/pi,abs(h)) график АЧХ до округления

» bq=round(bm*256)/256; округление масштабированных

» aq=round(am*256)/256; кооэффициентов

» hq=freqz(bq,aq); АЧХ после округления

» subplot(1,2,2)

» plot(f/pi,abs(hq)) график АЧХ после округления

|

Рисунок 5 АЧХ рекурсивного ФНЧ до округления коэффициентов (слева) и после округления (справа) в формате 1.8

Из сравнения графиков на рис. 5 видно, что амплитудно-частотная характеристика фильтра изменилась существенно: в несколько раз увеличилась амплитуда пульсаций в полосе пропускания, скат АЧХ стал более пологим. Заданный параметр пульсаций в полосе пропускания 1 дБ фильтр с форматом 1.8 не обеспечивает. Округление коэффициентов в формате 1.15 приводит к небольшим искажениям частотной характеристики. В этом случае графики АЧХ без учета квантования и с квантованием практически сливаются.

В некоторых случаях удобно использовать для процессоров ADSP2189M целочисленный формат 16-разрядных двоичных чисел без знака или со знаком. Целые числа без знака имеют диапазон [0,65535], диапазон целых чисел со знаком составляет [-32768,32767]. Коэффициенты деления частоты генератора, задающие период квантования сигналов в АЦП и ЦАП, в рассматриваемой далее программе задаются в виде 16-разрядных целых чисел без знака. Программы на языке С поддерживают 16- и 32-разрядные переменные со знаком и без знака.

Архитектура процессора ADSP-2189M

Однокристальный процессор ADSP-2189M в 100 или 144-выводном корпусе использует модифицированную гарвардскую архитектуру, которая предполагает раздельные адресные пространства памяти программы и памяти данных, позволяет хранить данные в памяти программы (рис. 6). Процессор содержит ядро 2100 (три вычислительных блока, генераторы адреса и программный секвенсор), два последовательных порта, 16-разрядный внутренний порт прямого доступа DMA, 8-разрядный порт DMA, порты ввода-вывода внешних сигналов, программируемый таймер, систему обработки прерываний, встроенную статическую память программ и данных.

Все устройства микропроцессора – 16-разрядные и оперируют с данными в формате с фиксированной запятой. Числа представляются либо как беззнаковые, либо в дополнительном коде. 14-разрядная шина адреса памяти программ позволяет получить прямой доступ к 16К слов (24-битовых) памяти программ. Шина данных памяти данных является 16-разрядной. На кристалле процессора расположено 32К слов памяти программ и 48К слов (16-битовых) памяти данных.

Рисунок 6. Блок-схема ADSP-2189M

При тактовой частоте 75МГц производительность процессора составляет 75 миллионов команд в секунду (75 MIPS), время командного цикла – 13.3 нс.

За один цикл ADSP-2189M может сгенерировать адрес следующей команды программы, выбрать следующую команду, выполнить два обмена данных, обновить два указателя адреса, выполнить вычислительную операцию, передать или принять данные от двух последовательных портов и обновить регистр таймера. С точки зрения программиста сигнальный процессор представляет собор набор программно-доступных регистров (рис.7).

Адресные генераторы (DAG) вычисляют адреса при пересылке данных из памяти в регистры и обратно. Генератор DAG1 может выполнять адресацию только в памяти данных, DAG2 – в памяти данных и в памяти программ.

Секвенсор управляет ходом выполнения программы. Регистр команд секвенсора хранит информацию о выполняемой в данный момент времени команде.

РM – память программ (program memory), DM – память данных (data memory)

Команды загружаются из памяти программ в регистр команд в одном цикле процессора и выполняются в следующем цикле, когда одновременно с выполнением выбирается следующая команда программы. Регистр команд образует одноуровневый конвейер в потоке выполняемых команд. Секвенсор позволяет организовать цикл в программе без использования команд условного перехода. Условие завершения цикла процессор выполняет автоматически, контролируя системный счетчик циклов программы.

Устройство также способно с минимальной задержкой реагировать на прерывания, поступающие от контроллера прерываний. Появление прерывания вызывает временную остановку основной программы и переход к ячейке памяти, где хранится подпрограмма обработки прерывания. Для этих целей в таблице векторов прерываний зарезервировано четыре ячейки памяти на одно прерывание. Прерывания могут вызываться внешними сигналами, поступающими на процессор, или циклически через равные интервалы времени, подсчитываемые таймером.

Арифметико-логическое устройство (АЛУ) поддерживает 32-разрядные арифметические действия. АЛУ обеспечивает стандартный набор арифметических и логических функций: сложение, вычитание, инкремент, декремент, получение абсолютного значения, смену арифметического знака, логическое И, ИЛИ, исключающее ИЛИ и инверсию. Поддерживаются примитивы деления.

Умножитель-накопитель МАС выполняет умножение со сложением или умножение с вычитанием за один цикл. Пример такой ассемблерной команды рассмотрен ранее. Для защиты от переполнения устройство содержит 40-битный аккумулятор. Дополнительные 8 разрядов допускают возникновение 256 переполнений, прежде чем произойдет потеря данных. Если после окончания выполнения программы установлен флаг MV, то это означает, что регистр результата содержит слово, длина которого больше 32 разрядов.

Устройство сдвига производит операции логического и арифметического сдвига, нормализации (преобразование из формата с фиксированной запятой в формат с плавающей запятой), денормализации (преобразование из формата с плавающей запятой в формат с фиксированной запятой), вычисления экспоненты.

Два последовательных порта SPORT0 и SPORT1 используются для обмена данными с последовательными устройствами. Обычно один из портов подключается через СОМ-порт к компьютеру, другой – с последовательным кодеком (АЦП и ЦАП в одной микросхеме). Оба порта поддерживают обмен данными в последовательном коде словами длиной от 3 до 16 бит и обеспечивают логарифмическое сжатие данных по А-закону или μ-закону в соответствии с рекомендацией G.711.

Программируемый таймер генерирует периодические прерывания с помощью 16-битного счетчика TCOUNT. Содержимое счетчика уменьшается на единицу в каждом цикле процессора. Когда счетчик обнуляется, генерируется прерывание и в него записывается начальное значение из 16-разрядного регистра TPERIOD.

Микропроцессор содержит внутренний порт прямого доступа к памяти (ПДП) и байтовый порт ПДП, которые обеспечивают быстрый обмен с памятью. Внутренний порт ПДП поддерживает обмен с памятью программ, байтовый порт позволяет записывать и читать как команды, так и данные. Порт интерфейса с хост-процессором обеспечивает подключение процессоров данного семейства или других микропроцессоров без дополнительных интерфейсных схем.

Напряжение питания ядра процессора 2.5В, напряжение на внешних выводах портов ввода-вывода должно быть равным 2.5В или 3.3В. Мощность, потребляемая от источника питания, достигает максимума 90мВТ при выполнении процессором программы из встроенной памяти и не превышает 1 мВТ в режиме пониженного энергопотребления.

Переход в «спящий» режим может осуществляться аппаратно или программно.

Структура процессора ориентирована на выполнение наиболее часто встречающихся операций при цифровой обработке за один цикл. Типовой операцией различных алгоритмов ЦПОС является суммирование произведений. Для этого процессору необходимо извлечь из памяти два операнда (например, коэффициент фильтра и один отсчет массива данных), перемножить их и суммировать результат с предыдущим произведением.

При обращении к отдельному устройству в программах на языке ассемблера используется одна или несколько переменных, хранящихся в регистрах

процессора. Имя регистра определяет не только конкретное устройство, но и закрепленную за ним функцию. В генераторах адреса DAG1 и DAG2 четыре индексных регистра I содержат адреса ячеек памяти, регистры М – шаг увеличения адреса, L – длину циклического буфера.

Данные, поступающие на входы АЛУ и МАС для выполнения арифметических или логических операций, должны храниться в одном или нескольких регистрах АХ0, АХ1, МХ0, МХ1, АY0, АY1, МY0, МY1. Результат выполненной операции хранится в регистрах AR, AF, MR, MF. Признаки результата операции, выполненной АЛУ и МАС, процессор автоматически заносит в регистр ASTAT (рис. 8). Процессор установит бит AZ (AZ=1), если результат нулевой, и сбросит бит (AZ=0) в противном случае. Бит AN=1, если после выполнения текущей команды получено отрицательное число. Бит MV устанавливается в том случае, если произошло переполнение 40-разрядного числа МАС.

Таблица 2. Переменные регистра ASTAT

Регистр режима работы MSTAT содержит 4 бита управления переключением регистров вычислительных блоков, бит-реверсивной адресацией генератора DAG1 и насыщением АЛУ. Остальные 3 бита управляют размещением результата в блоке МАС, таймером и запуском процессора.

Стек счетчика COUNT содержит переменную CNTR для организации цикла без указания в программе условия его завершения. Необходимо лишь задать начальное значение счетчика CNTR, например, CNTR=10. Каждый цикл программы автоматически уменьшает содержимое счетчика на единицу. После 10 циклов, когда счетчик обнулится, процессор продолжит линейное выполнение программы.

В систему команд процессора входят многофункциональные команды, использующие параллельное выполнение действий различными блоками. Примером такого типа команд является следующая инструкция, которая выполняется за один цикл

MR=MR+MX0*MY0(SS), MX0=DM(I0,M0), MY0=PM(I4,M5);

Первая часть команды (до первой запятой) помещает в регистр результата.

MR блока МАС сумму предыдущего значения регистра и произведение текущих значений входных регистров Х и Y (МХ0 и МY0), данные в которых воспринимаются процессором как числа со знаком SS, где S – первая буква слова sign (знак). Во второй и третьей части команды процессор читает из памяти два новых операнда и запоминает их в регистрах МХ0 и МY0. В регистр МХ0 заносится значение из ячейки памяти данных (DM) с номером I0, в регистр МY0 – из ячейки памяти программ (РМ) с номером I4. После записи чисел в регистры значение переменной I0 увеличивается на М0, а I4 соответственно – на М5.

Дата добавления: 2018-08-06; просмотров: 688; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!