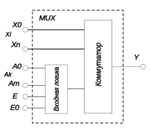

Обобщённая схема мультиплексора

Обобщённая схема мультиплексора.

Входные логические сигналы Xi поступают на входы внутреннего коммутатора и через коммутатор передаются на выход Y. На вход управляющей схемы подаётся слово адресных сигналов Ak (от англ. Address). Мультиплексор также может иметь дополнительный управляющий вход E (от англ. Enable), который разрешает или запрещает прохождение входного сигнала на выход Y. В разных типах мультиплексоров при запрещенном состоянии передачи по входу E на выходе Y может быть состояние 0 или 1. Кроме этого, некоторые мультиплексоры могут иметь выход с тремя состояниями: два логических состояния 0 и 1, и третье состояние — отключённый выход (высокоимпедансное состояние, часто говорят, Z-состояние — выходное сопротивление велико, выходной внутренний вентиль отключается от выхода специальным внутренним ключом). Перевод мультиплексора в третье состояние производится подачей на вход OE (от англ. OutputEnable) логической 1, чаще, логического 0 — опять же зависит от модели конкретного мультиплексора.

Реализация логических функций с помощью мультиплексора

На основе мультиплексоров может быть реализована любая логическая функция, благодаря чему встроенные в микросхему мультиплексоры широко применяются в СБИС программируемой логики.Покажем, как на основе мультиплексора можно реализовать логическую функцию "сумма по модулю 2", представленную таблицей истинности, приведенной в табл. 3.7. Таблица 3.7

|

|

|

| Номера набора | Х1 | Х0 | F |

| 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 2 | 1 | 0 | 1 |

| 3 | 1 | 1 | 0 |

Так как мультиплексор может пропустить на выход сигнал с любого входа, адрес которого установлен на соответствующих адресных входах, подадим на входы 0–3 сигналы "0" и "1" в соответствии с F. Номер входа при этом будет соответствовать номеру набора (рис. 3.18). Теперь если на адресные входы мультиплексора а1а0 подавать аргументы функции х1х0, значения функции F будут формироваться на выходе мультиплексора в соответствии с таблицей истинности.

Рис. 3.18. Реализация функции "сумма по модулю два"

Таким образом, чтобы мультиплексор выполнял логическую функцию, на его информационные входы необходимо подать логические "1" или "0" в соответствии с таблицей истинности, а на адресные входы – аргументы функции.

Рисунок 3.19 иллюстрирует возможность воспроизведения с помощью мультиплексора любой функции п аргументов. Действительно, каждому набору аргументов соответствует передача на выход одного из сигналов настройки. Если этот сигнал есть значение функции на данном наборе аргументов, то задача решена. Разным функциям будут соответствовать разные коды настройки. Информационные входы становятся входами настройки булевой функции, а адресные – входами аргументов.

|

|

|

Рис. 3.19. Реализация любой логической функции п аргументов

В примере с реализацией функции "сумма по модулю 2" используется мультиплексор с двумя адресными входами, число которых равно числу аргументов функции. Однако возможны ситуации, когда с помощью такого мультиплексора можно реализовать и более сложные функции.

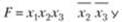

Пусть, например, булева функция трех аргументов имеет вид:

Аргумент х1, входит в функцию только один раз (в конъюнкцию х1х2х3), в то время как х2 и х3 – два раза. Это значит, что если х2 и х3 равны единице, то значение функции F однозначно определяется значением x1. Это дает возможность перехода к сокращенной таблице истинности функции F, которая в этом случае называется остаточной (табл. 3.8).

Таблица 3.8

| Х3 | Х2 | Fост |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | Х1 |

|

|

|

Таким образом, на входы настройки F(0), F(l), F(2) мультиплексора, соответствующие наборам х3х2 = 00, 01 и 10, подаются логические "1" или "0" в соответствии с Fост. На вход F(3) подается аргумент х1. Схема включения мультиплексора, реализующего функцию F, изображена на рис. 3.20. Переменная x1 в этом случае переводится из аргументов на входы настройки.

Рис. 3.20. Реализация функции трех аргументов на мультиплексоре с двумя адресными входами

Если использовать дополнительные элементарные логические схемы, то на основе мультиплексора можно реализовать функции более чем трех аргументов. При этом два аргумента будут подаваться на адресные входы, а остальные два – на входы настройки после соответствующей логической обработки.

Пример 3.2. Пусть на основе мультиплексора с двумя адресными входами необходимо реализовать функцию

Решение. Данная функция равна единице, когда х2х1 = 11 или х4х3 = 01. Если на адресные входы подать аргументы x1 и х2, то на вход настройки F(3), соответствующий набору х2x1 = 11, в соответствии с таблицей истинности Focr необходимо подать единицу (табл. 3.9).

Таблица 3.9

| Х2 | Х1 | Fост |

| 0 | 0 |

|

| 0 | 1 |

|

| 1 | 0 |

|

| 1 | 1 | 1 |

Для всех остальных сочетаний x1 и х2 результат конъюнкции x1x2 равен нулю и функция F будет однозначно определяться конъюнкцией  . Поэтому на остальные входы настройки нужно подать этот сигнал, сформированный с помощью логических схем.

. Поэтому на остальные входы настройки нужно подать этот сигнал, сформированный с помощью логических схем.

|

|

|

Если же в качестве адресных взять аргументы х3 и х4, то единицу нужно будет подавать на вход настройки F( 1), соответствующий набору х4х3 = 01 (табл. 3.10). На все остальные входы настройки нужно будет подавать результат конъюнкции x1x2 (рис. 3.21).

Таблица 3.10

| Х4 | Х3 | Fост |

| 0 | 0 | Х1Х2 |

| 0 | 1 | 1 |

| 1 | 0 | Х1Х2 |

| 1 | 1 | Х1Х2 |

Рис. 3.21. Реализация заданной функции F

Однако для реализации конъюнкции х1х2 нужна всего одна схема И на два входа, в то время как для конъюнкции  требуется еще один инвертор. Поэтому в качестве адресных выбираем аргументы х1 и х2.

требуется еще один инвертор. Поэтому в качестве адресных выбираем аргументы х1 и х2.

Еще более сложные логические функции можно реализовать на основе нескольких мультиплексоров. Именно они являются основой для выполнения логических функций в СБИС программируемой логики. Наборы мультиплексоров и вспомогательных логических схем в таких СБИС объединяются в универсальные логические блоки.

Дата добавления: 2018-08-06; просмотров: 1212; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!