Приведите современные виды ПЛИС и их характеристики

Виды современных ПЛИС

1.CPLD – complex PLD, основано на блоках макроячеек. Информация о конфигурации данной микросхемы хранится во внутренней энергонезависимой памяти (ROM, EEPROM, flash)

Преимущества:

1.Не требуется дополнительной микросхемы памяти

2.Высокая защищённость проекта (данные микросхемы обладают возможностью запрета чтения информации из конфигурационного ПЗУ, что не даёт злоумышленнику кражи топологии (конфигурации) микросхем)

Недостатки:

1.Необходимость реализации ПЗУ на ПЛИС (дорого, низкотехнологично)

2.Небольшой объём реализуемых функций (32-7000 макроячеек), по сравнению с FPGA – намного меньше например.

2. FPGA – field-programmable gate array (Программируемая пользователем вентильная матрица)

Информация о конфигурации микросхемы FPGA хранится во внутренней энергозависимой памяти, реализованной как статическое ОЗУ. Каждый раз, при перезагрузке микросхемы во внутреннее конфигурационное ОЗУ, информация загружается из внешнего конфигурационного ПЗУ (CROM).

Преимущества:

1.Высокая сложность микросхемы, которая позволяет реализовывать широкий спектр функций

2.Возможность изменения функциональности микросхемы даже в процессе работы (однако, перезагрузка требуется). Можно изменить информацию в конфигурационном ПЗУ, перезагрузить систему и начать работать в системе с новыми конфигурациями.

Недостатки: 1.Дорогая

|

|

|

2.Необходимость внешней микросхемы памяти (зачастую стоимость CROM соизмерима, если не выше, со стоимостью ПЛИС) – падает надёжность.

3.Слабая защищённость проекта заключается в том, что злоумышленник может снять информацию в точке между CROM и FPGA, и на основании снятой информации, получить конфигурацию ПЛИС. Для минимизации этого недостатка используют различные методы, например: Кроме применения в научной области и универсальных ЭВМ, СуперЭВМ, микросхемы FPGA используются в процессе прототипирования, т.е. в дальнейшем они могут быть созданы на микросхемах с жёсткой логикой функционировании.

ASIC (Application-specific integrated circuit) – интегральная схема, специфицируемая под специфику предметной области. Разрабатывается аналогично другим микросхемам ПЛИС, однако, изготавливается вплоть до фиксированных внутренних подключений на заводе-изготовителе интегральных схем. Полузаказная микросхема.

Завод имеет определённую структуру микросхем ASIC, список подключений которой ему передаёт пользователь, и завод изготавливает интегральную схему с жёсткой логикой функционирования.

Но недостатки ASIC – невозможность изменения и высокая стоимость, которая потом компенсируется при массовом выпуске микросхем.

|

|

|

Приведите примеры современных телекоммуникационных устройств, где используются ПЛИС

В области телекоммуникации ПЛИС используются в передатчиках и приемниках.

Например, рассмотрим SDR-приемник.

SDR-приемник - это методика приёма радиосигнала, в которой большой объем обработки информации производится в цифровом виде. Благодаря использованию ПЛИС и высокоскоростного АЦП, можно сделать приёмник, в котором даже перенос частоты «вниз» производится цифровым способом. Такой метод называется DDC (Digital Down Conversion). Используя эту методику, можно сильно упростить приёмник, в котором единственной аналоговой частью становится АЦП. Основой приемника является ПЛИС. Главная задача ПЛИС — «захватить» цифровой сигнал с АЦП, перенести его в область низких частот, отфильтровать и отправить результат на компьютер.

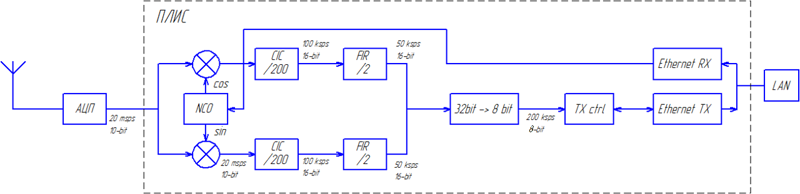

Структурная схема приемника

Вся дальнейшая обработка сигнала после АЦП идет в ПЛИС.

Поток данных с АЦП составляет 200 Мбит (10-bit x 20 MSPS). Передать такой поток напрямую в компьютер, а потом его еще и обработать очень сложно, поэтому частоту сигнала нужно специально понизить. При переносе на более низкую частоту возникает явление «зеркального канала», для борьбы с которым используют квадратурное преобразование частоты — сигнал преобразовывают в комплексную форму (происходит разделение на два канала I/Q). Перенос на более низкую частоту производится путем умножения исходного сигнала на сигнал генератора. Для того, чтобы переносить входной сигнал на нужную частоту, ее нужно создать. Для этого используется готовый компонент Quartus — NCO (numerically controlled oscillator). На генератор подается тактовая частота, такая же как и у АЦП (20 МГц), на его вход управления подается значение, определяющее частоту, и на его выходе формируется цифровой синусоидальный сигнал нужной частоты, дискретизованный с частотой 20 МГц. NCO способен параллельно формировать и косинусный сигнал, благодаря чему можно формировать квадратурный сигнал.

|

|

|

CIC-фильтр. После смешивания с сигналом генератора с выхода умножителей сигнал выходит уже перенесенный на более низкую частоту, но все еще с высокой частотой дискретизации (20 MSPS). Сигнал требуется децимировать, то есть отбросить часть выборок. Просто так отбросить лишние выборки нельзя, так как это приведет к искажению выходного сигнала. Поэтому сигнал нужно пропустить через специальный фильтр (CIC-фильтр). В данном случае я хотел получить на выходе приёмника частоту дискретизации сигнала 50 кГц. Из этого следует, что частота должна быть понижена в (20e6 / 50e3 = 400) раз. Децимацию придется производить в 2 этапа — сначала в 200, затем в 2 раза.

Первый этап выполняет именно CIC-фильтр. К сожалению, CIC-фильтр имеет довольно крутую АЧХ, стремящуюся к 0 при приближении к выходной частоте дискретизации (100 кГц). Для компенсации ее кривизны служит следующий фильтр.

|

|

|

Компенсационный FIR-фильтр. Этот фильтр нужен для того, чтобы компенсировать спад АЧХ CIC-фильтра и выполнить еще один этап децимации (в два раза). В данном случае частота дискретизации на выходе фильтра без децимации, как и на его входе, составляет 100 кГц. В результате этого частота среза будет как раз 25 кГц, что и видно на графиках выше.

Оба фильтра являются готовыми компонентами Quartus.

Передача данных на компьютер. Полученный поток данных ((16+16)bit x 50 KSPS = 1.6 Mbit) нужно передать на компьютер. Данные можно передавать через Ethernet. После переделки модуль Ethernet передатчика мог передавать 1024 байта, считывая их из RAM. В результате на компьютер в одном пакете отправляются 256 пар 16-битных значений сигнала, взятого с выходов фильтров. Так как данные поступают от АЦП непрерывно, а отправлять их на компьютер нужно пакетами, то пришлось реализовать двойную буферизацию памяти.

Дата добавления: 2018-06-01; просмотров: 921; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!