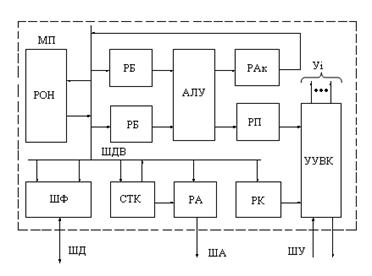

Микропроцессор. Обобщенная структурная схема.

Основой ее является общая внутренняя шина данных (ШДВ), соединяющая все элементы операционного блока (на схеме расположены выше ШДВ) и элементы управляющего блока (расположены ниже ШДВ). Шинный формирователь (ШФ), связывающий внутреннюю шину данных с внешней (ШД), является общим элементом как для операционного, так и для управляющего блоков (рис. ).

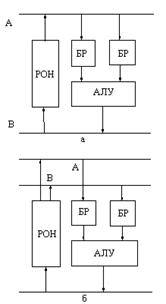

Структура микропроцессора с одной внутренней шиной данных не является единственно возможной. На рисунке представлены схемы двухшинной (рис. а) и трехшинной (рис. б) организации операционного блока.

Рис. – двухшинная (а) и трехшинная (б) организация операционного блока.

Увеличение числа внутренних шин данных позволяет совмещать во времени операции пересылки данных из одного операционного элемента в другой и ведет к росту быстродействия МП. В то же время увеличение числа шин уменьшает площадь кристалла, которую можно занять под различные функциональные элементы, и тем самым (при фиксированной площади) приводит к уменьшению функциональных возможностей МП. Поэтому промышленность выпускает микропроцессоры, в которых в зависимости от назначения по-разному организованы внутренние шины данных.

На характеристики МП большое влияние оказывают число и организация не только внутренних, но и внешних шин. В связи с ограниченностью числа выводов БИС в некоторых МП применяют общие шины адреса и данных (рис. а)

|

|

|

Рис. – МП с общими шинами адреса и данных.

В таких системах обмен информацией с внешними устройствами ввода-вывода (УВВ) или запоминающими устройствами (ОЗУ, ПЗУ) требует большего времени (до 8-ми тактов). Кроме того, необходим специальный внешний регистр для запоминания адреса, так как после 1-го такта шину надо освободить для передачи данных. Поэтому большее распространение получили МП с раздельными внешними шинами данных и адреса. (рис 6.10 и б)

В этих МП шина адреса однонаправлена, по ней адресные сигналы только передаются к внешним устройствам. Шина данных двух направленная, информация по ней и передается от МП к внешним устройствам (ОЗУ, УУВ на рис. б), и принимается от них (ОЗУ, ПЗУ, УВВ).

Внешняя шина управления ШУ во всех микропроцессорах самостоятельна. Эта шина многоразрядная, и каждая линия в ней однонаправлена, т.е. служит только для передачи или только для приема управляющих сигналов. В состав этой шины входят лини передачи сигналов записи (ЗП) в память и УВВ, а также сигналов чтения (ЧТ) из памяти и УВВ. Эти сигналы организуют соответствующий режим работы того устройства, адрес которого выставлен в этот момент на шине ША.

|

|

|

Сигналы ЗП и Чт организуют обмен данными между МП и внешними устройствами по инициативе МП. Внешние устройства обращаются к МП по своей инициативе. Например при обращении пользователя к МП через клавишный пульт ввода информации. Внешнее УВВ (пульт) выставляет запрос на прерывание (ЗПР) текущей программы и обслуживания микропроцессором внешнего устройства ( рис. б). Если внешних устройств, которые могут выставить сигналы ЗПР больше, чем входов запросов на прерывание у МП, то необходима дополнительная БИС- контроллер прерываний, которая устанавливала бы очередность этих сигналов и пропускала их на вход МП по заданному приоритету.

Обработка запросов на прерывание в МП велеться схемой прерываний (СП), входящей в состав УУВК. Этот узел (СП) должен выполнить следующие действия :

а) выбрать момент когда можно прервать основную программу и выставить на линии управления сигнал, подтверждающий разрешение на прерывание (РПР).

б) дать команду на запись в РОН состояние счетчика команд и регистра признаков в момент прерывания ;

в) запустить выполнения команды обслуживания УВВ;

г) после окончания обслуживания УВВ вернуть исходную информацию в СТК и РП и запустить продолжения выполнения основной программы с прерванного места.

|

|

|

Помимо основных управляющих сигналов в различных микропроцессорах применяются другие сигналы, облегчающие организацию наиболее трудоемких для программирования операций взаимодействия со внешними устройствами. Общее число линий управления может составлять 10…30.

Вопрос 13

Программно-доступные элементы МП КР580ИК80А.

Рисунок- Программная модель МП КР580ИК80А.

Этот МП построен по схеме с одной 8-разрядной внутренней шиной данных. В основном его структура подобна структуре МП, изображенной на рисунке. Однако иметься и отличия. К АЛУ подключена схема десятичной коррекции (СДК), позволяющая выполнять обработку данных, представленных, не только в двоичном, но и в двоично-десятичном коде, на базе МП КР580 (рис. ) содержит непосредственно микропроцессор (МП), память М (ROM и RAM) и порты ввода-вывода I/O (input/output), объединенные тремя шинами : данных – ШД, адреса – ША и управления ШУ.

Процессор выполняет машинные инструкции, обнаруживает, запросы на прерывание , контролирует работу ОШ, т.е. общей шины, ОШ – это единый унифицированный интерфейс, в физическом смысле – это высокочастотная магистраль передачи данных, через которую передаются адреса, данные, управляющие сигналы на все устройства вычислительного комплекса, включая процессор и память М. Процессор использует установленный набор сигналов для связи с памятью и для связи с внешними устройствами, благодаря чему в системе отсутствуют специальные команды ввода-вывода, при этом регистрам процессора, регистрам внешних устройств, которые являются источниками или приемниками при передаче информации на 81 ОШ отводятся адреса. В программах адреса регистров устройств рассматриваются как адреса ячеек памяти, что позволяет обращаться к ним с помощью адресных инструкций.

|

|

|

В микропроцессоре для программиста является доступными 8-разрядный регистр накопитель А (аккумулятор), регистры общего назначения B,C,D,E,H,L, регистр признаков F (флагов), одноразрядный регистр (триггер) разрешение прерываний INTE ( INTERRUPT ENABLE) в составе СП, 16- разрядный счетчик РС (PROGRAM COUNTER), который содержит адрес следующей команды-инструкции, т.е. хранит слово (команду), переданное из ОЗУ на исполнение и указатель стека SP (STACK POINTER). Стек автоматически используется при вызове подпрограмм и обработки прерываний.

Наличие в процессоре SP позволяет организовать в МП системе быструю работу с памятью, при которой не требуется указывать адрес ячейки ЗУ, к которой обращается МП.

В блок СОЗУ помимо РОН и SP, входят два буферных регистра W и Z.

F- регистр фиксирует 5 различных признаков: C (CARRY) – бит переноса; P/N (PARJTY), где Р – бит паритета (честность результата); V - ……..; AC (AUXILIARY CARRY) – бит вспомогательного переноса; Z (ZERO) – бит нуля; S (SIGN) – бит знака. (Три разряда F – регистра не используются и содержат биты – константы) (рис. )

рисунок - F – регистр признаков

Регистр-накопитель А совместно с F – регистром образуют регистровую пару слова состояния процессора PSW (PROCESSOR STATUS WORD) . Это слово отражает результаты текущих преобразований данных в 8-разрядном арифметико-логическом устройстве (АЛУ). Регистровая пара слово состояния процессора совместно с универсальными и функциональными регистрами обеспечивают связь процессора с ОШ, а через нее и с двумя другими устройствами комплекса.

Для процессора м.б. установлен приоритет, определяющий это взаимодействие с другими устройствами ОШ. Приоритет процессора и коды условий хранятся в слове состояния процессора PSW. Структура PSW показана на рис.

0-4 коды условий, вырабатываемые процессором после выполнения каждой инструкции:

разряд 0 (С) устанавливается в 1, если в результате выполнения инструкции имел место перенос разряда;

разряд 1 (P/V) устанавливаться в 1, если в результате выполнения инструкции имело место четность значения разрядов, в противном случае 0;

разряд 2 (Z) устанавливается в 1, если результат выполнения инструкции равен нолю, в противном случае 0:

разряд 3 (S) устанавливается в 1, если результат выполнения инструкции отрицательный, в противном случае 0.

4 – разряд слежения. Если установлен в 1, то после выполнения последней инструкции происходит прерывание работы программы. Используется в программах – отладчиках, устанавливается или сбрасывается программно.

5-7 - приоритет процессора. М. б. установлен один из восьми уровней приоритета процессора от 0 (000- в разрядах 5-7) до 7 (111 в разрядах 5-7).

Приоритет определяет возможность прерывания работы процессора по запросу от внешнего устройства. Наивысший приоритет 7 означает, что работа процессора не должна прерываться. Приоритет процессора устанавливается или изменяется программно.

12-13 – предшествующий режим работы процессора; определяет режим профессора, в котором находился процессор последним прерыванием.

14-15 – текущий режим работы процессора.

В каждый момент времени процессор работает в одном из двух режимов: системном (привилегированном), т.е. в состоянии обработки системной программы, для которой доступны все ресурсы комплекса, и пользовательском (непривилегированном) т.е. в состоянии программы пользователя, работающей под управлением операционной системы. Значение разрядов 14-15 - 00 означает работу процессора в системном режиме, 11 – в пользовательском. Данные разряды используются только при работе с УУВК, т.е. с диспетчером памяти.

Универсальные регистры. В состав процессора входят универсальные регистры, которые используются для выполнения инструкций, для запоминания промежуточных результатов в процессе выполнения программы, в качестве индексных и т.п.

Мнемоническое обозначение регистров в инструкциях R0, R1, R2, …, R5, SP (Stack pointer), PC (Program Counter).

Регистр SP – указатель стека,

Регистр PC – счетчик инструкций, т.е. всегда содержит адрес очередной инструкции, подлежащей выполнению.

Функциональные регистры. Используются аппаратным диспетчером памяти для преобразования виртуальных адресов в физические. Временная коммутация элементов МП системы осуществляться с помощью УУВК, который используется как управляющий счетчик и запоминается как стек со старшего разряда, а опрашиваться с младшего разряда. Когда процессор прерывает свою работу, УУВК, работающее как стек хранит состояние регистровой пары PSW и PC, т.е. данные, полученные до прерывания.

Память (М) представляется как последовательность ячеек размером один байт. Номер ячейки памяти является ее адресом. Шестнадцатиразрядная шина адреса МП позволяет обращаться к адресному пространству размером 216=65536=64 Кбайт.

Каждая МП система имеет свою структуру памяти. Количество ячеек памяти в системе часто меньше максимального возможного. Часть памяти выполнена в виде ОЗУ, остальная представляет ПЗУ. В любой области ОЗУ может быть размещен стек. Информация в стеке храниться в том порядке, в котором туда поступает, а извлекается в обратном порядке. При этом записываются или читаются два байта информации; а индекс указателя стека автоматически соответственно уменьшается или увеличивается на 2.

Для учета при программировании адресного пространства применяют карту памяти графическое распределение рабочего пространства памяти между отдельными блоками последовательных ячеек.

Микропроцессорная система на основе МП КР580 может иметь до 256 восьмиразрядных портов ввода и столько же портов вывода информации. Каждый канал ввода и вывода имеет адрес от 0 до 255 (0016 …FF16). Обращение к ним осуществляется командами IN (ввести байт канала ввода в накопитель) и OUT ( вывести байт из накопителя в канал). Вторым байтом этих команд всегда является адрес соответствующего канала (порта). Функциональные возможности набора команд определяется форматом данных, форматом команд и способами адресации.

В МП КР580 базовым информационным словом является байт (В7, В6, … , В0), где В7 старший, а В0 младший разряд байта. Для предоставления данных повышенной разрядности используется программно-организуемые многобайтовые слова.

Вопрос 17

Дата добавления: 2018-04-15; просмотров: 693; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!