Формат команды короче, он занимает один байт. Адресная часть размещена в КОП. Количество адресов (объем промежуточного ОЗУ) уменьшилось, но команда занимает в памяти меньше места.

2)Любая команда прямой адресации требует нескольких обращений в память команд.: КОП, адрес младший, адрес старший и адрес доступа к данным, т.е. минимум 4 раза на ША должен появиться адрес.. Косвенная адресация обходится двумя циклами: КОП, физический адрес доступа к данным. В косвенной адресации, прежде чем воспользоваться ее, требуется определить содержимое памяти: В регистровую пару необходимо занести адрес начальной ячейки памяти данных. Если этого не сделать, обращение произойдет по нулевому адресу, либо по случайному адресу. При обращении к следующей ячейке содержимое регистровой пары следует увеличить (уменьшить) на единицу специальной командой. Команды косвенной адресации дают заметное преимущество, если массив включает пересылки данных более десяти. Кроме того, косвенная адресация легко вписывается в структуру цикла, прямая же нет.

Модификация адресов

С расширением адресного пространства ОЗУ встала проблема увеличения разрядности адреса без изменения типа процессора. С этой целью разрабатываются различные подходы к получению физического адреса при сохранности структуры самого процессора.

1.Страничная адресация – это варианты позволяющие увеличить разрядность шины адреса. Дополнительно к адресной шине процессора комплексируются разряды с триггера адреса.(Рис.9). Триггер адреса – обычно счетчик с последовательным счетом и возможностью внешней установки данных.Дополнительно к ША. подключают выходные разряды такого счетчика., увеличивая адресное пространствово много раз. Основной недостаток этого способа -

1.Страничная адресация – это варианты позволяющие увеличить разрядность шины адреса. Дополнительно к адресной шине процессора комплексируются разряды с триггера адреса.(Рис.9). Триггер адреса – обычно счетчик с последовательным счетом и возможностью внешней установки данных.Дополнительно к ША. подключают выходные разряды такого счетчика., увеличивая адресное пространствово много раз. Основной недостаток этого способа -

|

|

|

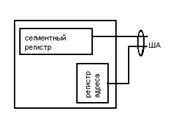

Рис. 9 Расширение шины адреса – необходимость управления счетчиком. Им необходимо управлять через внешние сигналы процессора. Идея страничной адресации интегрирована в сегментную адресацию. Этот счетчик выполнен внутри процессора, его выходы образуют дополнительные четыре разряда адреса.

Рис. 10. Смещение адреса на четыре разряда  В реальных схемах сегментный регистр выполняется 16разрядным, его содержимое сдвигается на 4 разряда влево и складывается с регистром адреса. В результате формируется смещение содержимого адресного регистра., общий адрес становится двадцатиразрябным.

В реальных схемах сегментный регистр выполняется 16разрядным, его содержимое сдвигается на 4 разряда влево и складывается с регистром адреса. В результате формируется смещение содержимого адресного регистра., общий адрес становится двадцатиразрябным.

При таком способе изменить адрес можно двумя путями. Появляющаяся степень свободы накладывает дополнительно заботу о состоянии всех внутренних регистров процессора. Сформировать физический адрес можно и с участием третьего регистра – регистра смещения или базового регистра. Его содержимое как бы перемещает физический адрес в пространстве адресов на некоторую величину. Если вместо базового использовать другой регистр получают относительный адрес.

|

|

|

Все способы модификации ориентируются на критерий: минимальное время формирования адреса при максимальном адресном пространстве. Прежде чем начать работу с процессором, необходимо определить все его регистры. Можно использовать и композицию, объеденные способы увеличения адресов, если возникает в том необходимость. В системе DEC существуют два дополнительных способа: автоинкрементный и автодекрементный. При косвенной адресации увеличение/ уменьшение на1 (2) содержимого адресного регистра происходит автоматически после каждого обращения в память.

Дата добавления: 2015-12-20; просмотров: 22; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!