А – функциональная схема; б – УГО

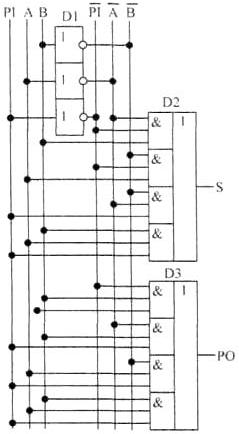

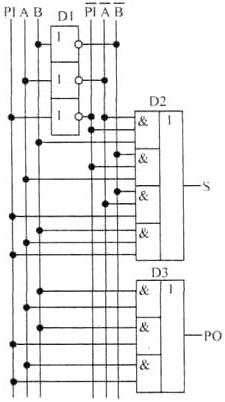

Теперь, точно так же как и в предыдущих случаях, в соответствии с правилами построения принципиальной схемы по произвольной таблице истинности получим схему полного двоичного одноразрядного сумматора, построенной на базе ИМС. Схема приведены на рисунках 20.5 и 20.6.

Примером одноразрядного двоичного сумматора может служить микросхема средней интеграции К155ИМ1. Обычно для выполнения вычислений в схемах цифровой обработки сигналов недостаточно точности одноразрядного сумматора. В них применяются 16- или даже 40-разрядные двоичные сумматоры.

|

|

| Рисунок 20.5 – Схема полного двоичного одноразрядного сумматора | Рисунок 20.6 – Минимизированная схема полного двоичного одноразрядного сумматора |

Многоразрядные сумматоры

Полные одноразрядные сумматоры являются основой, из которых получают различные схемы многоразрядных сумматоров.

Сумматор параллельного действия содержит одноразрядные сумматоры, число которых равно разрядности суммируемых двоичных слов.

Для того чтобы получить многоразрядный сумматор из полученного выше одноразрядного сумматора, достаточно соединить входы и выходы переносов соответствующих двоичных разрядов.

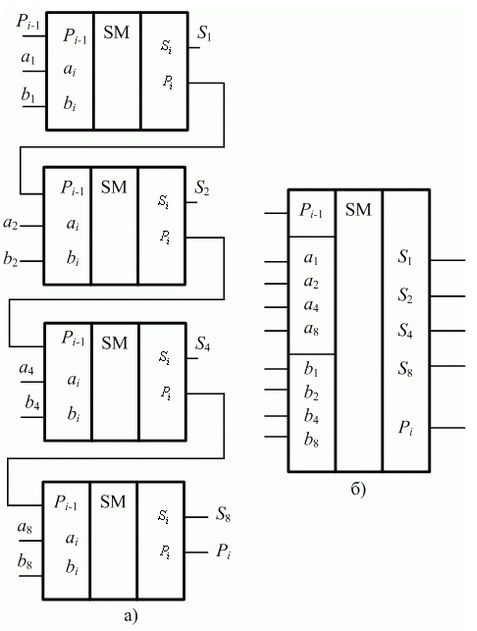

Для сложения многоразрядных двоичных чисел необходимо последовательно соединить нужное количество сумматоров так, как показано на рисунке 20.7. Здесь  и

и  – 4-разрядные слагаемые,

– 4-разрядные слагаемые,  – 4-разрядная сумма.

– 4-разрядная сумма.

|

|

|

Рисунок 20.7 – Четырехразрядный сумматор:

А – функциональная схема; б – УГО

Полный двоичный четырехразрядный сумматор изображается на схемах с использованием УГО, показанного на рисунке 20.7. Обратите внимание, что в этом обозначении входы двоичного слова  объединены в отдельное поле. Точно так же объединены входы двоичного слова

объединены в отдельное поле. Точно так же объединены входы двоичного слова  . Вход и выход сигналов переноса в приведенном УГО микросхемы тоже выделены в отдельные поля. Это не обязательно, и не требуется ГОСТом, однако изображенная таким образом микросхема намного более наглядно отображает свои функции.

. Вход и выход сигналов переноса в приведенном УГО микросхемы тоже выделены в отдельные поля. Это не обязательно, и не требуется ГОСТом, однако изображенная таким образом микросхема намного более наглядно отображает свои функции.

Приведенная на рисунке 20.7 схема не оптимизирована по быстродействию, она служит лишь для пояснения принципа действия многоразрядного двоичного сумматора. В применяемых на практике схемах никогда не допускают последовательного распространения переноса через все разряды многоразрядного сумматора, т. к. это снижает его быстродействие.

Для увеличения скорости работы двоичного сумматора используется отдельная схема формирования переносов для каждого двоичного разряда. Таблицу истинности для такой схемы легко получить из алгоритма суммирования двоичных чисел, а затем применить хорошо известные нам принципы построения цифрового устройства по произвольной таблице истинности.

|

|

|

Дата добавления: 2021-05-18; просмотров: 158; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!