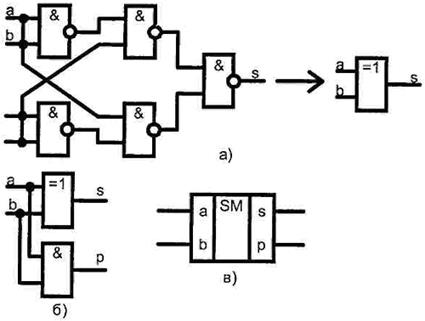

А, б – функциональные схемы; в – УГО; г) УГО схемы «исключающее ИЛИ»

ЛЕКЦИЯ № 20

по учебной дисциплине:

"ЦУ и МП в РЭО"

Тема 1.3: Последовательностные функциональные узлы

Занятие 1.3.12: " СЧЕТНЫЕ СХЕМЫ ЭВМ. СУММАТОРЫ"

План лекции:

Введение.

Назначение и классификация сумматоров. Комбинационный сумматор.

Многоразрядные сумматоры.

Примеры включения счетчиков и сумматоров в цифровые схемы. Цифровые умножители .

Заключение.

Учебная литература: [1], [2], [3], [6], [7].

Назначение и классификация сумматоров. Комбинационный сумматор

1.1. Классификация сумматоров

В настоящее время получили распространение схемы, в которых выходной сигнал формируется непосредственно в цифровой форме. Затем этот сигнал преобразуется в аналоговую форму при помощи цифроаналогового преобразователя. В составе этих микросхем широко используются сумматоры, умножители и цифровые фильтры.

Наиболее распространенной операцией в устройствах обработки цифровой информации является суммирование, т. е. арифметическое сложение двух чисел, имеющих одинаковое число разрядов. Операция сложения выполняется в соответствии с правилами арифметики, используемой в данном конкретном случае системы счисления.

Сумматоромназывают функциональный узел, выполняющий сложение одно- или многоразрядных двоичных чисел в соответствии с правилами двоичного сложения.

Многоразрядные сумматоры строятся на основе одноразрядных.

|

|

|

Сумматоры выполняют арифметическую операцию сложения двух чисел. Они имеют как самостоятельное значение, так и являются составной частью арифметическо-логических устройств (АЛУ), реализующих ряд разнообразных операций и являющихся непременной частью всех процессоров.

При организации различных вычислительных процессов суммированию отводится главная роль, оно является основной операцией. Например, вычитание – это суммирование с использованием ДК или ОК, умножение сводится к сдвигу и сложению (суммированию) двоичных чисел.

Следует отметить, что сумматоры являются логическими устройствами, функционируют по законам алгебры логики, но выполняют операцию арифметического, а не логического сложения.

В соответствии с определением, сумматор суммирует два числа. Выходной сигнал зависит только от двух входных сигналов, действующих на входе в текущий момент. Следовательно, сумматор является комбинационным устройством. Однако, некоторые сумматоры, например, накапливающий сумматор и другие, содержат в своем составе элементы памяти.

По числу выводов различают:

- полусумматоры;

- одноразрядные сумматоры;

- многоразрядные сумматоры.

Полусумматор имеет два входа и два выхода, предназначен для сложения двух одноразрядных слов и формирует на своих выходах сигнал суммы и сигнал переноса в старший разряд.

|

|

|

Одноразрядный сумматор имеет три входа и два выхода, предназначен для сложения двух одноразрядных слов и сигнала переноса из младшего разряда., формирует сигнал выхода и сигнал переноса в старший разряд.

Многоразрядный сумматор предназначен для сложения многоразрядных слов.

В настоящее время выпускают микросхемы одно-, двух- и четырехразрядные сумматоры. Маркировку микросхем – сумматоров можно определить по буквам ИМ – функциональное назначение, например, К555ИМ6 – четырехразрядный полный двоичный сумматор. На принципиальных схемах сумматоры обозначают буквами SM .

В зависимости от способа обработки чисел различают многоразрядные сумматоры:

- последовательного;

- параллельного;

- последовательно-параллельного действия.

В последовательных сумматорах сложение чисел осуществляется поразрядно, последовательно во времени.

В параллельных сумматорах действия сложение всех разрядов многоразрядных чисел происходит одновременно.

По способу тактирования различают сумматоры:

- синхронные;

- асинхронные.

|

|

|

В синхронных сумматорах операция сложения осуществляется по тактовым импульсам, и время ее проведения не зависит от длины разрядов кодов, остается постоянным.

В асинхронных сумматорах время выполнения операции зависит от длины входных кодов и поэтому необходимо формировать признак окончания операции.

В зависимости от используемой системы счисления различают сумматоры:

- двоичные;

- двоично-десятичные и др.

Аппаратная сложность и быстродействие сумматора являются очень важными параметрами и поэтому разработано множество вариантов сумматоров, которые имеют разветвленную классификацию. В виду особой важности на основе различных алгоритмов синтеза разработано большое количество разнообразных схем сумматоров:

- одноразрядный сумматор;

- сумматор для последовательных операндов;

- сумматор для параллельных операндов с последовательным переносом;

- сумматор для параллельных операндов с параллельным переносом;

- сумматор с последовательным распространением переноса по цепочке замкнутых ключей;

- сумматор групповой структуры с цепным переносом;

- сумматор групповой структуры с параллельным межгрупповым переносом;

- сумматор с условным переносом;

|

|

|

- накапливающий сумматор.

Наряду с сумматорами могут быть реализованы вычитатели, однако это почти никогда не делается, поскольку вычитание выполняется посредством сложения с применением ДК либо ОК.

Кроме параметров, определяющих условия эксплуатации сумматоров как микросхем, используют следующие параметры, необходимые при решении задачи синтеза электрических схем устройства обработки цифровой информации на основе сумматоров:

- разрядность;

- способ суммирования двоичных чисел (последовательный или параллельный);

- тип входной логики сумматора по входу  и по входу

и по входу  ;

;

- наличие и организация входов управления;

- способ организации цепи переноса;

- тип выходной логики;

- быстродействие (время задержки сигнала и переноса);

- потребляемый ток питания;

- особенности монтажа при увеличении разрядности сумматора.

Подробно вопросы двоичной арифметики будут освещены в лекции № 22. Рассмотрим наиболее характерные схемы построения сумматоров.

1.2.Одноразрядный полусумматор

В сумматорах операция суммирования чисел, представленных в двоичном коде, осуществляется поразрядно.

Простейший случай – это суммирование двух одноразрядных слов. В десятичной системе

(20.1)

(20.1)

что соответствует в двоичной системе счисления

(20.2)

(20.2)

В последнем случае результат суммы оказался двухразрядным 102 = 210. Обычное явление, когда при суммировании двух чисел в любой системе счисления результат имеет на один разряд больше. В двоичной системе единица в старшем разряде суммы называется единицей переноса. Сведем формулы (20.2) в таблицу 20.1.

Таблица 20.1 – Таблица истинности полусумматора

| Слагаемые | Сумма S | Перенос Р | Математическое выражение | |

| 0 | 0 | 0 | 0 | 0+0 = 010 (002) |

| 0 | 1 | 1 | 0 | 0+1 = 110 (012) |

| 1 | 0 | 1 | 0 | 1+0=110 (012) |

| 1 | 1 | 0 | 1 | 1+1 =210 (102) |

Обратите внимание,что сигналы в приведенной таблице истинности расположены в порядке, принятом для схем, т. е. в соответствии с тем, что сигнал распространяется слева направо. В результате перенос, который имеет двоичный вес больший, по сравнению с суммируемыми разрядами, записан правее. В математике принят другой порядок разрядов числа. Старший разряд на бумаге записывается самым левым, а младший разряд – самым правым. В результате может возникнуть путаница. Чтобы этого не произошло, введен десятичный эквивалент каждой строки таблицы истинности полусумматора (таблица 20.1).

Из таблицы 20.1 получим аналитические выражения для суммы S и переноса Р. Выражение для Sможно записать с помощью известной операции ИСКЛЮЧАЮЩЕЕ-ИЛИ

(20.3)

(20.3)

(20.4)

(20.4)

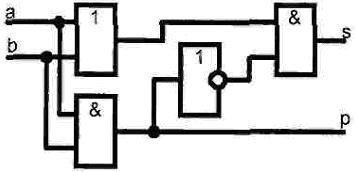

Техническая реализация полусумматора на основе формул (20.3) – (20.4) представлена на рисунке 20.1.

Рисунок 20.1 – Схема полусумматора в базисе И-НЕ (сумматор по модулю 2):

а, б – функциональные схемы; в – УГО; г) УГО схемы «исключающее ИЛИ»

Используя представление в базисе ИЛИ-НЕ,из таблицы 3.17 получим

(20.5)

(20.5)

На основе формулы (20.5) построим схему полусумматора, содержащего меньшее число логических элементов (рисунок 20.2)

Рисунок 20.2 – Схема полусумматора в базисе ИЛИ-НЕ

В то же время схема (см. рисунок 20.2) содержит различные элементы: И, НЕ, ИЛИ.

Полусумматор (см. рисунки 20.1; 20.2) не имеет входа переноса с предыдущего разряда, поэтому его можно использовать только в младших разрядах устройства обработки многоразрядных двоичных слов.

Полусумматоры выпускаются в виде отдельных микросхем и используются в качестве отдельных модулей в составе больших интегральных микросхем, поэтому ГОСТом предусмотрено УГО полусумматора. Оно приведено на рисунке 20.1 в.

Полусумматор формирует перенос в следующий разряд, но не может учитывать перенос из предыдущего разряда, поэтому он и называется полусумматором. В результате такой особенности полусумматор не может использоваться в качестве отдельного устройства.

Интегральные схемы, а полусумматоров "ИЛ". Например, 155ИЛ7 – полусумматор.

Практический интерес представляет полный сумматор.

Сумматор по модулю 2 выполняет суммирование без учета переноса между двоичными разрядами.В полном двоичном сумматоре его необходимо учитывать, поэтому требуются элементы, позволяющие формировать перенос в следующий двоичный разряд.

1.3.Одноразрядный комбинационный сумматор

Одноразрядным комбинационным сумматоромназывают операционный элемент, выполняющий микрооперацию суммирования двух или нескольких одноразрядных чисел.

Таблицу истинности полного одноразрядного двоичного сумматора (таблица 20.2), можно получить из правил арифметического суммирования двоичных чисел. В обозначении входов и выходов полного сумматора использовано следующее правило: в качестве входов использованы одноразрядные двоичные числа  и

и  ; сумма – это одноразрядное двоичное число

; сумма – это одноразрядное двоичное число  ; перенос обозначен буквой

; перенос обозначен буквой  ; для обозначения входа переноса используется сочетание букв

; для обозначения входа переноса используется сочетание букв  (i – сокращение от английского слова input, вход) или (РI); для обозначения выхода переноса используется сочетание букв

(i – сокращение от английского слова input, вход) или (РI); для обозначения выхода переноса используется сочетание букв  или РО (О – сокращение от английского слова output ,выход).

или РО (О – сокращение от английского слова output ,выход).

Правила двоичного сложения одноразрядного сумматора можно представить в виде таблицы истинности (таблица 20.2) будущей логической схемы двоичного сумматора и построить эту схему по ранее изложенным принципам.

Для текущего разряда суммы  логическое выражение имеет вид:

логическое выражение имеет вид:

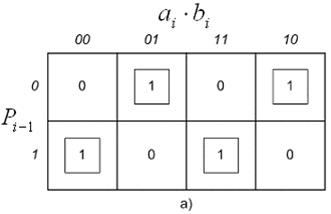

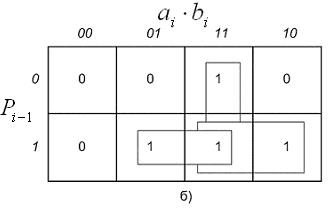

причем согласно карте Карно, представленной на рисунке 20.3 а, данное выражение не минимизируется. Для выходного переноса  минимизация возможна, поэтому логическое выражение согласно рисунку 20.3 б, получается следующим:

минимизация возможна, поэтому логическое выражение согласно рисунку 20.3 б, получается следующим:

|

|

| Рисунок 20.3 – Карты Карно для одноразрядного сумматора: а – для текущего разряда суммы; б – для текущего разряда выходного переноса | |

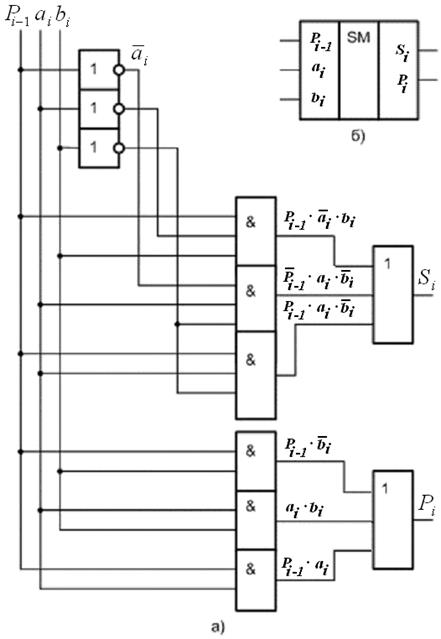

Схема одноразрядного сумматора и его УГО представлены на рисунке 20.4.

Рисунок 20.4 – Одноразрядный сумматор:

Дата добавления: 2021-05-18; просмотров: 194; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!