Последовательно-параллельного регистра

В этой схеме для переключения регистра из последовательного режима работы в параллельный используется вход V. Подача на этот вход единичного потенциала превращает схему в параллельный регистр. При этом на входы ключей, подключенных к информационным входам D, подается единичный потенциал. Это приводит к тому, что сигналы с входов параллельной записи данных поступают на входы логических элементов "ИЛИ", а на входы ключей, подключенных к выходам предыдущих триггеров, подаются нулевые потенциалы. То есть на выходах этих ключей будут присутствовать нулевые потенциалы, и они не будут мешать работе.

(Слайд) Подача на вход V нулевого потенциала приводит к отключению входов параллельных данных от входов триггеров. Сигналы с выхода предыдущего триггера свободно проходят через верхние логические элементы "И" на вход последующего триггера, т. к. на его второй вход подается единичный потенциал.

Инверторы на входах V и С использованы для усиления входного сигнала по току. В результате применения такого решения входной ток микросхемы будет равен не суммарному току четырех логических элементов "И", а входному току инвертора.

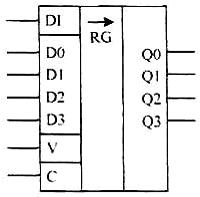

УГО универсального регистра, принципиальная схема которого показана на рисунке 17.6, приведено на рисунке 17.7.

Рисунок 17.7 – УГО универсального регистра на принципиальных схемах

Вход последовательного ввода данных на этом рисунке обозначен как DI и отделен от других групп входов чертой. Точно так же выделены в отдельные группы и входы управления V и синхронизации С.

|

|

|

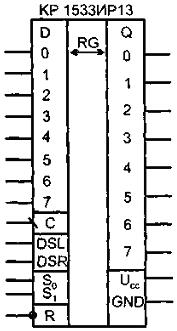

(Слайд) Типичным представителем многорежимных регистров является микросхема ИР13 серии КР1533 и других. Это восьмиразрядный регистр с возможностью двусторонних сдвигов с допустимой тактовой частотой до 25 МГц при токе потребления до 40 мА. Условное обозначение регистра ИР13 приведено на рисунке 17.8.

Одна из возможных схем трехразрядного реверсивного регистра с двумя последовательными информационными входами, для сдвига информации влево DSL, и вправо DSR, с параллельными входами записи (D0..D2), синхровходом C, входом  установки в 0 всех триггеров и двумя входами выбора режима M1,M0, приведена на рисунке 17.9.

установки в 0 всех триггеров и двумя входами выбора режима M1,M0, приведена на рисунке 17.9.

К D-входу любого разряда, за исключением крайних, подключены, через входы 1 и 2 мультиплексора, выходы и левого и правого соседних триггеров.

Если M1=0, а M0=1, то к входам D подключены первые входы мультиплексоров и информация в каждый триггер, кроме нулевого записывается от левого соседа (происходит сдвиг вправо). Вход DSR служит в этом режиме для последовательного ввода информации.

Рисунок 17.8 – УГО универсального регистра ИР13

|

|

|

(Слайд)

Рисунок 17.9 – Часть функциональной схемы (3 разряда) реверсивного 8-ми разрядного регистра 1533ИР13

(Слайд) Если M1=1, M0=0, то к входам D подключены вторые входы мультиплексоров и информация в каждый триггер, кроме последнего записывается от правого соседа (происходит сдвиг влево). Для последовательного ввода данных в этом режиме используется вход DSL.

При M1=M0=1 происходит параллельная запись Qi=Di положительным фронтом тактового сигнала.

Для хранения информации необходимо подать комбинацию M1=M0=0.

В этом случае к D-входам триггеров подключатся нулевые входы мультиплексоров (на схеме не показаны). Чтобы не произошло несанкционированной записи схема ИЛИ-И запрещает в этом режиме прохождение синхроимпульсов. По такой схеме выполнен 8-разрядный регистр 1533ИР13.

Реверсивный регистр может использоваться для быстрого (всего за n тактов) деления и умножения двоичных чисел на  , где n-число сдвигов. Например (рисунок 17.10), вместо числа 5, после сдвига влево на 2 разряда, стало число 20.

, где n-число сдвигов. Например (рисунок 17.10), вместо числа 5, после сдвига влево на 2 разряда, стало число 20.

(Слайд)

Рисунок 17.10 – Процесс умножения и деления числа

В универсальных регистрах

Устройства (в том числе регистры), в которых для записи входного параллельного кода Di используется сигнал разрешения записи L, а тактовый сигнал C не используется, называютсяустройствами с асинхронной параллельной записью кода (рисунок 17.11).

|

|

|

Рисунок 17.11 – Входные управляющие сигналы в цифровых устройствах

(Слайд) Устройства (в том числе регистры), в которых для записи входного параллельного кода Di необходим, во-первых, сигнал разрешения записи L и, во-вторых, перепад синхросигнала на тактовом входе C – называются устройствами с синхронной параллельной записью кода.

Условные обозначения таких входов могут совпадать поэтому для точной идентификации способа записи необходимо обращаться к справочникам (таблица состояний либо описание).

Дата добавления: 2021-05-18; просмотров: 95; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!