А) функциональная схема; б) УГО

ЛЕКЦИЯ № 17

по учебной дисциплине:

"ЦУ и МП в РЭО"

Тема 1.3: Последовательностные функциональные узлы

Занятие 1.3.6: " Регистры и регистровая память"

План лекции:

Введение.

Регистры последовательного действия.

Универсальные регистры.

Регистровая память. Сверхоперативное запоминающее устройство.

Заключение.

Учебная литература: [1], [2], [3], [6], [7]

Регистры последовательного действия

(Слайд) Схемы, в которых триггеры соединены последовательно, называютсяпоследовательными регистрами.

Последовательный регистр (регистр сдвига) обычно служит для преобразования последовательного кода в параллельный, и наоборот.

В регистрах последовательного действия ввод и вывод информации осуществляется последовательно (разряд за разрядом), начиная с младшего или старшего разряда. При записи очередного разряда ранее записанная в последовательный регистр информация сдвигается. Запись или считывание одного разряда (сдвиг) выполняется под действием одного синхронизирующего импульса.

(Слайд) Сдвиг данных в регистре – одна из основных операций в цифровых устройствах. С ее помощью можно:

- преобразовать параллельный код в последовательный, сдвигая по тактам двоичное число от разряда к разряду;

- выполнить операции умножения и деления на число  , т. к. сдвиг числа на один разряд вправо означает уменьшение его в два раза, а влево – увеличение в два раза. Таким образом, чтобы разделить или умножить число, записанное в регистре на

, т. к. сдвиг числа на один разряд вправо означает уменьшение его в два раза, а влево – увеличение в два раза. Таким образом, чтобы разделить или умножить число, записанное в регистре на  необходимо его сдвинуть вправо или влево на n-разрядов.

необходимо его сдвинуть вправо или влево на n-разрядов.

|

|

|

Операция сдвига осуществляется с помощью специального последовательного соединения триггеров, составляющих последовательный (сдвигающий) регистр. Сдвигающие регистры строятся на основе синхронных RS , D, JK-триггерах. Наиболее приспособленными для сдвигающих регистров являются двухступенчатые триггеры, т. к. они свободны от проблемы гонок.

(Слайд) С приходом очередного положительного фронта синхроимпульса C , сигнал с входа i-го триггера через времяtзд.р. окажется на его выходе и поступит на вход следующего (i+1)-го триггера. Однако на его выход эта информация не перепишется, т. к. длительность активного фронта t0,1 меньше tзд.р. На этом процесс сдвига данных на один разряд закончится до прихода следующего положительного фронта тактового сигнала. Отсюда понятно, почему нельзя использовать триггеры со статическим управлением. Каждый раз при C = 1 вся цепочка окажется прозрачной от входа до выхода регистра, и значение  будет записано во все триггеры.

будет записано во все триггеры.

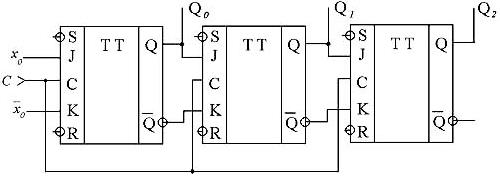

На рисунке 17.1 показан фрагмент схемы сдвигающего регистра на JK-триггерах. (Слайд)

|

|

|

Рисунок 17.1 – Фрагмент схемы сдвигающего регистра на JK -триггерах

Вход  обладает наивысшим приоритетом, если

обладает наивысшим приоритетом, если  , то

, то  , а

, а  и все триггеры обнуляются, независимо от остальных поступающих сигналов.

и все триггеры обнуляются, независимо от остальных поступающих сигналов.

Применение последовательного кода связано с необходимостью передачи большого количества двоичной информации по ограниченному количеству соединительных линий.При параллельной передаче разрядов требуется большое количество соединительных проводников. Если двоичные разряды последовательно бит за битом передавать по одному проводнику, то можно значительно сократить размеры соединительных линий на плате (и размеры корпусов микросхем).

Одно из применений регистров сдвига с параллельной загрузкой кода заключается в преобразовании параллельного формата данных в последовательный, передаче этих данных по однопроводной линии связи (вторая линия должна быть, как минимум "землей" или экраном) и обратном преобразовании последовательной информации в параллельную (рисунок 17.2). (Слайд)

Рисунок 17.2 – Схема преобразования и передачи двоичного кода

Такая схема применяется в коммуникационных портах ЭВМ (COM-порты), в микросхеме К580ИК51, а также в модемах.

|

|

|

В настоящее время этот же принцип применяется для увеличения скорости передачи цифровых сигналов. Это связано с тем, что для малого количества соединительных проводников можно применить усложненную схему согласования и вместо обычного соединительного провода использовать микрополосковую линию передачи сигналов.

(Слайд) При обсуждении схемы преобразования параллельного кода в последовательный часто возникает вопрос – а почему бы не воспользоваться для этого преобразования мультиплексором? В качестве ответа можно привести то, что время переключения мультиплексора зависит от двоичного кода на адресном входе мультиплексора. Различные разряды этого кода, в свою очередь, могут поступать на вход мультиплексора тоже неодновременно.

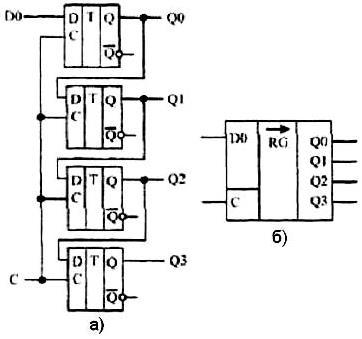

(Слайд) Принципиальная схема последовательного регистра, собранного на основе двухступенчатых D -триггеров, и позволяющего осуществить преобразование последовательного кода в параллельный, приведена на рисунке 17.3 а, а его УГО приведено на рисунке 17.3 б. В обозначениях регистров сдвига направление стрелки, указывающей сдвиг, условно. В разных справочниках, ее направление различно. Условно принимается, что сдвиг производится от младшего разряда к старшему.

|

|

|

Входы синхронизации отдельных триггеров в схеме последовательного регистра, как и в схеме параллельного регистра, объединяются. Это обеспечивает одновременность смены внутреннего состояния всех триггеров, входящих в состав последовательного регистра.

Преобразование последовательного кода в параллельный производится следующим образом. Отдельные биты двоичной информации последовательно подаются на вход D0. Каждый бит сопровождается отдельным тактовым импульсом, который поступает на вход синхронизации С.

После поступления первого тактового импульса логический уровень, присутствующий на входе D0, запоминается в первом триггере и поступает на его выход, а т. к. он соединен с входом второго триггера, то теперь этот потенциал будет присутствовать на входе второго триггера.

Рисунок 17.3 – Схема последовательного регистра:

а) функциональная схема; б) УГО

После поступления второго тактового импульса логический уровень, присутствующий на входе второго триггера, запоминается в нем и поступает на его выход, а т. к. он соединен с входом третьего триггера, то теперь этот потенциал подан на вход третьего триггера. Одновременно в первом триггере запоминается второй бит входного последовательного кода.

После поступления четвертого тактового импульса в триггерах регистра будут записаны уровни бит, которые последовательно присутствовали на входе D0 в моменты поступления предыдущих импульсов тактовой синхронизации. Теперь этими логическими уровнями можно воспользоваться, например, для отображения на индикаторах.

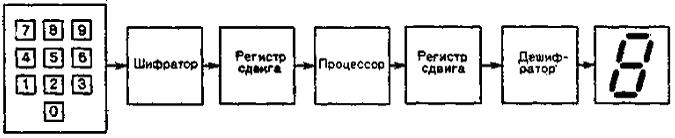

(Слайд) Регистры сдвига часто используются для временного хранения данных. На рисунке 17.4 иллюстрируется типичный пример такого применения в цифровой системе. Можно считать, что данная цифровая система представляет собой калькулятор. Обратите внимание на использование регистров сдвига в качестве временной буферной памяти между шифратором и процессором, а также между процессором и дешифратором. Их можно использовать и в других местах цифровой системы.

Рисунок 17.4 – Цифровая система, использующая регистр сдвига

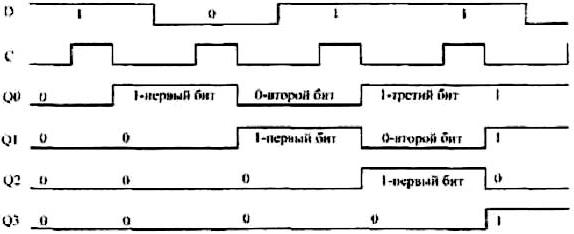

(Слайд) Пусть на вход последовательного регистра поступает сигнал, временная диаграмма которого изображена на рисунке 17.5, тогда состояние выходов этого регистра будет последовательно принимать значения, записанные в таблице 17.1.

Рисунок 17.5 – Временные диаграммы сдвигового регистра

(Слайд)

Таблица 17.1 – Состояние выходов сдвигового регистра

В таблице 17.1 символом «X» обозначено неопределенное значение, возникающее в триггерах регистра при включении питания или оставшееся от предыдущего цикла работы схемы.

Сдвигающие регистры можно строить различным образом, зависящим от выполнения требуемой операции: сдвиг влево, сдвиг вправо, сдвиги влево и вправо. Регистры, имеющие возможность сдвигать информацию и влево, и вправо называют реверсивными. В их составе обязательно присутствует управляющая схема, которая определяет, в соответствии с командой, направление сдвига информации. Управляющая схема является схемой комбинационного типа и может быть синтезирована на основе теории переключательных функций для каждого конкретного случая.

Универсальные регистры

Название указывает, что сдвиг данных от разряда к разряду может производиться, как в одну сторону, так и в другую.

(Слайд) Регистры сдвига выполняют обычно как универсальные последовательно-параллельные микросхемы. Это связано с необходимостью записи в регистр параллельного двоичного кода при преобразовании параллельного кода в последовательный. Переключение регистра из параллельного режима работы в последовательный и наоборот осуществляется при помощи мультиплексора (коммутатора). Использование коммутатора позволяет подключать входы триггероврегистра либо к внешним выводам микросхемы, либо к выходу предыдущего триггера.

Двухвходовый мультиплексор можно реализовать при помощи логических элементов "2И-2ИЛИ". Элементы "И" при этом работают в качестве электронных ключей, а элементы "ИЛИ" объединяют их выходы.

Схема универсального последовательно-параллельного регистра с использованием коммутаторов на логических элементах "2И-2ИЛИ" приведена на рисунке 17.6. (Слайд)

Рисунок 17.6 – Принципиальная схема универсального

Дата добавления: 2021-05-18; просмотров: 94; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!