Программирование с использованием отладочной платы STM32F4Discovery

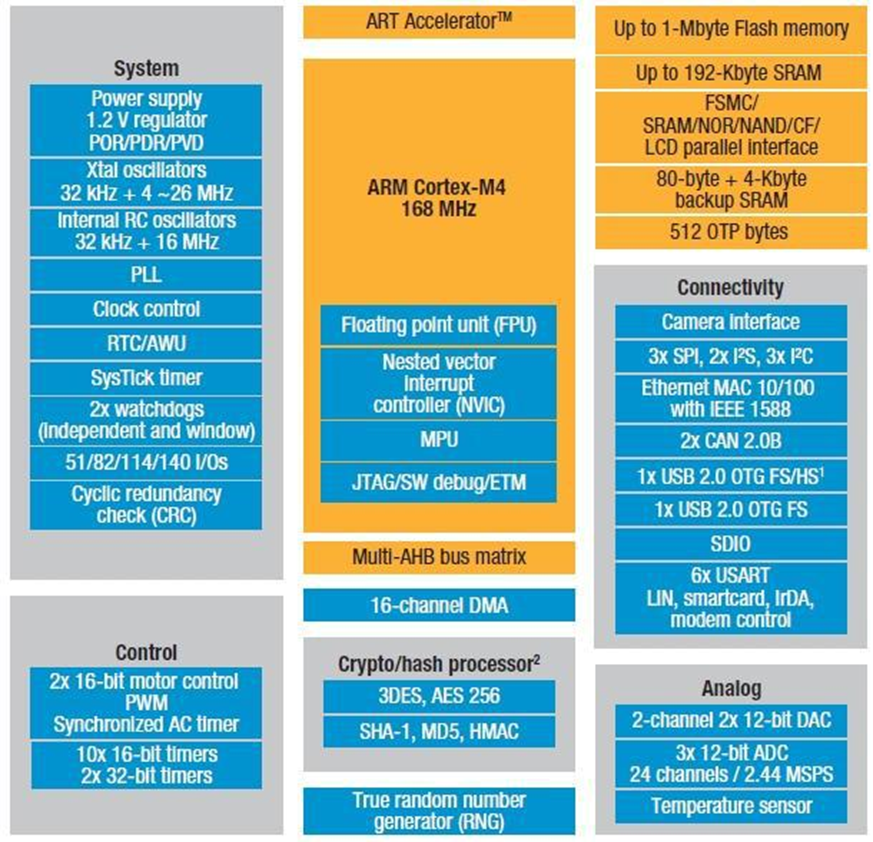

· микроконтроллер STM32F407VGT6 с частотой 168Mhz на 32-битном ядре ARM Cortex-M4F, 1 Мб флэш-памяти, 192 Кб оперативной памяти в корпусе LQFP100.

· встроенный ST-LINK/V2 с возможностью использования ST-LINK/V2 как отдельного устройства (с SWD разъемом для программирования и отладки).

LIS302DL, ST MEMS датчик движения, 3-осевой акселерометр с цифровым выходом.

· MP45DT02, ST MEMS датчик звука, всенаправленный цифровой микрофон.

CS43L22, аудио ЦАП со встроенным усилителем класса D.

четыре светодиода, LD3 (оранжевый), LD4 (зеленый), LD5 (красный) и LD6 (синий).

· две кнопки (пользовательская и reset)

порт USB OTG FS и коннектор micro-AB USB Client

штырьки для быстрого соединения с другими устройствами подключенные ко всем выводам LQFP100.

·

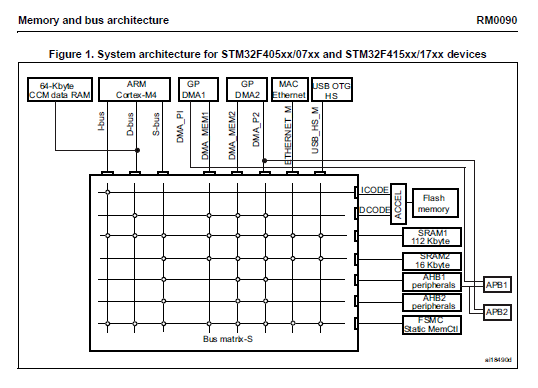

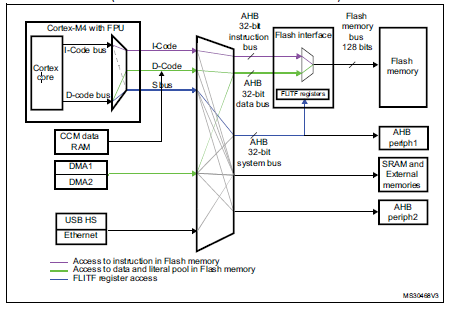

STM32F407VG6 МК, основан на базе arm-cortex-m4f ядра, в которое включен набор fpu и dsp инструкций для ускорения работы. Помимо ядра работающего на частоте 168 МГц и имеющего производительность 210 МИВС, имеется 7 канальная матричная шина AHB которая позволяет без простоя коммутировать независимо основные блоки МК. Помимо AHB помочь производительности призваны 16 канальный DMA и ART accelerator(tm) (который к сожалению в А версии не работает, чип этой версии и стоит на плате). 192 КБ статического ОЗУ и 1 МБ флеш памяти. Большое количество интерфейсов как последовательных (4 spi, 2 i2s, 2 i2c, 3 usart, 3 uart, 2 usb otg fs/hs, Ethernet MAC 10/100, sdio, 2 can 2.0b) так и параллельных (display 8080, camer 8 — 14 bit, gpio, FSMC). и много других периферийных блоков (таймеров, adc, dac и пр.).

|

|

|

Шинная матрица обеспечивает доступ от master к slave, обеспечивая параллельный доступ и эффективную работу, даже когда несколько высокоскоростных периферийных устройств работают одновременно. Оперативное ОЗУ объемом 64 КБ (память с привязкой к ядру) не является частью матрицы шины и может быть доступно только через ЦП. Эта архитектура показана на рисунке 1.

Рис. 22 Встроенные модули ARM Cortex-M4

Семейство микроконтроллеров STM32

Семейство микроконтроллеров STM32 построено с использованием 32-рязрядного ядра Cortex различных версий (в микроконтроллере, установленном на плате используется ядро Cortex-M4). Некоторые основные характеристики ядра микроконтроллеров STM32 представлены в табл. 1.1.

Таблица 1.1. Основные характеристики ядра микроконтроллеров STM32

|

|

|

| Характеристика | Значение |

| Ширина слов для данных, разряд | 32 |

| Архитектура | Гарвард |

| Конвейер | 3-ступенчатый |

| Набор инструкций | RISC |

| Организация памяти программ, разряд | 32 |

| Буфер предвыборки, разряд | 2х64 |

| Средний размер инструкции, байт | 2 |

| Тип прерываний | Векторизированные |

| Задержка реагирования на прерывания | 12 циклов |

| Режимы управления энергопотреблением | Сон, сон по выходу, глубокий сон |

| Отладочный интерфейс | ST-LINK, JTAG |

Микроконтроллеры данного типа построены на гарвардской архитектуре и имеют 3-ступенчатый конвейер, который минимизирует время выполнения команд. Они разработаны для построения систем с максимальной энергоэффективностью и имеют несколько режимов управления энергопотреблением. В них используются внутренние интерфейсы памяти шириной больше, чем средняя длина инструкции. Это минимизирует число доступов к шине памяти, а, следовательно, и потребление электроэнергии, связанное с операциями по шине и чтением энергонезависимой памяти. Технология непрерывной обработки прерываний с исключением внутренних операций над стеком (tail chaining) сокращает время реакции на прерывания и исключает лишние операции со стеком.

|

|

|

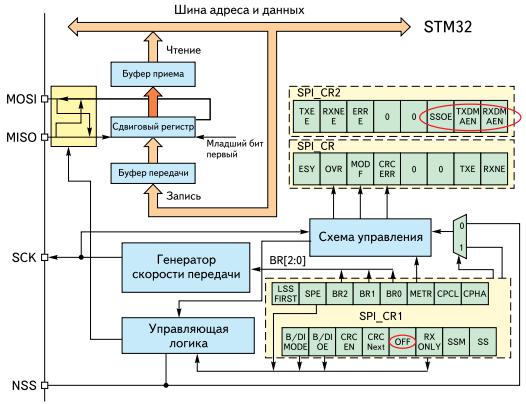

На рис. 1.2 представлено упрощенное представление цифрового периферийного устройства. Периферийный узел может быть разделен на два главных блока. Первый блок – это ядро, которое

содержит конечные автоматы, счетчики и любой вид комбинаторной или последовательной логики. Оно предназначено для выполнения задач, не требующих участия процессора, таких как простые задачи передачи данных, управления аналоговыми входами или выполнения функций, привязанных к синхросигналам. Ядро периферийного узла связывается с внешним миром через порты ввода/вывода МК. Внешние соединения могут состоять из нескольких сигналов или сложных шин. Второй блок – настройка и управление периферией, которые осуществляются приложением через регистры, соединенные с внутренней шиной, разделяемой с другими ресурсами МК.

Рис. 23. Представление цифрового периферийного устройства

Плата STM32F4 Discovery оснащена:

- микроконтроллером STM32F407VGT6 с ядром Cortex-M4F тактовой частотой 168 МГц, 1 Мб Flash-памяти, 192 кб RAM в корпусе LQFP100;

- отладчиком ST-Link/V2 для отладки и программирования МК;

- питанием платы через USB или от внешнего источника питания 5 В;

- датчиком движения ST MEMS LIS302DL и выходами цифрового акселерометра по трем осям;

|

|

|

- датчиком звука ST MEMS MP45DT02;

- звуковым ЦАП CS43L22;

- восемью светодиодами: LD1 (красный/зеленый) для USB-подключения, LD2 (красный) для

питания 3.3 В, четыре пользовательские светодиода: LD3 (оранжевый), LD4 (зеленый), LD5 (красный), LD6 (синий) и два светодиода для USB On-The-Go – LD7 (зеленый) и LD8 (красный)$

- двумя кнопками (для программирования пользователем и для перезапуска).

Лекция 3,4.

Дата добавления: 2020-01-07; просмотров: 223; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!