Процессорное ядро микроконтроллера

Программирование контроллера STM 32 на основе ЦПУ АРМ Cortex-M4

Оглавление

Лекция 1-2. 7

Классификация и структура микроконтроллеров. 7

Память программ.. 12

Память данных. 14

Оперативная память. 15

Энергонезависимая память данных. 16

Структурная организация микроконтроллера i8051. Общие характеристики.. 16

Арифметико-логическое устройство. 17

Структурная организация AVR - микроконтроллера. 18

Стадии подготовки программного обеспечения для микроконтроллеров. 20

Языки программирования для микроконтроллеров. 21

Этапы разработки программ.. 27

Общие характеристики семейства. 30

Встроенные интерфейсы коммуникации.. 30

Модуль операций с плавающей запятой (или с плавающей точкой). 33

Урок 1 - GPIO. Порты ввода-вывода. 33

Регистры GPIO.. 36

STM32CubeMX.. 37

Программирование с использованием отладочной платы STM32F4Discovery. 49

Семейство микроконтроллеров STM32. 54

Лекция 3,4. 57

Многофункциональные УВВ (устройство ввода – вывода). 57

Безопасность. 60

Альтернативные функции.. 60

АЦП.. 61

АЦП последовательного приближения. 61

Функция оконного компаратора. 65

Базовая конфигурация АЦП.. 65

Режимы сдвоенных преобразований.. 67

Режимы одновременного преобразования инжектированных групп и одновременного преобразования регулярных групп.. 68

Комбинированный режим одновременного преобразования регулярных/инжектированных групп 69

Режимы быстрых и медленных преобразований со смещением во времени.. 69

|

|

|

Режим поочередного запуска. 70

Комбинирование режима одновременного преобразования регулярной группы и режима поочередного запуска. 70

Комбинирование режима одновременного преобразования инжектированной группы и режима со смещением во времени. 71

Регулярные каналы (regular channels). 72

Инжектированные (Injected channels). 72

Независимая работа. 73

Парная работа. 73

Независимая работа. 75

АЦП в STM32. 79

Скорость оцифровки, тактирование. 92

Физические линии ввода, группы каналов. 93

Включение, запуск оцифровки, режимы работы модулей ADC.. 94

Одиночные и непрерывные преобразования. 94

Сканирование списка каналов. 95

Использование DMA.. 95

Опрос инжектированных каналов. 95

Прерывистый режим опроса каналов. 96

Режим калибровки.. 96

Предельный компаратор. 97

Регистры.. 98

Таймер. 100

TIM1. 103

Подача единичного импульса на примере ШИМ... 106

Блок контроллера master/slave. 106

Блок базы времени. 107

Блок канала таймера. 108

Блок функции Break. 110

Каскад фильтрации. 110

Функция пред загрузки регистров таймера. 111

Тактирование таймера STM32 от внешнего источника . 113

Блок синхронизации. 114

Режим 1 внешнего тактирования. 115

Режим 2 внешнего тактирования. 117

Отличия режима 1 и режима 2 внешнего тактирования. 119

|

|

|

ШИМ-регулирование с использованием входа break. 120

Генерация сигнала произвольной формы с помощью пакетных передач DMA таймера. 122

DMA-burst таймера. 123

TIMx_DMAR. 123

Настройка регистров адреса контроллера DMA.. 124

Регистр управления DMA-burst таймера. 124

Генерация сигнала из N-импульсов с использованием синхронизации таймера. 126

Обзор синхронизации таймера. 126

Конфигурация master-таймера. 127

Конфигурация slave-таймера. 128

Функция коммутации таймера STM32. 128

Таймеры общего назначения TIM 9- TIM 14. 128

Блок-схема таймеров TIM10/11, TIM13/14. 129

Блок-схема таймеров TIM9, TIM12. 130

Тактирование счётчиков. 131

Лекция 5. 131

Прерывания.. 131

Прерывания и события. 132

Разрешение прерываний.. 135

Настройка прерывания в периферии.. 137

Особенности обработки прерываний.. 138

Вложенность прерываний. 138

Работа КВВП при входе в исключительные ситуации и выходе из них. 139

Непрерывная обработка прерываний с исключением внутренних операций над стеком.. 141

Обработка опоздавшего высокоприоритетного прерывания. 142

Таблица векторов исключительных ситуаций. 142

Лекция 1-2

Введение

|

|

|

В процессе миниатюризации функциональные блоки, которые в обычных компьютерных системах размещались в отдельных интегральных схемах (процессор, память, порты ввода \ вывода, таймеры, контроллеры прерываний и пр.) стали объединять на одном кристалле. Так появились микроконтроллеры или, как их принято называть в отечественной литературе, однокристальные ЭВМ. Такой подход позволил значительно сократить не только размеры встроенных систем, но также сложность и сроки их разработки, а, следовательно, и стоимость. Сокращение числа компонентов повлекло за собой повышение надежности готовых устройств. В некоторых случаях для построения полноценной встроенной системы достаточно одной микросхемы – микроконтроллера.

Основные требования, которые потребители предъявляют к управляющим блокам приборов (микроконтроллерам) можно сформулировать следующим образом:

- низкая стоимость,

- высокая надежность,

- высокая степень миниатюризации,

- малое энергопотребление,

- работоспособность в жестких условиях эксплуатации;

- достаточная производительность для выполнения всех требуемых функций.

В отличие от универсальных компьютеров к управляющим контроллерам, как правило, не предъявляются высокие требования к производительности и программной совместимости.

|

|

|

Выполнение всех этих довольно противоречивых условий одновременно затруднительно, поэтому развитие и совершенствование техники пошло по пути специализации и в настоящее время количество различных моделей управляющих микроконтроллеров чрезвычайно велико.

Классификация и структура микроконтроллеров

В настоящее время выпускается целый ряд типов МК. Все эти приборы можно условно разделить на три основных класса:

- 8-разрядные МК для встраиваемых приложений;

- 16- и 32-разрядные МК;

- цифровые сигнальные процессоры (DSP).

Наиболее распространенным представителем семейства МК являются 8-разрядные приборы, широко используемые в промышленности, бытовой и компьютерной технике. Они прошли в своем развитии путь от простейших приборов с относительно слаборазвитой периферией до современных многофункциональных контроллеров, обеспечивающих реализацию сложных алгоритмов управления в реальном масштабе времени. Причиной жизнеспособности 8-разрядных МК является использование их для управления реальными объектами, где применяются, в основном, алгоритмы с преобладанием логических операций, скорость обработки которых практически не зависит от разрядности процессора.

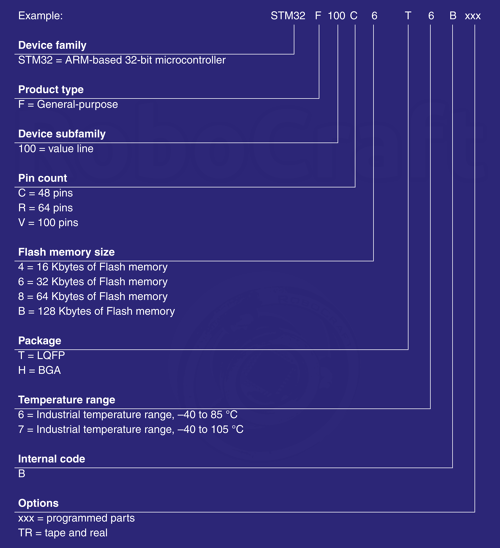

Схема именования моделей МК.

Росту популярности 8-разрядных МК способствует постоянное расширение номенклатуры изделий, выпускаемых такими известными фирмами, как Motorola, Microchip, Intel, Zilog, Atmel и многими другими. Современные 8-разрядные МК обладают, как правило, рядом отличительных признаков. Перечислим основные из них:

- модульная организация, при которой на базе одного процессорного ядра (центрального процессора) проектируется ряд (линейка) МК, различающихся объемом и типом памяти программ, объемом памяти данных, набором периферийных модулей, частотой синхронизации;

- использование закрытой архитектуры МК, которая характеризуется отсутствием линий магистралей адреса и данных на выводах корпуса МК. Таким образом, МК представляет собой законченную систему обработки данных, наращивание возможностей которой с использованием параллельных магистралей адреса и данных не предполагается;

- использование типовых функциональных периферийных модулей (таймеры, процессоры событий, контроллеры последовательных интерфейсов, аналого-цифровые преобразователи и др.), имеющих незначительные отличия в алгоритмах работы в МК различных производителей;

- расширение числа режимов работы периферийных модулей, которые задаются в процессе инициализации регистров специальных функций МК.

При модульном принципе построения все МК одного семейства содержат процессорное ядро, одинаковое для всех МК данного семейства, и изменяемый функциональный блок, который отличает МК разных моделей. Структура модульного МК приведена на рис.1.

Рис.1

Процессорное ядро включает в себя:

- центральный процессор;

- внутреннюю контроллерную магистраль (ВКМ) в составе шин адреса, данных и управления;

- схему синхронизации МК;

- схему управления режимами работы МК, включая поддержку режимов пониженного энергопотребления, начального запуска (сброса) и т.д.

Изменяемый функциональный блок включает в себя модули памяти различного типа и объема, порты ввода/вывода, модули тактовых генераторов (Г), таймеры. В относительно простых МК модуль обработки прерываний входит в состав процессорного ядра. В более сложных МК он представляет собой отдельный модуль с развитыми возможностями. В состав изменяемого функционального блока могут входить и такие дополнительные модули как компараторы напряжения, аналого-цифровые преобразователи (АЦП) и другие. Каждый модуль проектируется для работы в составе МК с учетом протокола ВКМ. Данный подход позволяет создавать разнообразные по структуре МК в пределах одного семейства.

Процессорное ядро микроконтроллера

Структура процессорного ядра МК

Основными характеристиками, определяющими производительность процессорного ядра МК, являются:

- набор регистров для хранения промежуточных данных;

- система команд процессора;

- способы адресации операндов в пространстве памяти;

- организация процессов выборки и исполнения команды.

С точки зрения системы команд и способов адресации операндов процессорное ядро современных 8-разрядных МК реализует один из двух принципов построения процессоров:

- процессоры с CISC-архитектурой, реализующие так называемую полную систему команд (Complicated Instruction Set Computer);

- процессоры с RISC-архитектурой, реализующие сокращенную систему команд (Reduced Instruction Set Computer).

CISC-процессоры выполняют большой набор команд с развитыми возможностями адресации, давая разработчику возможность выбрать наиболее подходящую команду для выполнения необходимой операции. В применении к 8-разрядным МК процессор с CISC-архитектурой может иметь однобайтовый, двухбайтовый и трехбайтовый (редко четырехбайтовый) формат команд. Время выполнения команды может составлять от 1 до 12 циклов. К МК с CISC-архитектурой относятся МК фирмы Intel с ядром MCS-51, которые поддерживаются в настоящее время целым рядом производителей, МК семейств НС05, НС08 и НС11 фирмы Motorola и ряд других.

В процессорах с RISC-архитектурой набор исполняемых команд сокращен до минимума.

RISC – все команды имеют одинаковую длину – одно слово, и выполняются за один машинный цикл. Производительность высокая. Объем кода программы – большой. Используется конвейер команд. Команда у RISC-процессора выполняется в несколько этапов с помощью одинаковой последовательности элементарных команд: выборка из памяти команды и операндов, дешифрация команды, выполнение команды, сохранение результата. Если каждая элементарная команда выполняется отдельным операционным устройством процессора, и все эти операционные устройства работают одновременно, то можно получать результат на каждом такте работы конвейера. Машинный цикл – время выполнения команды. Время выполнения элементарной команды – 1 такт работы CPU. Тактовая частота может не совпадать с частотой машинных циклов.

Для реализации более сложных операций приходится комбинировать команды. При этом все команды имеют формат фиксированной длины (например, 12, 14 или 16 бит), выборка команды из памяти и ее исполнение осуществляется за один цикл (такт) синхронизации. Система команд RISC-процессора предполагает возможность равноправного использования всех регистров процессора. Это обеспечивает дополнительную гибкость при выполнении ряда операций. К МК с RISC-процессором относятся МК AVR фирмы Atmel, МК PIC16 и PIC17 фирмы Microchip и другие.

На первый взгляд, МК с RISC-процессором должны иметь более высокую производительность по сравнению с CISC МК при одной и той же тактовой частоте внутренней магистрали. Однако на практике вопрос о производительности более сложен и неоднозначен.

С точки зрения организации процессов выборки и исполнения команды в современных 8-разрядных МК применяется одна из двух уже упоминавшихся архитектур МПС: фон-неймановская (принстонская) или гарвардская.

Основной особенностью фон-неймановской архитектуры является использование общей памяти для хранения программ и данных, как показано на рис.2.

Рис.2

Основное преимущество архитектуры Фон-Неймана – упрощение устройства МПС, так как реализуется обращение только к одной общей памяти. Кроме того, использование единой области памяти позволяло оперативно перераспределять ресурсы между областями программ и данных, что существенно повышало гибкость МПС с точки зрения разработчика программного обеспечения. Размещение стека в общей памяти облегчало доступ к его содержимому. Неслучайно поэтому фон-неймановская архитектура стала основной архитектурой универсальных компьютеров, включая персональные компьютеры.

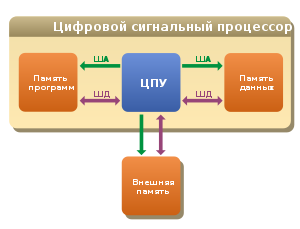

Основной особенностью гарвардской архитектуры является использование раздельных адресных пространств для хранения команд и данных, как показано на рис.3.

Рис.3

Гарвардская архитектура почти не использовалась до конца 70-х годов, пока производители МК не поняли, что она дает определенные преимущества разработчикам автономных систем управления.

Дело в том, что, судя по опыту использования МПС для управления различными объектами, для реализации большинства алгоритмов управления такие преимущества фон-неймановской архитектуры как гибкость и универсальность не имеют большого значения. Анализ реальных программ управления показал, что необходимый объем памяти данных МК, используемый для хранения промежуточных результатов, как правило, на порядок меньше требуемого объема памяти программ. В этих условиях использование единого адресного пространства приводило к увеличению формата команд за счет увеличения числа разрядов для адресации операндов. Применение отдельной небольшой по объему памяти данных способствовало сокращению длины команд и ускорению поиска информации в памяти данных.

Кроме того, гарвардская архитектура обеспечивает потенциально более высокую скорость выполнения программы по сравнению с фон-неймановской за счет возможности реализации параллельных операций. Выборка следующей команды может происходить одновременно с выполнением предыдущей, и нет необходимости останавливать процессор на время выборки команды. Этот метод реализации операций позволяет обеспечивать выполнение различных команд за одинаковое число тактов, что дает возможность более просто определить время выполнения циклов и критичных участков программы.

Рис.4 ЦСП на основе Гарвардской архитектуры

Объем адресуемой памяти определяется разрядностью шины адреса. Разрядность шины данных памяти программ совпадает с разрядностью команды CPU. Разрядность шины данных памяти данных совпадает с разрядностью данных CPU.

В микроконтроллерах используется три основных вида памяти – это память программ, память данных и регистры. Память программ представляет собой постоянную память (ПЗУ), предназначенную для хранения программного кода (команд). Ее содержание в ходе выполнения программы не изменяется. Память данных предназначена для хранения переменных в процессе выполнения программы. Регистры МК – этот вид памяти включает в себя внутренние регистры процессора и регистры, которые служат для управления периферийными устройствами (регистры специальных функций).

Памя ть программ

Основным свойством памяти программ является ее энергонезависимость, то есть возможность хранения программы при отсутствии питания. С момента появления МК технология энергонезависимых запоминающих устройств претерпела множество изменений, которые позволили не только повысить информационную емкость, быстродействие, надежность хранения информации, но и привели к появлению принципиально новых технологий программирования памяти МК. С точки зрения пользователей МК следует различать пять типов энергонезависимой памяти программ.

1. ПЗУ масочного типа – Mask ROM. Содержание ячеек ПЗУ этого типа заносится на заводе-изготовителе МК с помощью масок и не может быть заменено или «допрограммировано». Поэтому МК с такой памятью программ следует использовать только после достаточно длительной опытной эксплуатации. Основным недостатком данной памяти является необходимость значительных затрат на создание нового комплекта фотошаблонов и их внедрение в производство. Обычно такой процесс занимает 2 – 3 месяца и является экономически выгодным только при выпуске несколько десятков тысяч приборов. Достоинством ПЗУ масочного типа является высокая надежность хранения информации по причине программирования в заводских условиях с последующим контролем качества.

2. ПЗУ, однократно программируемые пользователем – OTPROM (One-Time Programmable ROM). В незапрограммированном состоянии каждая ячейка памяти однократно программируемого ПЗУ при считывании возвращает код FFh. Программированию подлежат только те разряды, которые должны содержать «0». Если в процессе программирования некоторые разряды какой-либо ячейки памяти были установлены в «0», то восстановить в этих разрядах единичное значение уже невозможно. Поэтому рассматриваемый тип памяти и носит название «однократно программируемые ПЗУ». Технология записи информации состоит в многократном приложении импульсов повышенного напряжения к элементарным ячейкам байта памяти (т.е. к битам), подлежащим программированию. МК с однократно программируемым ПЗУ рекомендуется использовать в изделиях, выпускаемых небольшими партиями.

3. ПЗУ, программируемые пользователем с ультрафиолетовым стиранием – EPROM (Erasable Programmable ROM). ПЗУ данного типа программируются электрическим сигналами и стираются с помощью ультрафиолетового облучения. Ячейка памяти EPROM представляет собой МОП-транзистор с «плавающим» затвором, заряд на который переносится с управляющего затвора при подаче на него высокого напряжения. При этом МОП-транзистор переключается в открытое состояние, и при обращении к ячейке считывается «0». Для стирания содержимого ячейки она облучается ультрафиолетовым светом, который сообщает заряду на плавающем затворе энергию, достаточную для преодоления потенциального барьера и стекания на подложку. Этот процесс может занимать от десятков секунд до нескольких минут. Число циклов стирания/программирования ПЗУ данного типа ограничено и составляет 15-25 раз. Обычно микросхемы EPROM выпускаются в керамическом корпусе с кварцевым окошком для доступа ультрафиолетового света. МК с ПЗУ данного типа имеют высокую стоимость, поэтому их рекомендуется использовать только в опытных образцах изделий.

4. ПЗУ, программируемые пользователем с электрическим стиранием – EEPROM (Electrically Erasable Programmable ROM). Электрически программируемые и электрически стираемые ПЗУ совместили в себе положительные качества рассмотренных выше типов памяти. Максимальное число циклов стирания/программирования ПЗУ типа EEPROM в составе МК обычно равно 100000. Эта память позволяет реализовать побайтное стирание и побайтное программирование. По цене ЕEPROM занимают среднее положение между OTPROM и EPROM. Основное преимущество использования ЕEPROM заключается в том, что можно многократно стирать и программировать МК, не снимая его с платы. Таким способом можно производить отладку и модернизацию программного обеспечения. Это дает огромный выигрыш на начальных стадиях разработки микроконтроллерных устройств или в процессе их изучения, когда много времени уходит на поиск причин программ. Несмотря на очевидные преимущества, только в редких моделях современных МК такая память используется для хранения программ. Связано это с тем, что во-первых, ПЗУ типа ЕEPROM имеют ограниченную емкость и могут использоваться в качестве резидентной памяти программ только в маловыводных МК с небольшим объемом памяти. Во-вторых, почти одновременно с ЕEPROM появились ПЗУ типа Flash, которые при сходных потребительских характеристиках имеют более низкую стоимость.

5. ПЗУ с электрическим стиранием типа Flash – Flash ROM. Электрически программируемые и электрически стираемые ПЗУ типа Flash функционально мало отличаются от ЕEPROM. Основное отличие состоит в способе стирания записанной информации. Для увеличения объема памяти транзистор адресации каждой элементарной ячейки был удален, что не дает возможности программировать каждый бит памяти отдельно. Память типа Flash стирается и программируется страницами или блоками. Страница, как правило, составляет 8, 16 или 32 байта памяти, блоки могут объединять некоторое число страниц, вплоть до полного объема резидентного ПЗУ МК. Если необходимо изменить содержимое одной ячейки Flash-памяти, потребуется перепрограммировать весь блок. Упрощение декодирующих схем, произошедшее из-за уменьшения числа транзисторов, и, как следствие, снижение стоимости и размеров привели к тому, что МК с Flash-памятью в настоящее время становятся конкурентоспособными не только по отношению к МК с однократно программируемыми ПЗУ, но и с масочными ПЗУ также.

Выше отмечалось, что ЕEPROM ПЗУ практически никогда не используется для хранения программ, но оно имеет режим побайтного программирования. Данное обстоятельство сделало ЕEPROM идеальным энергонезависимым запоминающим устройством для хранения изменяемых в процессе эксплуатации изделия настроек пользователя. В качестве примера достаточно вспомнить современный телевизор: настройки каналов сохраняются при отключении питания. Одной из тенденций совершенствования резидентной памяти 8-разрядных МК стала интеграция на кристалл МК сразу двух моделей энергонезависимой памяти: OTPROM или Flash ROM – для хранения программ и EЕPROM – для хранения перепрограммируемых констант.

Память данных

Память данных (ПД) микроконтроллеров предназначена для хранения промежуточных данных в ходе выполнения программы. В современных микроконтроллерах память данных подразделяется по выполняемым функция и способу реализации на два вида:

1) оперативная память – ОЗУ;

2) память хранения данных в EEPROM.

Оперативная память (англоязычный термин RAM) является ОЗУ статического типа, так как ячейки ее выполняются на основе триггеров. Эта память энергозависима, так как ее содержимое теряется при выключении электропитания. Достоинством статического ОЗУ является высокое быстродействие, простота управления памятью. Однако такое ОЗУ имеет существенные недостатки: большое энергопотребление и большое количество активных компонентов (транзисторов), необходимых для ее реализации. Объем оперативной памяти данных МК, как правило, невелик и составляет обычно десятки или сотни байт.

Второй вид ПД – это память хранения данных в EEPROM. Эту память можно использовать для данных, которые необходимо сохранить при выключении электропитания, а также неоперативных данных. Неоперативными данными могут быть настроечные параметры, изменяемые константы. Объем памяти хранения данных небольшой и обычно составляет несколько десятков байт. Эту память нельзя использовать в качестве оперативной. Во-первых, она является очень «медленной». Так время записи в ее ячейку составляет несколько миллисекунд. Во-вторых, она имеет ограниченное количество циклов записи-стирания.

Большинство современных микроконтроллеров имеют Гарвардскую архитектуру и содержат 3 вида памяти:

· память программ FLASH;

· оперативная память (ОЗУ) SRAM (Static RAM);

· энергонезависимая память данных EEPROM.

Адресные пространства указанных видов памяти, как правило, разделены. Способы адресации и доступа к этим областям памяти также различны. Такая структура позволяет центральному процессору работать одновременно как с памятью программ, так и с памятью данных, что существенно увеличивает производительность. Каждая из областей памяти данных (SRAM и EEPROM) также расположена в своем адресном пространстве.

Память программ

Память программ представляет собой электрически стираемое ППЗУ (FLASH) и может поддерживать команды с разрядностью больше 8 бит. В некоторых микроконтроллерах память программ разделена на 2 секции:

· секцию загрузчика (Boot Program);

· секцию прикладных программ (Application Program).

Память программ чаще всего является электрически перепрограммируемой, количество циклов перезаписи превышает 10 тысяч.

Большинство микроконтроллеров поддерживают внутрисхемное программирование, т. е. загрузку программы в микроконтроллер можно осуществлять после монтажа на плату посредством специального разъема программирования.

Для адресации памяти программ используется счетчик команд (Program Counter – PC).

В памяти программ также находится вектор сброса — в момент подачи питания микроконтроллер начинает выполнение программы с этого адреса, и здесь размещается команда перехода к началу исполняемой программы. Кроме того, память программ содержит таблицу векторов прерываний. При возникновении прерывания после сохранения в стеке текущего значения счетчика команд происходит выполнение команды, расположенной по адресу соответствующего вектора. Поэтому по данным адресам располагаются команды перехода к подпрограммам обработки прерываний.

Положение вектора сброса и таблицы векторов прерываний может быть перенесено из секции прикладных программ в секцию загрузчика.

В некоторых случаях память программ может использоваться не только для хранения кода программы, но и для хранения различных констант.

Оперативная память

Оперативная память, как правило, содержит 3 области:

· регистры общего назначения;

· служебные регистры;

· память для хранения данных.

Регистры общего назначения (РОН) находятся в непосредственной близости к АЛУ. Однако в микроконтроллерах некоторых фирм (в частности, PIC фирмы Microchip) имеется только один рабочий регистр, играющий роль одного из операндов в командах.

Применение набора регистров общего назначения в сочетании с конвейерной обработкой позволяет АЛУ выполнять одну операцию (извлечение операндов из набора регистров, выполнение команды и запись результата обратно в регистр) за один такт.

Служебные регистры имеют свои имя, адрес и назначение. Они предназначены для конфигурации и обслуживания периферийных узлов микроконтроллера. Краткая характеристика служебных регистров должна быть приведена в руководстве по использованию микроконтроллера (Data Sheet).

Среди служебных регистров есть, как правило, один регистр, используемый наиболее часто в процессе выполнения программ. Это регистр состояния. Он содержит набор флагов, показывающих текущее состояние микроконтроллера. Большинство флагов автоматически устанавливаются в «1» или сбрасываются в «0» при наступлении определенных событий (в соответствии с результатом выполнения команд). Все биты этого регистра доступны как для чтения, так и для записи. Эта информация анализируется при выполнении условных переходов. При возникновении прерываний содержимое регистра состояния необходимо сохранять программно (чаще всего это является «заботой» компилятора).

Остальная часть оперативной памяти предназначена для хранения пользовательских данных.

Дата добавления: 2020-01-07; просмотров: 455; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!