Специальные типы регистров защищенного режима МП ( IA -32): управляющие, отладки, системные адресные регистры. Селекторы сегментов: - организация в разных режимах.

По сравнению с реальным режимом МП IA-16 в защищенном режиме МП IA-32 регистровый файл увеличился до 32 регистров. К регистрам пользователей (16) добавились системные регистры (16).

Регистры пользователей:

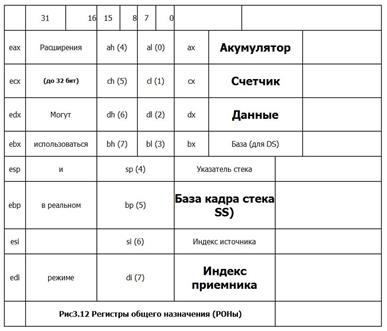

регистры общего назначения (РОНы) 8 регистров по 32 бита,

указатель команд 1 регистр – 32 бита,

регистр состояния (флагов) 1 регистр – 32 бита

сегментные регистры 6 регистров по 16 бит,

В состав системных регистров входят:

регистры системных адресов 4 регистра,

регистры управления, отладки и тестирования 16 регистров.

В защищенном режиме команды межсегментных переходов содержат полный указатель CS (сегмента) и IP (адрес команды в сегменте – offset). Указатель CS, в свою очередь, может указывать на:

- дескриптор сегмента,

- шлюз дескриптора сегмента,

- дескриптор TSS,

- дескриптор шлюза TSS.

Все зависит от выбора стратегии разработчиков ОС.

В первых двух случаях реализуется процедура передачи управления:

прямой передачи управления (без изменения уровней привилегий) или

через шлюз (с возможностью увеличения уровня привилегий, но по командам, предусматривающим возвращение, – например Call).

В двух последних случаях реализуется процедура переключения задач:

прямого переключения задач, если селектор указывает на дескриптор задачи (используется при переключениях задач на одном уровне привилегий),

|

|

|

косвенного переключения задач, если селектор указывает на шлюз задачи (используется при переключениях с изменениями уровня привилегий).

Как и в МП IA-16 с точки зрения использования регистров они не являются классическими регистрами общего назначения. Они могут задаваться по умолчанию (кодом операции, постбайтом и т.д.) По использованию регистров по умолчанию, они делятся на две группы :

регистры данных – eax, ecx, edx и ebx (по возрастанию адресов),

регистры адресов – esp, ebp, esi и edi (по возрастанию адресов)

Регистр ebx, хотя и относят к группе регистров данных, но он же является одним из регистров адреса базы сегмента данных.

При работе с 16-ти битовыми операндами и компонентами адреса используются 16- битовые РОНы – ax, cx, dx, bx, sp, bp, si и di (по возрастанию адресов).

При работе с байтовыми операндами используются 8 – битовые РОНы: al, cl, dl, bl, ah, ch, dh и bh (по возрастанию адресов).

В защищенном режиме по отношению к их содержимому (данные, компоненты адреса) регистры стали более симметричными.

Режим адресации операндов в команде определяется кодом операции, постбайтом и байтом SIB. Режим адресации определяет местонахождение компонент и алгоритм вычисления адреса операнда в памяти.

|

|

|

В защищенном режиме МП IA –32 используются следующие виды адресаций:

непосредственная (константа) MOV еax, 0002h,

прямая (#d – смещение) MOV еbx, [0002h],

регистровая (любой РОН, кроме ebp) MOV еbx, еах,

косвенная регистровая MOV еах, [еbx],

базовая со смещением MOV еах, [еbx+001Ah],

базовая индексная без смещением MOV еах, [еbp+esi*8],

базовая индексная со смещением MOV еах, [еbp+esi*8+1Ah],

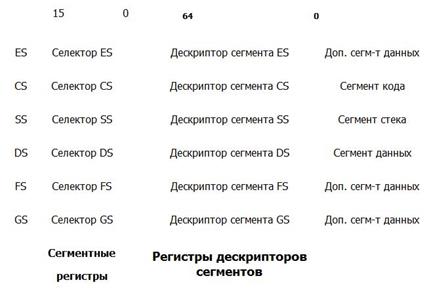

Изменилось и содержимое сегментных регистров. В МП IA-16 сегментные регистры содержат базовые адреса сегментов, а в МП IA 32 – селекторы сегментов.

Сегментные регистры в защищенном режиме дополняются 64-х разрядными регистрами дескрипторов сегментов. В системе не предусмотрены ни одной команды прямого обращения к ним. В этом смысле они программно невидимы. Это регистры аппаратных средств системы защиты программ от взаимных помех.

Назначение сегментных регистров в защищенном режиме остались прежними: использование в процедуре трансляции адресов, но сама функция и содержимое этих регистров существенно изменились.

|

|

|

Селекторы сегментов в защищенном режиме МП IA 32 – это указатели номера строки таблиц дескрипторов, в которых находятся заданные дескрипторы. Преобразование логического адреса в линейный (адрес плоской памяти) производится процедурой трансляции сегмента.

МП содержит 6 шестнадцати битных сегментных регистров:

ES – дополнительного сегмента данных,

CS – сегмента кода,

SS – сегмента стека,

DS – сегмента данных,

FS – дополнительного сегмента данных,

GS – дополнительного сегмента данных.

Использование регистров CS, SS, DS и ES принято по умолчанию. Для использования регистров FS и GS необходима явная ссылка на них в префиксе замены сегментов. Использование сегментных регистров зависит от режима работы МП.

- Регистровая (локальная) память МП. Сверхбыстрая буферная память. Внешний и внутренний кэш: - алгоритмы обслуживания. Стековая (магазинная) память. FIFO - буфера.

Регистровая КЭШ-память - высокоскоростная память сравнительно большой емкости, являющаяся буфером между ОП и МП и позволяющая увеличить скорость выполнения операций. Создавать ее целесообразно в ПК с тактовой частотой задающего генератора 40 МГц и более. Регистры КЭШ-памяти недоступны для пользователя, отсюда и название КЭШ (Cache), в переводе с английского означает "тайник".

|

|

|

В КЭШ-памяти хранятся данные, которые МП получил и будет использовать в ближайшие такты своей работы. Быстрый доступ к этим данным и позволяет сократить время выполнения очередных команд программы. При выполнении программы данные, считанные из ОП с небольшим опережением, записываются в КЭШ-память.

Микропроцессоры начиная от МП 80486 имеют свою встроенную КЭШ-память (или КЭШ-память 1-го уровня), чем, в частности, и обусловливается их высокая производительность. Микропроцессоры Pentium и Pentium Pro имеют КЭШ-память отдельно для данных и отдельно для команд, причем если у Pentium емкость этой памяти небольшая - по 8 Кбайт, то у Pentium Pro она достигает 256 - 512 Кбайт.

Следует иметь в виду, что для всех МП может использоваться дополнительная КЭШ-память(КЭШ-память 2-го уровня), размещаемая на материнской плате вне МП, емкость которой может достигать нескольких мегабайтов.

Примечание. Оперативная память может строитьсяна микросхемах динамического (Dinamic Random Access Memory - DRAM) или статического (Static Random Access Memory - SRAM) типа. Статический тип памяти обладает существенно более высокимбыстродействием, но значительно дороже динамического, Для регистровой памяти(МПП и КЭШ-память) используются SRAM, а ОЗУ основной памяти строится на базе DRAM-микросхем.

Кэш-память — сверхбыстрая буферная память процессора, в которой хранятся часто используемые фрагменты программ и данные. В новых ПК интегрируется на кристалл процессора.

Быстрая буферная память

В результате такого параллелизма ускоряется обработка потока инструкций. Адреса операндов вычисляются с помощью специализированного арифметического устройства. Код операции (самый левый байт каждой инструкции) посылается к БМУ, где он непосредственно адресует так называемую векторную память, содержащую начальные адреса микропрограмм, управляющих выполнением конкретных инструкций.

Выборку инструкций ускоряет быстрая буферная память (ББП) инструкций емкостью 16 Кбайт, которая управляется непосредственно БВИ. Для адресации этой памяти используется реальный адрес инструкции. Преобразование виртуальных адресов в реальные — тоже функция БВИ, она выполняется аппаратно с помощью буфера быстрого преобразования (TLB). Когда выбираемая инструкция или часть инструкции отсутствует в буферной памяти инструкций, выполняется микропрограммное прерывание, и из оперативной памяти выбирается блок размером 64 байта (называемый «линией»), содержащий требуемую инструкцию.

Блок выборки операндов работает под микропрограммным управлением. Его основная функция — обеспечивать данные, необходимые для обработки, выполняемой в БАЛУ. Блок БВО осуществляет также связь с системной магистралью процессора. В его состав входит быстрая буферная память данных емкостью 16 Кбайт, разделенная логически на два массива по 8 Кбайт. Каждый из этих массивов организован как 128 линий по 64 байта, (или по 16 слов в линии). Линии ББП являются копиями определенных линий из оперативной памяти с адресами, зависящими от потребностей программы, поэтому в БВО (как и в БВИ, для буферной памяти инструкций) используются адресные таблицы, содержащие старшие части адресов линий ББП. Адресные таблицы устанавливают соответствие между информацией в линиях ББП и в конкретных линиях оперативной памяти.

Внутренне кэширование обращений к памяти применяется в процессорах, начиная с 486-го. С кэшированием связаны новые функции процессоров, биты регистров и внешние сигналы.

Процессоры 486 и Pentium имеют внутренний кэш первого уровня, в Pentium Pro и Pentium II имеется и вторичный кэш. Процессоры могут иметь как единый кэш инструкций и данных, так и общий. Выделенный кэш инструкций обычно используется только для чтения. Для внутреннего кэша обычно используется наборно-ассоциативная архитектура.

Алгоритм:

Любой внутренний запрос процессора на обращение к памяти направляется на внутренний кэш. Теги четырех строк набора, который обслуживает данный адрес, сравниваются со старшими битами запрошенного физического адреса. Если адресуемая область представлена в строке кэш-памяти (случая попадания –cache hit), запрос на чтение обслуживается только кэш-памятью, не выходя на внешнюю шину. Запрос на запись модифицирует данную строку, и в зависимости от политики записи либо сразу выходит на внешнюю шину (при сквозной записи), либо несколько позже (при использовании алгоритма обратной записи).

Альтернативой, широко применяемой в настоящее время, является вторая (внешняя) кэш-память большего объема, расположенная между внутренней кэш-памятью и ОП. В этой двухуровневой системе кэш-памяти, внутренней памяти отводится роль первого уровня L1, а внешней - второго L2. емкость L2 обычно на порядок и более выше, чем L1, а быстродействие и стоимость ниже. Память второго уровня также строится обычно как статическое ОЗУ. Емкость ее может составлять от 256 Кбайт до 1 Мбайта и технически реализуется как в виде отдельной микросхемы, однако может размещаться и на одном кристалле с процессором.

Алгоритм:

При доступе к памяти, ЦП сначала обращается к кэш-памяти первого уровня. При промахе производится обращение к кэш-памяти второго уровня. Если информация отсутствует и в L2, производится обращение к ОП, и соответствующий блок заносится сначала в L2, а затем и в L1. Благодаря такой процедуре, часто запрашиваемая информация может быть легко восстановлена из кэш-памяти второго уровня.

Магазинная (стековая) память организуется по принципу “Последний пришел, первый вышел” (LIFO- Last In First Out), или “Первый пришел, первый вышел” (FIFO- First In First Out).

|

Отличительным свойством памяти FIFO является наличие отдельного порта для чтения и отдельного — для записи данных. Благодаря наличию указателей и двухпортовой структуре памяти FIFO, стробы считывания и записи данных могут поступать на одноименные входы микросхемы в произвольном порядке. И если в памяти RAM операции чтения и записи данных выполняются строго последовательно во времени, то в памяти FIFO допускается выполнение записи и считывания в независимых друг от друга асинхронных режимах.

Недостатком FIFO является то, что содержимое уже прочитанной ячейки памяти может быть автоматически замещено новым значением, тогда как в RAM или ROM содержимое ячеек может быть изменено только путем непосредственной адресации и записи в них новых значений. Для предотвращения непредусмотренной потери данных в состав микросхем памяти FIFO введены флаги заполненности. В процессе функционирования память FIFO может находиться в одном из следующих возможных состояний: «нормальная работа», «буфер пуст», «буфер почти пуст», «буфер заполнен на 1/2 от максимального размера пространства памяти», «буфер почти полон», «буфер полон». Флаги заполненности являются индикаторами этих состояний и позволяют внешним устройствам осуществлять гибкий контроль над потоками считываемых или записываемых данных. С целью обеспечения помехоустойчивой передачи данных в канале связи, в состав большинства современных микросхем памяти FIFO добавлена функция повторного считывания данных из буфера, начиная с первого слова. Расширением этой функции является возможность повторного считывания произвольного сегмента памяти путем пользовательской установки указателя начала записи.

Дата добавления: 2020-01-07; просмотров: 254; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!