Лекция 7 Физическая и логическая организация адресного пространства

Цели лекции:

1. Изучение механизмов формирования физического адреса

2. Различная организация логического адресного пространства.

Логическое адресное пространство (ЛАП)

Для адресации операндов в физическом адресном пространстве программы используют логическую адресацию. Процессор автоматически транслирует логические адреса в физические, выдаваемые затем на системную шину.

Архитектура компьютера различает физическое адресное пространство (ФАП) и логическое адресное пространство (ЛАП).

Физическое адресное пространство представляет собой простой одномерный массив байтов, доступ к которому реализуется аппаратурой памяти по адресу, присутствующему на шине адреса микропроцессорной системы. Логическое адресное пространство организуется самим программистом исходя из конкретных потребностей. Трансляцию логических адресов в физические осуществляет блок управления памятью MMU.

В архитектуре современных микропроцессоров ЛАП представляется в виде набора элементарных структур: байтов, сегментов и страниц. В микропроцессорах используются следующие варианты организации логического адресного пространства:

- плоское (линейное) ЛАП: состоит из массива байтов, не имеющего определенной структуры; трансляция адреса не требуется, так как логический адрес совпадает с физическим;

- сегментированное ЛАП: состоит из сегментов - непрерывных областей памяти, содержащих в общем случае переменное число

§ байтов; логический адрес содержит 2 части: идентификатор сегмента и смещение внутри сегмента; трансляцию адреса проводит блок сегментации MMU;

- страничное ЛАП: состоит из страниц - непрерывных областей памяти, каждая из которых содержит фиксированное число байтов. Логический адрес состоит из номера (идентификатора) страницы и смещения внутри страницы; трансляция логического адреса в физический проводится блоком страничного преобразования MMU;

- сегментно-страничное ЛАП: состоит из сегментов, которые, в свою очередь, состоят из страниц; логический адрес состоит из идентификатора сегмента и смещения внутри сегмента. Блок сегментного преобразования MMU проводит трансляцию логического адреса в номер страницы и смещение в ней, которые затем транслируются в физический адрес блоком страничного преобразования MMU.

Таким образом, основой получения физического адреса памяти служит логический адрес. В какой-то степени логическое адресное пространство, с которым имеет дело программист, можно сравнить со структурой книги, где аналогом сегмента выступает рассказ, страница книги соответствует странице ЛАП, а искомая информация - это некоторое слово. При этом если память организована как линейная, то номер искомого слова задается в явном виде и просто отсчитывается от начала книги. При сегментном представлении памяти искомое слово определяется его номером в заданном рассказе. Страничное представление памяти предполагает задание информации о слове в виде номера страницы в книге и номера слова на указанной странице. При сегментно-страничном представлении логический адрес слова задается номером слова в определенном рассказе. В этом случае по оглавлению книги определяется номер страницы, с которой начинается указанный рассказ. Затем, зная количество слов на странице и положение слова в рассказе, можно вычислить страницу книги и положение искомого слова на этой странице.

Формирование физического адреса в универсальном микропроцессоре при различных режимах работы

При работе в реальном режиме возможности процессора ограничены: емкость адресуемой памяти составляет 1 Мбайт, отсутствует страничная организация памяти, сегменты имеют фиксированную длину 2 байт.

Этот режим обычно используется на начальном этапе загрузки компьютера для перехода в защищенный режим.

В реальном режиме сегментные регистры процессора содержат старшие 16 бит физического адреса начала сегмента. Сдвинутый на 4 разряда влево селектор дает 20-разрядный базовый адрес сегмента. Физический адрес получается путем сложения этого адреса с 16-разрядным значением смещения в сегменте, формируемого по заданному режиму адресации для операнда или извлекаемому из регистра EIP для команды, как показано на рисунке 7.1. По полученному адресу происходит выборка информации из памяти.

Рисунок 7.1 – Схема получения физического адреса

Наиболее полно возможности микропроцессора по адресации памяти реализуются при работе в защищенном режиме. Объем адресуемой памяти увеличивается до 4 Гбайт, появляется возможность страничного режима адресации. Сегменты могут иметь переменную длину от одного байта до 4 Гбайт.

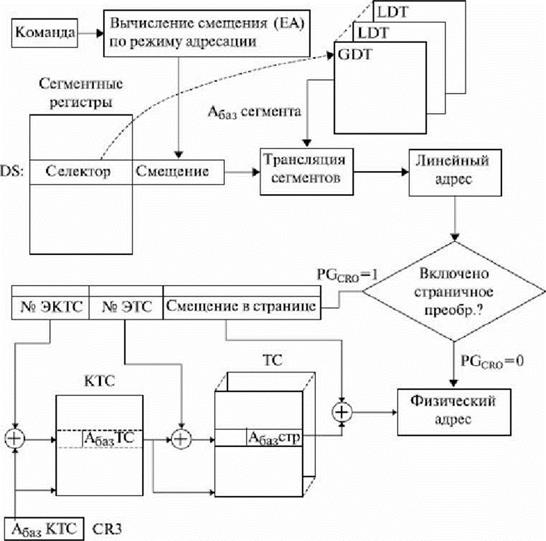

Общая схема формирования физического адреса микропроцессором, работающим в защищенном режиме, представлена на рисунке 7.2.

Рисунок 7.2 - Формирование физического адреса при сегментно-страничной организации памяти

Основой формирования физического адреса служит логический адрес. Он состоит из двух частей: селектора и смещения в сегменте.

Селектор содержится в сегментном регистре микропроцессора и позволяет найти описание сегмента (дескриптор) в специальной таблице дескрипторов. Дескрипторы сегментов хранятся в специальных системных объектах глобальной (GDT) и локальных (LDT) таблицах дескрипторов. Дескриптор играет очень важную роль в функционировании микропроцессора, от формирования физического адреса при различной организации адресного пространства и до организации мультипрограммного режима работы.

Сегменты микропроцессора, работающего в защищенном режиме, характеризуются большим количеством параметров. Поэтому в универсальных 32‑разрядных микропроцессорах информация о сегменте хранится в специальной 8‑байтной структуре данных, называемой дескриптором, а за сегментными регистрами закреплена основная функция определение местоположения дескриптора.

Структура дескриптора сегмента представлена на рисунке 7.3.

Рисунок 7.3 – Структура дескриптора сегмента

32-разрядное поле базового адреса позволяет определить начальный адрес сегмента в любой точке адресного пространства в 2 байт (4 Гбайт).

Поле предела (limit) указывает длину сегмента (точнее, длину сегмента минус единицу: если в этом поле записан 0, то это означает, что сегмент имеет длину один) в адресуемых единицах, то есть максимальный размер сегмента равен 220 элементов.

Величина элемента определяется одним из атрибутов дескриптора битом G:

|

|

Таким образом, сегмент может иметь размер с точностью до 1 байта в диапазоне от 1 байта до 1 Мбайт (при G = 0 ). При объеме страницы в 4 Кбайт можно задать объем сегмента до 4 Гбайт (при G = 1 ):

|

|

Бит размерности ( Default size ) определяет длину адресов и операндов, используемых в команде по умолчанию:

|

|

Этот бит доступен только программам, работающим на высшем уровне привилегий. Микропроцессор в своей работе его не меняет и не использует.

Запись в сегмент кода запрещена. При любой попытке записи возникает программное прерывание.

В сегменте данных:

- ED (Expand Down) - бит направления расширения. При ED = 1 этот сегмент является сегментом стека и смещение в сегменте должно быть больше размера сегмента. При ED = 0 - это сегмент собственно данных (смещение должно быть меньше или равно размеру сегмента);

- бит разрешения записи W (Writeable) . При W = 1 разрешено изменение сегмента. При W = 0 запись в сегмент запрещена, при попытке записи в сегмент возникает программное прерывание.

В случае обращения за операндом смещение в сегменте формируется микропроцессором по режиму адресации операнда, заданному в команде. Смещение в сегменте кода извлекается из регистра - указателя команд EIP.

Сумма извлеченного из дескриптора начального адреса сегмента и сформированного смещения в сегменте дает линейный адрес (ЛА).

Если в микропроцессоре используется только сегментное представление адресного пространства, то полученный линейный адрес является также и физическим.

Если помимо сегментного используется и страничный механизм организации памяти, то линейный адрес представляется в виде двух полей: старшие разряды содержат номер виртуальной страницы, а младшие смещение в странице. Преобразование номера виртуальной страницы в номер физической проводится с помощью специальных системных таблиц: каталога таблиц страниц (КТС) и таблиц страниц (ТС). Положение каталога таблиц страниц в памяти определяется системным регистром CR3.

Физический адрес вычисляется как сумма полученного из таблицы страниц адреса физической страницы и смещения в странице, полученного из линейного адреса.

Дата добавления: 2019-09-13; просмотров: 564; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!