ПРОЕКТИРОВАНИЕ ОПЕРАЦИОННОГО АВТОМАТА

1) Список операций:

y1: A(2n-1:0):=D1(2n-1:0)

y2: B(n:0):= D2(n-1:0).0

y3: TgS:= A(2n-1)

y4: B(n:0):=R1(B(n).B(n:1))

y5: A(2n-1:n-1):=A(2n-1:n-1)+B(n:0)+1

y6: A(2n-1:n-1):=A(2n-1:n-1)+B(n:0)

y7: C(n-1:0):=0

y8: CnT(m-1:0):=n

y9: C(n-1:0):=L1(C(n-1:0).1)

y10: C(n-1:0):=L1(C(n-1:0).0)

y11: CnT:=CnT-1

y12: A:=L1(A.0)

y12: A:=L1(A.0)

y13: A:=A+B+1

y14: A:=A+B

y15: C(n-1:0):=C(n-1:0)+1

y16: R(2n-1:0):=0000000.C(n-1:0)

y17: IRQ1:=1

y18: IRQ2:=1

y19: A(2n-1:0):=0.D1(n-1 :0)

y20: B(n:0):=0.D2

y21: C(n-1:0):=C(n-1:0)+A(n-1:0)

y22: B(n-1:0):=R1(C(0).B(n-1:1))

y23: C(n-1:0):=R1(CF.C(n-1:1))

y24: R(2n-1:0):=C(n-1:0).B(n-1:0)

x1: F=1

x2: B=0

x3: A(2n-1) ÅB(n)

x4: CnT=0

x5: A(2n-1)ÅTgS

x6: B(n)

x7: f3=B(n) ÅTgS

x8: TgS

x9: A=0

x10: B(0)

2) A(2n-1:0), B(n:0), C(n-1), CnT(m-1:0), TgS, R(2n-1:0), IRQ1,IRQ2

3) YA = {y1, y5, y6, y12, y13, y14, y19};

YB = {y2, y4, y20, y22} ;

YC = {y7, y9, y10, y15, y21, y23} ;

YCnT = {y8, y11} ;

YTgS = {y3} ;

YR = {y16, y24} ;

YIRQ1 = {y17} ;

YIRQ2 = {y18}

4) KA1 = {y1, y19} ; KA2 = {y5,y6} ; KA3 = {y13, y14} ; KB1 = {y2, y20} ;

KB2 ={y4,y22} ; KC1 = {y9, y10} ; KC2 = {y15,y21}

5)

A:= F1, где

A:= F1, где

А:= A+F2+F3, где

А:= A+F2+F3, где

B:= F4, где

B:= F4, где

B:= R1(F5.B(n:1)), где

B:= R1(F5.B(n:1)), где

C:= L1(C.F6), где

C:= L1(C.F6), где

С:= C+F7, где

С:= C+F7, где

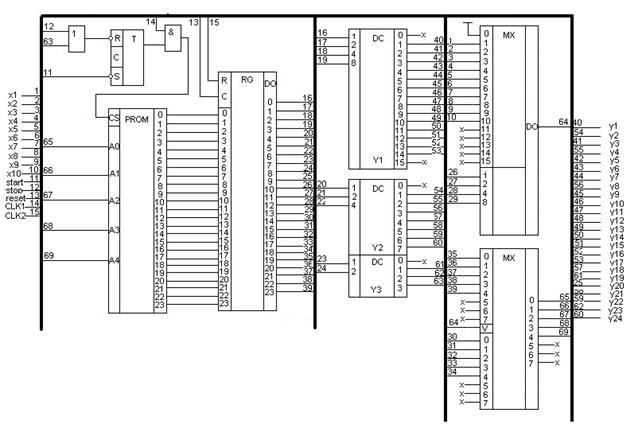

Рис. 2.1 – Структурная схема операционного автомата I

ПРОЕКТИРОВАНИЕ УПРАВЛЯЮЩЕГО АВТОМАТА

Рис. 3.1 – Размеченная ГСА для П-автомата с принудительной адресацией

1) Таблица 3.1 - Матрица совместимости S

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 2 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 3 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 4 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 5 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 6 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 7 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 8 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 9 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 10 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 11 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 12 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 13 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 14 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 15 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 16 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 17 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 18 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 19 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 20 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 21 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 22 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 23 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 24 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

2) Нахождение матрицы включения:

Таблица 3.2 - Матрица включения R

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | |

| 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | Y1 |

| 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | Y2 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | Y3 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | Y4 |

|

|

|

Рис. 3.2 – Структура микрокоманды

3) Таблица 3.3 - Кодирование микроопераций

| Y1 | K(Y1) | Y2 | K(Y2) | Y3 | K(Y3) | X | K(X) |

| y1 | 0001 | y2 | 001 | y19 | 01 | x1 | 0001 |

| y3 | 0010 | y4 | 010 | y23 | 10 | x2 | 0010 |

| y5 | 0011 | y8 | 011 | yF | 11 | x3 | 0011 |

| y6 | 0100 | y18 | 100 | x4 | 0100 | ||

| y7 | 0101 | y21 | 101 | x5 | 0101 | ||

| y9 | 0110 | y22 | 110 | x6 | 0110 | ||

| y10 | 0111 | y24 | 111 | x7 | 0111 | ||

| y11 | 1000 | x8 | 1000 | ||||

| y12 | 1001 | x9 | 1001 | ||||

| y13 | 1010 | x10 | 1010 | ||||

| y14 | 1011 | ||||||

| y15 | 1100 | ||||||

| y16 | 1101 | ||||||

| y17 | 1110 |

4) Таблица 3.4 - Карта программирования памяти

| Y1 | Y2 | Y3 | Y4 | X | A0 | A1 | |

| 0 | 0000 | 000 | 00 | 0 | 0001 | 00001 | 11010 |

| 1 | 0001 | 001 | 00 | 0 | 0010 | 00010 | 00011 |

| 2 | 0010 | 010 | 00 | 0 | 0011 | 00100 | 00101 |

| 3 | 0000 | 000 | 00 | 0 | 0000 | 00000 | 00000 |

| 4 | 0011 | 000 | 00 | 0 | 0011 | 00110 | 11111 |

| 5 | 0100 | 000 | 00 | 0 | 0011 | 00110 | 11111 |

| 6 | 0101 | 011 | 00 | 0 | 0011 | 00111 | 01000 |

| 7 | 0110 | 000 | 00 | 0 | 0000 | 01001 | 01001 |

| 8 | 0111 | 000 | 00 | 0 | 0000 | 01001 | 01001 |

| 9 | 1000 | 000 | 00 | 0 | 0100 | 01010 | 01111 |

| 10 | 0000 | 000 | 00 | 0 | 0011 | 01011 | 01100 |

| 11 | 1001 | 000 | 00 | 0 | 0000 | 01101 | 01101 |

| 12 | 1001 | 000 | 00 | 0 | 0000 | 01110 | 01110 |

| 13 | 1010 | 000 | 00 | 0 | 0011 | 00111 | 01000 |

| 14 | 1011 | 000 | 00 | 0 | 0011 | 00111 | 01000 |

| 15 | 0000 | 000 | 00 | 0 | 0101 | 10000 | 10001 |

| 16 | 0000 | 000 | 00 | 0 | 0111 | 10100 | 11000 |

| 17 | 0000 | 000 | 00 | 0 | 0110 | 10010 | 10011 |

| 18 | 1011 | 000 | 00 | 0 | 0000 | 10000 | 10000 |

| 19 | 1010 | 000 | 00 | 0 | 0000 | 10000 | 10000 |

| 20 | 0000 | 000 | 00 | 0 | 1000 | 00000 | 10101 |

| 21 | 0000 | 000 | 00 | 0 | 1001 | 00000 | 10110 |

| 22 | 1100 | 000 | 00 | 0 | 0000 | 10111 | 10111 |

| 23 | 1101 | 000 | 00 | 0 | 0000 | 00000 | 00000 |

| 24 | 0000 | 000 | 00 | 0 | 1000 | 10110 | 11001 |

| 25 | 0000 | 000 | 00 | 0 | 1001 | 10110 | 00000 |

| 26 | 0101 | 011 | 01 | 1 | 1010 | 11100 | 11011 |

| 27 | 0000 | 101 | 00 | 0 | 0000 | 11100 | 11100 |

| 28 | 1000 | 110 | 10 | 0 | 0100 | 11101 | 11110 |

| 29 | 0000 | 000 | 00 | 0 | 1010 | 11100 | 11011 |

| 30 | 0000 | 111 | 00 | 0 | 0000 | 00000 | 00000 |

| 31 | 0000 | 000 | 00 | 0 | 0000 | 00000 | 00000 |

Рис. 3.3 - Структурная схема управляющего автомата

ПРОЕКТИРОВАНИЕ ПРОЦЕССОРНОГО МОДУЛЯ

4.1 Схема объединения операционного и управляющего автоматов

Рис. 4.1 – Схема объединения операционного и управляющего автоматов

4.2 Результаты тестирования

Рис. 4.2.1 – Результат умножения двух беззнаковых чисел

Рис. 4.2.2 – Результат деления знаковых чисел без восстановления остатка

ВЫВОД

Данный курсовой проект разработан для изучения современных средств проектирования цифровых вычислительных машин. В этом проекте был разработан двухуровневый процессорный модуль, который был спроектирован на основе управляющего автомата типа П с принудительной адресацией и операционного автомата класса I. С помощью данного устройства можно выполнять такие микрооперации, как сложение, умножение и деление двоичных знаковых и беззнаковых чисел. П-автомат является автоматом с программируемой логикой. Для таких автоматов затраты оборудование больше (при несложных микрокомандах), чем в автоматах с жесткой логикой. Чем сложнее микропрограмма, тем меньше аппаратные затраты.

Управляющие автоматы и автоматы с жесткой логикой отличаются степенью гибкости. Для автоматов с жесткой логикой, при возникновении ошибки в микропрограмме, необходимо перестраивать структуру автомата. Программируемая логика позволяет решить задачу перестройки структуры относительно просто – путем прошивки в ПЗУ дополнительных микрокоманд, изменяемых при внесении изменений в микропрограмму. Таким образом, можно считать, что гибкостью обладают только автоматы с программируемой логикой.

СПИСОК ИСПОЛЬЗУЕМЫХ ИСТОЧНИКОВ

1. Майоров С.А., Новиков Г.И., Структура электронных вычислительных машин. - Л.: Машиностроение. Ленингр. Отделение, 1979. -

384 с., ил.

2. Баранов С.И., Скляров В. А., Цифровые устройства на программируемых БИС с матричной структурой. - М.: Радио и связь,

3.

1986. - 272 с, ил.

3. Угрюмов Е.П., Проектирование элементов и узлов ЭВМ: Учеб.

Пособие для спец. ЭВМ вузов. - М.: Высш. шк., 1987. - 318 с, ил.

4. ДСТУ 3008-95. «Звіти у сфері науки і техніки. Структура та

правила оформлення».

ПРИЛОЖЕНИЕ А

Листинг программы

---------------

-- unit . vhd

---------------

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_unsigned.all;

entity OU is

generic (n:natural:=8);

port( -- n = 8

clk,rst:in std_logic;

d1:in std_logic_vector(2*n-1 downto 0);

d2:in std_logic_vector(n-1 downto 0);

f:in std_logic;

y:in std_logic_vector(24 downto 1);

x:out std_logic_vector(10 downto 1);

DBUS:out std_logic_vector(2*n-1 downto 0)

);

end OU;

--}} End of automatically maintained section

architecture OU of OU is

--use ieee.std_logic_unsigned.all;

signal A:std_logic_vector(2*n-1 downto 0);

signal B:std_logic_vector(n downto 0);

signal C:std_logic_vector(n downto 0); --Po GSA 7

signal CnT:std_logic_vector(3 downto 0);

--signal CnTu:std_logic_vector(2 downto 0);

signal TgS,IRQ1,IRQ2:std_logic;

--signal stop:std_logic:= '0';

begin

process (clk,rst) is

begin

if rst='0' then A <=(others=>'0');

B <=(others=>'0');

C <=(others=>'0');

Cnt <= "1000";

-- CnT <= "111";

elsif rising_edge(clk) then

if y(1)='1' then A <= d1;

elsif y(19)='1' then A <= ("00000000" & d1(n-1 downto 0));

elsif y(5)='1' then A(2*n-1 downto n-1) <= IEEE.std_logic_signed."+"(A(2*n-1 downto n-1), (not B));

A(2*n-1 downto n-1) <= IEEE.std_logic_signed."+"(A(2*n-1 downto n-1),1);--****

elsif y(6)='1' then A(2*n-1 downto n-1) <= IEEE.std_logic_signed."+"(A(2*n-1 downto n-1), B);

elsif y(12)='1' then A <= (A(2*n-2 downto 0) & '0');

elsif y(13)='1' then A <= IEEE.std_logic_signed."+"(A,(not B));

A <= IEEE.std_logic_signed."+"(A,1);

elsif y(14)='1' then A <= IEEE.std_logic_signed."+"(A,B);

end if;

if y(2)='1' then B <= (d2 & '0');

elsif y(20)='1' then B <= ('0' & d2);

elsif y(4)='1' then B <=(B(n) & B(n downto 1));--B <= B(8) & B(7 downto 0);-- B <= '0' & B(8) & B(8 downto 2);

elsif y(22)='1' then B <= '0' & C(0) & B(n-1 downto 1); --B <= '0' & C(0)&B(6 downto 0);--B <= '0' & C(0)& '0'& B(7 downto 2);

end if;

if y(7)='1' then C <=(others=>'0');

elsif y(9)='1' then C <= '0'&C(n-2 downto 0)&'1'; --elsif y(9)='1' then C <= C(n-1 downto 0) & '1';

elsif y(10)='1' then C <= '0'&C(n-2 downto 0)&'0'; --elsif y(10)='1' then C <= C(n-1 downto 0) & '0';

elsif y(15)='1' then C <= IEEE.std_logic_signed."+"(C,1);

elsif y(21)='1' then C <= IEEE.std_logic_unsigned."+"(C,'0'&A(n-1 downto 0)); --sm <= sm + 1;--sm <= IEEE.std_logic_unsigned."+"(('0'& C),A(7 downto 0));--C + A(7 downto 0); sm <= ('0'& C) + A(7 downto 0);

elsif y(23)='1' then C <= '0'& C(n downto 1);--C <= '0' & C(7 downto 1);

end if;

if y(8)='1' then CnT<="1000";

elsif y(11)='1' then CnT <= CnT - 1;

end if;

if y(3)='1' then TgS <= A(2*n-1);

end if;

if y(17)='1' then IRQ1 <= '1'; assert (0>1) report "IRQ1 was thrown" severity failure ;

elsif y(18)='1' then IRQ2 <= '1'; assert (0>1) report "IRQ2 was thrown" severity failure ;

end if;

end if;

end process;

-- IRQ1 <= '1' when y(16)='1';--assert (0>1) severity failure;

-- IRQ2 <= '1' when y(17)='1';--assert (0>1) severity failure;

DBUS <= C(n-1 downto 0) & B(n-1 downto 0) when y(24)='1'else

--DBUS <=

"00000000" & C(n-1 downto 0) when y(16)='1' else (others=>'Z');

x(1) <= f;

x(2) <= '1' when B = "000000000" else '0';

x(3) <= A(2*n-1) xor B(n);

x(4) <= '1' when CnT = "000" else '0';

x(5) <= A(2*n-1) xor TgS;

x(6) <= B(n);

x(7) <= B(n) xor TgS;

x(8) <= TgS;

x(9) <= '1' when A = "0000000000000000" else '0';

x(10) <= B(0);

end OU;

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.std_logic_unsigned.all;

entity CU is

port(

clk,rst:in std_logic;

x:in std_logic_vector(10 downto 1);

y:out std_logic_vector(24 downto 1)

);

end CU;

architecture CU of CU is

subtype TCommand is std_logic_vector(37 downto 0);

type TROM is array (0 to 31) of TCommand;

constant ROM:TROM := (

-- |----------- y --------||x ||-a0||-a1|

"000000000000000000000000 0001 0000111010",--0

"00000000000000000000001100100001000011",--1

"00000000000000000000110000110010000101",--2

"00000001000000000000000000000000000000",--3

"00000000000000000001000000110011011111",--4

"00000000000000000010000000110011011111",--5

"00000000000000001100000000110011101000",--6

"00000000000000010000000000000100101001",--7

"00000000000000100000000000000100101001",--8

"00000000000001000000000001000101001111",--9

"00000000000000000000000000110101101100",--10

"00000000000010000000000000000110101101",--11

"00000000000010000000000000000111001110",--12

"00000000000100000000000000110011101000",--13

"00000000001000000000000000110011101000",--14

"00000000000000000000000001011000010001",--15

"00000000000000000000000001111010011000",--16

"00000000000000000000000001101001010011",--17

"00000000001000000000000001111010011000",--18

"00000000000100000000000001111010011000",--19

"00000000000000000000000010000000010101",--20

"00000000000000000000000010010000010110",--21

"00000000010000000000000000001011110111",--22

"00000000100000000000000000000000000000",--23

"00000000000000000000000010001011011001",--24

"00000000000000000000000010011011000000",--25

"00001100000000001100000010101110011011",--26

"00010000000000000000000000001110011100",--27

"01100000000001000000000001001110111110",--28

"00000000000000000000000010101110011011",--29

"10000000000000000000000000000000000000",--30

"00000010000000000000000000000000000000");

signal RegCom:TCommand;

signal xx:std_logic_vector(10 downto 1);

begin

process (clk,rst) is

variable j:integer:=1;

begin

if rst = '0' then RegCom <= (others => '0');

elsif rising_edge(clk) then

case RegCom(13 downto 10) is

when "0001" => j:=1;

when "0010" => j:=2;

when "0011" => j:=3;

when "0100" => j:=4;

when "0101" => j:=5;

when "0110" => j:=6;

when "0111" => j:=7;

when "1000" => j:=8;

when "1001" => j:=9;

when "1010" => j:=10;

when others =>null;

end case;

if((x(j)='0') or (RegCom(13 downto 10)="0000")) then

RegCom<=ROM(conv_integer(RegCom(9 downto 5))); -- A0

else

RegCom<=ROM(conv_integer(RegCom(4 downto 0))); -- A1

end if;

end if;

end process ;

y <= RegCom (37 downto 14);

end CU;

----------------

--cpu.vhd

----------------

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use work.all;

entity CPU is

port(

clk,rst:in std_logic;

d1:in std_logic_vector(15 downto 0);

d2:in std_logic_vector(7 downto 0);

F:in std_logic;

DBUS:out std_logic_vector(15 downto 0)

);

end CPU;

--}} End of automatically maintained section

architecture cpu of cpu is

component OU

port(

clk,rst:in std_logic;

d1:in std_logic_vector(15 downto 0);

d2:in std_logic_vector(7 downto 0);

f:in std_logic;

y:in std_logic_vector(24 downto 1);

x:out std_logic_vector(10 downto 1);

DBUS:out std_logic_vector(15 downto 0)

);

end component ;

component CU

port (

clk,rst:in std_logic;

x:in std_logic_vector(10 downto 1);

y:out std_logic_vector(24 downto 1)

);

end component ;

signal y: std_logic_vector (24 downto 1);

signal x: std_logic_vector (10 downto 1);

signal nclk: std_logic;

begin

nclk <= not clk;-- after 10 ns;

dd1:OU port map (nclk,rst,d1,d2,f,y,x,DBUS);

dd2:CU port map (clk,rst,x,y);

end cpu;

Дата добавления: 2018-10-27; просмотров: 351; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!