Принцип адресного взаимодействия частей микропроцессорной системы

На этапе технической реализации микропроцессорную систему представляют следующей структурной схемой, изображенной на рис.П2.1:

Рис.П2.1:

МЦП - модуль центрального процессора

МОЗУ - модуль оперативного запоминающего устройства (ОЗУ)

МПЗУ - модуль постоянного запоминающего устройства (ПЗУ)

МСВУ - модуль связи с внешними устройствами (ВУ)

В общем случае основная память процессора (т.е. его запоминающее устройство - ЗУ) содержит ОЗУ и ПЗУ. ОЗУ обеспечивает как чтение находящейся в нем информации, так и запись новой информации. Обычно ОЗУ реализуется как энергозависимая память, содержимое которой разрушается при отключении питания и принимает хаотические значения при включении питания. ПЗУ обеспечивает только чтение находящейся в ней информации и является энергонезависимой памятью, содержимое которой не разрушается при включении/отключении питания. В ПЗУ хранится программа работы микропроцессорной системы и неизменные константы. Запись информации в ПЗУ производится вне микропроцессорной системы на специальных устройствах - программаторах.

Внешние устройства микропроцессорной системы являются источниками и приемниками информации, подвергающейся обработке или являющейся результатом обработки.

Устройствами ввода/вывода являются клавиатура, монитор, принтер, цифровые индикаторы, электромагнитные реле и т.п.

Основополагающим принципом функционирования микропроцессорной системы является принцип адресного взаимодействия её частей. Суть этого принципа заключается в том, что микропроцессор способен обмениваться данными только с программно доступными элементами. Программно доступный элемент - физический элемент микропроцессорной системы, информация о состоянии которого может быть считана микропроцессором или состояние этого элемента может быть изменено микропроцессором. Все возможное количество программно доступных элементов называют адресным пространством микропроцессора. Физический объем адресного пространства самого микропроцессора (но не микропроцессорной системы на его основе!!!) однозначно связан с количеством адресных выводов микропроцессора или, как принято говорить, с шириной адресной шины микропроцессора. Если количество адресных выводов микропроцессора равно n, то его адресное пространство равно либо N1= 2n, либо не более чем N2= 2n+1. Величина N1 характерна для тех микропроцессоров, которые относят к микропроцессорам с совмещенным адресным пространством. Их особенностью является то, что все их адресное пространство делится между ОЗУ, ПЗУ и внешними устройствами. Величина N2 характерна для тех микропроцессоров, которые относят к микропроцессорам с раздельными адресными пространствами между запоминающими устройствами и внешними устройствами. Микропроцессоры с совмещенными и раздельными адресным пространствами легко определить: если микропроцессор имеет только выводы «Чтение ЗУ» и «Запись ЗУ», то это процессор с совмещенным адресным пространством. Если же у процессора дополнительно имеются выводы «Чтение ВУ», «Запись ВУ», то это процессор с раздельными адресными пространствами.

Первоначальным этапом разработки микропроцессорной системы является этап разделения адресного пространства. На этом этапе ориентировочно определяются потребные объемы ОЗУ и ПЗУ и закрепляются за ними соответствующие области адресных пространств. Выбираются так же соответствующие микросхемы, на основе которых будут реализованы ОЗУ и ПЗУ. Определяются все внешние устройства, необходимые для реализации микропроцессорной системы, выбираются дисциплины взаимодействия микропроцессора с внешними устройствами, а так же закрепляются определенные области адресного пространства за каждым внешним устройством с учетом возможностей управления ими – только чтение, только запись или чтение/запись. Только после распределения адресного пространства микропроцессора можно приступать к раздельной разработке аппаратной части микропроцессорной системы и её программной части.

Инженер по специальности 230101 «Вычислительные машины, комплексы, системы и сети» должен уметь рационально распределять адресные пространства в микропроцессорных системах, а так же определять распределение адресного пространства в любой микропроцессорной системе.

В качестве бытовой модели адресного пространства микропроцессора рассмотрим всем известный зал кинотеатра и процедуру его посещения.

Для того, что бы посетить кинотеатр необходимо прежде купить билет (или билеты). Иногда мы бываем рады тому, что нам достались хоть какие-то билеты, то есть хоть какие-то места! Но бывает и так, что желательно приобрести билеты на какие-то определенные места – что бы лучше видеть или слышать, или не видеть и не слышать ничего, лишь бы ощущать близость дорогого человека.

Но, как бы то ни было, мы заходим в зрительный зал и отыскиваем наши места, которые указаны в билете. Процедура достаточно проста – в билете указан ряд и место в ряду, которое мы можем занять. Пусть в кинотеатре 32 ряда и в каждом по 32 места. То есть всего 1024 места. Представьте себе, что бы было, если все места в кинотеатре были пронумерованы от 1 до 1024 и так же были бы указаны в билетах! Процедура посадки по местам растянулась бы на довольно длительное время. Если же указать в билетах номер ряда и номер места, то время отыскания своего места требует минимума физических и умственных усилий.

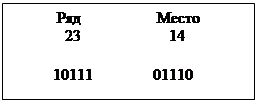

Итак, в билете указывается номер ряда и номер места, причем номер мест повторяется в каждом ряду, но рядов с одинаковыми номерами нет. Пусть номер нашего ряда 23, а номер места 14. Нумерация в билетах осуществляется в десятичной системе счисления, но микропроцессорная техника оперирует только с двоичными числами. На рис.П2.2 показано, как бы выглядел наш билет, если бы нумерация рядов и мест осуществлялась в десятичной и двоичной системах счисления.

Рис. П2.2

Так как в каждом ряду по 32 места, а рядов то же 32, то для представления таких номеров в двоичном коде потребуется по 5 двоичных разряда. Правда, при этом нумерация рядов и мест в десятичной и двоичной системах счисления будет от 0 до 31 или от 0000 до 11111.

Вполне возможно, что в самом не далеком будущем мы будем пользоваться электронными билетами. Тогда нам не придется даже отыскивать своё место – при входе наши места будут выделены светящимися индикаторами. Это вполне осуществимо даже сейчас, если номера рядов и мест кодировать двоичными числами. При этом достаточно условиться, что какое-то количество старших двоичных разрядов указывают номер ряда, а оставшиеся младшие двоичные разряды указывают номер места. Такой порядок кодирования обусловлен тем, что номера мест многократно повторяются, а номера рядов – всегда отличны друг от друга.

Бывают случаи, когда в зале кинотеатра нет ни одного свободного места, то есть все его адресное пространство распределено (занято). Но бывает и так, что пустуют некоторые ряды, или по нескольку рядов подряд. Причем пустующие ряды не поддаются каким-либо закономерностям. Иначе говоря, адресное пространство кинотеатра занято не полностью и несколько хаотично.

Будем надеяться, что бытовая модель адресного пространства микропроцессора достаточно понятна.

Рассмотрим схему электрическую функциональную модуля ПЗУ, представленную на рис.П2.3.

Рис. П2.3

Модуль построен из 4-х однотипных микросхем DD1, DD2, DD3, DD4. Первоначально необходимо определиться с, так называемой, организацией модуля ПЗУ, под которой понимают количество ячеек памяти модуля (L), а так же количество разрядов (K) в каждой ячейке памяти. Организацию модулей памяти принято обозначать как L*K. Будем отождествлять количество ячеек памяти в модуле ПЗУ с количеством рядов в кинотеатре, а количество разрядов каждой ячейки памяти – с количеством мест в каждом ряду кинотеатра. Однако теперь следует понимать и принципиальное отличие между кинотеатром и микросхемой памяти: и запись, и чтение данных в/из ячейки микросхем памяти производится параллельно (т.е. обращаются к одной единственной ячейки памяти, но одновременно ко всем её разрядам).

Сосредоточим своё внимание на одной единственной микросхеме, например, на DD1.

Микросхема имеет n = 8 адресных входов (А0,А1…А7). Это позволяет обращаться к Lм = 2n ячейкам памяти, расположенным в микросхеме. Микросхема имеет Kм = 4 выходов данных (D0, D1, D2, D3), т.е. разрядность микросхемы 4. Ясно, что организация каждой из однотипных микросхем памяти Lм*Kм = 28*4 = 256*4 = 1024 бит.

Каждая микросхема памяти имеет управляющие входы CS1 и CS2 (CS – Chip Select, т.е. выбор кристалла или, иначе говоря, выбор микросхемы). Как видно из рис.П2.3 управляющие сигналы CS1 и CS2 являются активными, если они принимают значение логического нуля, т.е. когда имеют низкий уровень напряжения, близкий к уровню нулевого потенциала. В различных микросхемах ПЗУ несколько управляющих сигналов могут объединяться внутри микросхемы по логической функции И или логической функции ИЛИ. В данном случае не принципиально, как объединены сигналы CS1 и CS2 внутри микросхемы, так как они объединены между собой и управляются одним и тем же сигналом SL1 (Select – выбор). Принципиальным является то, что когда управляющие сигналы CS1 и CS2 являются активными, то разрешается чтение и вывод данных на выходы D0, D1, D2, D3 из соответствующей ячейки микросхемы ПЗУ, причем адрес ячейки однозначно определяется двоичным кодом, установленным на входах А0,А1…А7. Всё вышесказанное справедливо для всех микросхем, представленных на рис.П2.3.

Теперь определимся с организацией всего модуля ПЗУ, для чего рассмотрим соединения между микросхемами DD1, DD2, DD3, DD4.

Микросхемы DD1 и DD2 управляются одним и тем же сигналом SL1, следовательно, чтение данных из этих микросхем производится одновременно. Выходы D0, D1, D2, D3 этих микросхем не объединены между собой, то есть две микросхемы DD1 и DD2 формируют уже 8-ми разрядное выходное слово, т.е. KПЗУ = 8. Одноименные адресные входы А0,А1…А7 микросхем DD1 и DD2 объединены между собой и одновременно подключены к одноименным (младшим) разрядам шины адреса микропроцессора (ADR0, ADR1…ADR7). Отсюда следует, что чтение данных из микросхем DD1 и DD2 производится из одинаковых по номеру ячеек памяти, общее количество которых равно Lм = 2n =28 =256.

Организация пары микросхем DD3 и DD4 практически не отличается от организации пары микросхем DD1 и DD2 за исключением того, что микросхемы DD3 и DD4 одновременно управляются сигналом SL2.

Остается рассмотреть соединение между собой пар микросхем DD1, DD2 и DD3, DD4. Для этого обратим внимание на жгутовое соединение, выделенное на рис.П2.3 жирной линией. Данное графическое обозначение следует понимать так: в жгуте 8 электрических линий связи (проводов). Каждый провод имеет свой уникальный номер. Повторяющиеся номера в жгутовом соединении обозначают точки электрического подключения одного и того же провода. Так на рис.П2.3 провод 1 соединяет выводы D0 микросхем DD1 и DD3, а так же один из выводов резистора R1. Анализ жгутового соединения показывает, что пары микросхем DD1 и DD2, DD3 и DD4 объединены параллельно друг другу. Следует знать: в разных жгутовых соединениях возможна повторяющаяся нумерация проводников, однако при этом жгуты на схеме не должны пересекать друг друга.

Таким образом, схемы подключения пар микросхем DD1 и DD2 (или DD3 и DD4) позволяют увеличить количество разрядов в ячейках памяти (корректно говорить «наращивать разрядность»). По аналогии с кинотеатром – увеличивается число мест в каждом ряду. Схема подключения между собой пар микросхем DD1 и DD2, DD3 и DD4 обеспечивает увеличение общего объема ПЗУ, в данном случае до величины LПЗУ=2* Lм = =2*256 = 512. Таким образом, организация ПЗУ, представленного на рис.П2.3, есть LПЗУ* KПЗУ = 512*8. Другими словами, данное ПЗУ содержит 512 ячеек памяти, разрядность которых равна 8. То же самое можно сказать так: объем ПЗУ равен 512–ти байтам.

Совокупность микросхем, определяющих разрядность шины данных микропроцессорной системы, принято называть «банком памяти». Так для модуля ПЗУ, представленного на рис.П2.3, микросхемы DD1 и DD2 образуют первый банк памяти, а микросхемы DD3 и DD4 – второй банк памяти. Если вновь проводить аналогию с кинотеатром, то ряды в кинотеатре аналогичны банкам памяти, а места в каждом ряду – ячейкам памяти в каждом банке. Теперь становится понятно, что сигналы SL1 и SL2 управляют выбором определенного банка памяти, при этом сигналы ADR0, ADR1…ADR7 подаются одновременно на оба банка памяти. Если активным будет сигнал SL1, то чтение данных будет осуществляться из первого банка памяти (микросхемы DD1, DD2), а если активизируется сигнал SL2, то чтение данных будет осуществляться из второго банка памяти (микросхемы DD3, DD4). В любой момент времени может быть активным только один какой - либо сигнал выбора банков! Обеспечить данное требование может такой цифровой узел как дешифратор (декодер - DC).

Дешифраторы, управляющие формированием сигналов выбора банков в модулях памяти, называют дешифраторами адреса банков или просто дешифраторами адреса. Для модуля ПЗУ, представленного на рис.П2.3 на вход DC подключены старшие разряды шины адреса микропроцессора (ADR8, ADR9…ADR15) и сигнал чтения памяти (MRD - memory read). Из совокупности этих сигналов формируются сигналы выбора банков памяти SL1 и SL2. В качестве дешифраторов адреса в модулях памяти используются дешифраторы со стробированием, при этом стробирующими сигналами являются сигналы чтения памяти (MRD) или записи памяти (MWR – memory write). Следует помнить, что дешифраторы адреса в модулях памяти могут быть реализованы как на специализированных микросхемах ( DC), так и на логических элементах! Это становится понятным из следующих рассуждений.

В модуле памяти ПЗУ, представленном на рис.П2.3, адресные линии ADR0, ADR1…ADR7 однозначно определяют адрес ячейки памяти в каждом банке, а адресные линии ADR8, ADR9…ADR15 – номер банка. Линий ADR8, ADR9…ADR15 – 8, следовательно, адресное пространство управляющего микропроцессора способно разместить 28 = 256 банков памяти с организацией 256*8 бит. Таким образом, для формирования всего двух сигналов SL1 и SL2 не целесообразно использовать специализированную микросхему DC, т.к. она должна иметь 8 входов и 256 выходов, из которых использовались бы всего 2 выхода! В данном случае дешифратор адреса целесообразно реализовывать на логических элементах. Подобные дешифраторы называют неполными дешифраторами.

Проводя аналогии с кинотеатром, отмечалось: «Бывают случаи, когда в зале кинотеатра нет ни одного свободного места, то есть все его адресное пространство распределено (занято). Но бывает и так, что пустуют некоторые ряды, или по несколько рядов подряд. Причем пустующие ряды не поддаются каким-либо закономерностям. Иначе говоря, адресное пространство кинотеатра занято не полностью и несколько хаотично». Для прояснения этой аналогии представим себе модуль ПЗУ, аналогичный представленному на рис.П2.3, но меньшего информационного объема. Предположим, что к банкам памяти подведены всего две адресные линии ADR0, ADR1, а к DC ещё две старшие линии адреса ADR2, ADR3. В этом случае полагаем, что организация банка памяти 4*8, всего модуля ПЗУ - 8*8, а все адресное пространство микропроцессора 24 = 16. Тогда следует, что в таком адресном пространстве можно разместить всего 4 банка памяти с организацией 4*8. Рассмотрим возможности размещения двух банков памяти с организацией 4*8 в адресном пространстве, объемом 24 на основе следующей табл. П2.1.

В табл. П 2.1 всё адресное пространство процессора представлено в виде последовательности возрастающих двоичных кодов, а так же приведена наиболее рациональная разбивка адресного пространства на банки с организацией 4*8. Рациональность представленной разбивки состоит в том, что формирование сигналов выбора банков предельно простое и заключается в реализации следующих логических уравнений:

Таблица П2.1

| SLj | № банка памяти | № ячейки в банке памяти | ||

| ADR3 | ADR2 | ADR1 | ADR0 | |

| SL0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | |

| 0 | 0 | 1 | 0 | |

| 0 | 0 | 1 | 1 | |

| SL1 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | |

| 0 | 1 | 1 | 0 | |

| 0 | 1 | 1 | 1 | |

| SL2 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | |

| 1 | 0 | 1 | 0 | |

| 1 | 0 | 1 | 1 | |

| SL3 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 0 | |

| 1 | 1 | 1 | 1 | |

На рис. П2.4 показаны возможные варианты размещения в адресном пространстве упрощенного процессора двух банков памяти с организацией 4*8.

| № банков | Вари- ант 1 | Вари- ант 2 | Вари- ант 3 | Вари- ант 4 | Вари-ант 5 | Вари- ант 6 |

| Банк 0 ( SL0) | ||||||

| Банк 1 ( SL1) | ||||||

| Банк 2 ( SL2) | ||||||

| Банк 3 ( SL3) |

Рис П2.4

В реальных микропроцессорных системах банки модулей памяти располагают последовательно друг за другом (без разрывов), например так, как в вариантах 1,2,3 на рис.П2.4. Модули ОЗУ и ПЗУ так же могут следовать последовательно друг за другом (без разрывов), но достаточно часто их располагают и с разрывами в адресном пространстве. Цель такого размещения модулей ОЗУ и ПЗУ становится понятной, если вспомнить, что, как уже говорилось, «…Первоначальным этапом разработки микропроцессорной системы является этап разделения адресного пространства. На этом этапе ориентировочно определяются потребные объемы ОЗУ и ПЗУ и закрепляются за ними соответствующие области адресных пространств». Таким образом, разрывы между адресными пространствами модулей ОЗУ и ПЗУ оставляют для того, что бы можно было в случае необходимости оперативно увеличить информационную емкость модулей памяти.

Достаточно часто в МПС, к которым не предъявляется жестких требований по надёжности работы, используется упрощенная схема формирования сигналов выборки банков (или модулей) памяти. В таких схемах на дешифратор адреса может быть подано ограниченное число старших адресных линий. Что бы понять принцип построения таких схем обратимся к соотношениям (1)…(4) и рис. П2.4.

Предположим, что реализуется вариант 1 (см. рис. П2.4) распределения адресного пространства двух банков памяти, при котором первые два банка заняты модулем ПЗУ, а второй и третий банки – «пустые», то есть их адресные пространства не заняты. Тогда, как следует из соотношений (1)…(4), для обращения к банкам 0 и 1 достаточно реализовать следующие соотношения

SL0 = ADR2, (5),

SL1 = ADR2. (6).

При таком подходе молчаливо предполагается, что если микропроцессорная система функционирует правильно, то процессор не выйдет из тех адресных пространств, с которыми он оперирует. Если же процессор по каким-либо причинам попадет в «пустые» области адресного пространства, то принимают специальных технические решения по принудительному восстановлению его правильного функционирования.

Выше приведенных сведений достаточно для решения практических задач по определению распределения адресного пространства в микропроцессорных системах даже для студентов, знакомых с цифровой схемотехникой и правилами выполнения схем электрических принципиальных цифровой техники.

Следует знать, что в подавляющем большинстве случаев адресные выводы микропроцессора подключатся к различным модулям не непосредственно, а через буферные микросхемы, умощняющие сигналы, формируемые микропроцессором!

Определим объемы модулей ОЗУ и ПЗУ и адресные пространства, занимаемые ими в микроЭВМ, фрагмент схемы электрической принципиальной которой представлен на рис.П2.5. Данная схема заимствована из литературного источника [5].

Прежде всего, рассмотрим на схеме микропроцессор (CPU) и его адресные линии. Микропроцессор (DD1) имеет 16 адресных выводов (А0,А1…А15). Микропроцессор типа КР580ВМ80, и, следовательно, он функционирует совместно с системным котроллером (микросхема DD8), которая формирует как сигналы чтения (MR) и записи (MW) памяти, так и сигналы чтения (IR) и записи (IW) внешних устройств. Следовательно, данный микропроцессор с раздельными адресными пространствами запоминающих (ЗУ) и внешних (ВУ) устройств.

Жгутовое соединение между микросхемами DD1 и DD5, DD6 указывает на электрические подключения адресных выводов микропроцессора к выводам буферных регистров DD5 и DD6, с выходов которых формируется системная шина адреса (ША) микроЭВМ.

Микросхемы буферных регистров DD5, DD6 включены по схеме повторителей входных сигналов. Это означает, что, например, на вывод «0» микросхемы DD5 транслируется сигнал, поступающий на вход D0 микросхемы DD5, на вывод «1» транслируется сигнал со входа D1 и т.д. Таким образом, на выходах микросхем DD5, DD6 повторяются сигналы с выходов А0,А1…А15 микропроцессора. Будем обозначать сигналы с выходов микросхем DD5, DD6 как ША0, ША1…ША15, помня, что А0 = ША0, А1 = ША1 … и т.д.

Рассмотрим микросхемы с функциональным назначением ROM и/или RAM: ROM – read only memory (память только для чтения), то есть ПЗУ; RAM – random access memory (память с произвольной выборкой), то есть ОЗУ.

Анализ схемы показывает, что на ней отсутствует ОЗУ (RAM), но присутствуют две микросхемы ПЗУ (ROM) – микросхемы DD10 и DD11. Рассмотрим соединение выходов данных микросхем, обозначенное в виде жгутового соединения. Анализ этого жгутового соединения показывает, что одноименные выходы микросхемы DD10 и DD11 объединены между собой, что говорит о том, что данное ПЗУ 8-ми разрядное, т.е. КПЗУ = 8. Об этом же можно было с уверенностью утверждать, если вернуться к микросхеме DD1 (микропроцессору) и определить разрядность его шины данных (выводы D0… D7).

Рис.П2.5

Рис.П2.5

|

Рассмотрим теперь соединение адресных выводов микросхем DD10 и DD11 (А0…А8). Одноименные выводы объединены между собой и подключены к одноименным выводам буферных регистров DD5, DD6, то есть к одноименным младшим разрядам шины адреса микропроцессорной системы (ША0, ША1…ША8). Так как адресных входов у каждой из микросхем DD10 и DD11 по 9, то каждая из них занимает адресное пространство Lм = 29 = 512 байт, образуя по одному банку памяти ПЗУ. Полная организация всего модуля ПЗУ равна LПЗУ * КПЗУ = 210 * 8 = 1024*8 или иначе 1К байт.

Каждая из микросхем DD10 и DD11 управляется сигналами V1, V2, V3, V4. Сигналы V1, V2 являются активными, если имеют низкий уровень напряжения (т.е. принимают значение логического нуля), а сигналы V3, V4 являются активными, если принимают значение логической единицы. При этом выборка каждой из микросхем DD10 и DD11 будет осуществляться при выполнении условия

SLМ = V1 & V2 & V3 & V4 (7)

О справедливости соотношения (7) сложно судить на основании представленного фрагмента принципиальной схемы микроЭВМ, однако его справедливость может быть проверена (определена) с использованием дополнительных справочных данных для микросхем КР556 РТ5 (DD10 и DD11). Располагая соотношением (7), можно приступать к определению номеров банков памяти, которые занимает в микроЭВМ модуль ПЗУ.

Определим первоначально, какой номер банка занимает микросхема DD10. Её вывод V1 проводом №10 подключен к выводу 18 микросхемы DD6. Данный вывод микросхемы является её выходом, на котором формируется 9 разряд шины адреса микроЭВМ (ША9). Аналогичным образом устанавливаем, что вывод V2 микросхемы DD10 соединен с ША12, вывод V3 соединен с одноименным выводом микросхемы DD11 и с проводом №18, который уходит в жгутовое соединение, которое на данном фрагменте схемы обрывается. Вывод V4 микросхемы DD10 соединен с одноименным выводом микросхемы DD11 и выходом 2 инвертора DD 9.1, вход 1 которого соединен с инверсным выходом «0» (вывод 1) микросхемы DD 7. Микросхема DD7 представляет собой полный дешифратор 4→16 со стробированием, однако, режим стробирования отключен подачей низкого потенциала на выводы 18 и 19 дешифратора.

Входы дешифратора подключены к старшим разрядам ША. Причем, ША12 подключена к младшему разряду дешифратора адреса, а ША15 – к старшему разряду дешифратора. Легко понять (зная правила выполнения условных графических обозначений!), что сигнал на выходе «0» дешифратора активизируется только в том случае, когда ША12 = ША13 = ША14 = ША15 = 0.

На основе проведенного анализа можно составить следующее логическое уравнение (8):

SLDD 10 = V 1 & V 2 & V 3 & V 4 = ША9& ША11& ША12 & ША13 &

SLDD 10 = V 1 & V 2 & V 3 & V 4 = ША9& ША11& ША12 & ША13 &

ША14 & ША15 & X (8)

Как видно из соотношения (8), в нем отсутствует сигнал ША10, а так же обязательный сигнал чтения памяти (MR), но присутствует неопределенный сигнал X. Данный сигнал Х либо сигнал чтения памяти, либо сигнал чтения памяти, «привязанный» к сигналу ША10. Для выяснения данного обстоятельства обратимся к системному контроллеру, выполненному на микросхеме DD8. На выводе 24 этой микросхемы формируется сигнал MR отрицательной полярности, который, как видно из схемы, проводом 9 передается на вход 11 инвертора DD 21.5. С выхода 10 данного инвертора идет провод под №18 в жгутовое соединение, которое хоть не пересекает на схеме жгут, охватывающий выводы микросхем DD10 и DD11, но имеет в этом жгуте тот же номер провода 18. Сигнал MR ни каким образом не связан с сигналом ША10, следовательно, сигнал ША10 не участвует в формировании сигнала выбора банков в модуле ПЗУ. Однако, зная ту особенность микропроцессора КР580ВМ80, что после начальной инициализации его счетчик команд обнуляется, можно предположить, что при написании программ для микроЭВМ полагают сигнал ША10 равным нулю. Таким образом, уточняем соотношение (8):

SLDD 10 =ША9&ША11&ША12 &ША13 &ША14 &ША15 & MR (9)

SLDD 10 =ША9&ША11&ША12 &ША13 &ША14 &ША15 & MR (9)

Рассуждая подобным образом, находим уравнение для формирования сигнала выборки микросхемы DD11:

SLDD 11 =ША9&ША11&ША2&ША13& ША14&ША15 & MR (10)

SLDD 11 =ША9&ША11&ША2&ША13& ША14&ША15 & MR (10)

Теперь можно определить адресное пространство, занимаемое в микроЭВМ модулем ПЗУ, используя систематизированные результаты анализа схемы, представленные в таблице П2.2.

Если считать ША 10 = 0, то адресное пространство ПЗУ есть Апр(ПЗУ) = 0000 Н…03FF H, в чем легко убедиться, представив двоичный код Amin микросхемы DD10 и Аmax микросхемы DD11 в шестнадцатеричном коде. Если же считать ША 10 = 1, то Апр(ПЗУ) = 4000 Н…07FF H.

Таблица П2.2

| Адресные пространства микросхем ПЗУ в hex кодах | № банка микросхемы | № ячейки в микросхеме | DDJ | |||||||||||||||

|

ШИНА АДРЕСА (ША) МИКРОЭВМ | ||||||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

| Amin = 000 0 H | 0 | 0 | 0 | 0 | 0 | 0/1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | DD10 | |

| … | . | . | . | . | . | . | . | . | . | . | . | . | . | . | . | . | ||

| Amax = 01FF H | 0 | 0 | 0 | 0 | 0 | 0/1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | ||

| Amin = 0200 H | 0 | 0 | 0 | 0 | 0 | 0/1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | DD11 | |

| … | . | . | . | . | . | . | . | . | . | . | . | . | . | . | . | . | ||

| Amax = 03FF H | 0 | 0 | 0 | 0 | 0 | 0/1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | ||

ПРИЛОЖЕНИЕ 3

Доступ к внешней памяти ВЕ51

В системах на основе МК51 возможно использование двух типов внешней памяти: постоянной памяти программ и оперативной памяти данных. Обращение к внешней памяти программ осуществляется при помощи управляющего сигнала  (

(  ), который выполняет функцию строб-сигнала чтения. Доступ к внешней памяти данных обеспечивается управляющими сигналами

), который выполняет функцию строб-сигнала чтения. Доступ к внешней памяти данных обеспечивается управляющими сигналами  и

и  (

(  и

и  ), которые автоматически формируются в линиях Р3.7 и Р3.6 при выполнении портом 3 альтернативных функций. Доступ к внешней памяти данных возможен с использованием 16-битного или 8-битного адреса.

), которые автоматически формируются в линиях Р3.7 и Р3.6 при выполнении портом 3 альтернативных функций. Доступ к внешней памяти данных возможен с использованием 16-битного или 8-битного адреса.

При обращении к внешней памяти используются выходные драйверы портов Р0 и Р2, а также входной буфер порта Р0. При этом через Р0 в режиме временного мультиплексирования сначала выводится младший байт адреса, а затем выдается или принимается байт данных. Через Р2 пересылается старший байт адреса, если разрядность адреса равна 16 битам (рисунок П3.1).

Таким образом при обращении к внешней памяти данных и к внешней памяти программ используются одни и те же шины, но разные управляющие сигналы.

Схема подключения внешних микросхем памяти к выводам корпуса микроконтроллера семейства MCS-51 приведена на рисунке П3.1. Буферный регистр на этой схеме предназначен для запоминания младших восьми битов адреса, передаваемых через шину адреса, совмещенную с портом 0. Во время пересылки адреса через Р0 микроконтроллер вырабатывает синхроимпульс на выводе ALE, который

позволяет запомнить младший байт адреса в буферном регистре.

Микроконтроллеры семейства MCS-51 имеют внешний вывод ЕА, с помощью которого можно запретить работу внутренней памяти. Для этого необходимо подать на ЕА логический 0 (т.е. соединить этот вывод с общим проводом). Внутренняя память программ окажется отключенной и, начиная с нулевого адреса, все обращения будут направлены к внешней памяти программ.

Таким образом, доступ к внешней памяти программ осуществляется в двух случаях:

- при действии сигнала ЕА=0 независимо от адреса обращения;

- в любом случае, если программный счетчик содержит число, большее, чем максимальный адрес внутренней памяти программ.

Содержимое памяти программ заполняется единожды на этапе разработки МК-систем. Память данных не может быть использована для хранения кодов программы.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Микушин А.В. Занимательно о микроконтроллерах/А.В.Микушин. СПб:БХВ-Петербург, 2006

2. Магда Ю.С. Микроконтроллеры серии 8051: практический подход/Ю.С.Магда. М.:ДМК Пресс, 2008.

3. Угрюмов Е.П. Цифровая схемотехника/Е.П. Угрюмов. СПб:БХВ-Петербург, 2001

4. Щелкунов Н.Н. Микропроцессорные средства и системы/ Н.Н. Щелкунов, А.П. Дианов. М.: Радио и связь, 1989.

5. Бартенев В.Г. От самоделок на логических элементах до микроЭВМ. / В.Г.Бартенев, Б.Е.Алгинин. М.: Просвещение, 1993.

СОДЕРЖАНИЕ

Введение..........................……………………………………......1

Контрольные задания по теме «Микропрограммируемые микропроцессоры»……………………………….....……...........3

Контрольные задания по темам «Однокристальные микропроцессоры», «Организация передачи данных в МПС»……………………………………......................................8

Контрольные задания по теме «Однокристальные микроконтроллеры»…………………………………………….13

Приложение 1..............................................................................17

Приложение 2..............................................................................22

Приложение 3..............................................................................44

Библиографический список................……………..……….....48

МЕТОДИЧЕСКИЕ УКАЗАНИЯ

к выполнению контрольной работы

по дисциплине «Микропроцессорные системы»

для студентов специальности 230101

“Вычислительные машины, комплексы, системы

и сети”

заочной и заочной сокращенной форм обучения

Составители: Петрухнова Галина Викторовна

Тюрин Сергей Владимирович

В авторской редакции

Подписано в печать 25.11.2010.

Формат 60x84/16. Бумага для множительных аппаратов.

Усл. печ. Л. 3.1 Уч.-изд. л. 2.9 . Тираж 100 экз. "С"

Зак. №

ГОУВПО

«Воронежский государственный технический

университет»

394026 Воронеж, Московский просп., 14

Дата добавления: 2018-09-22; просмотров: 1246; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!