Параллельный однотактный парофазный регистр

Чтобы регистр мог «запомнить» слово информации, он должен состоять из соответствующего числа ячеек, каждая из которых должна иметь два устойчивых состояния: лог.0 и лог.1. Эти состояния должны сохраняться сколь угодно долго, но могут быть изменены в любой момент времени.

В качестве ячеек обычно используются синхронные D - триггеры, состояние которых отображает слово информации, а каждый триггер хранит 1 бит информации и соответствует одному разряду слова.

В зависимости от наличия и характера связей между ячейками различают:

1) регистры хранения информации;

2) сдвиговые регистры

3) регистры специального назначения.

Регистры, предназначенные для хранения информации могут работать в двух режимах - записи и хранения информации. При записи «содержимое» ячеек изменяется на новое: в соответствии со значением разрядов входного слова информации. В режиме хранения состояние («содержимое») ячеек регистра остается неизменным пока сохраняется этот режим. Причем во время хранения регистр как бы становится «нечувствительным» к изменению входных информационных сигналов. Такие регистры используются для построения оперативных запоминающих устройств (ОЗУ) ЭВМ. Между ячейками таких регистров взаимных связей нет.Регистры сдвига (сдвиговые регистры) могут работать в трех режимах: 1) записи; 2) хранения и 3) сдвига (последовательной выдачи) информации.

Сдвиговые регистры могут быть реализованы только на динамических триггерах

|

|

|

Рис. Временная диаграмма сдвигового регистра

Универсальные регистры по алгоритму функционирования получили такое название, так как их можно использовать для хранения и преобразования информации, а также для деления частоты импульсов, построения фазовращателей и распределителей импульсов и выполнения математических операций с двоичными числами. Например, сдвиг на один разряд в сторону старших разрядов записанного в регистр слова, можно рассматривать, как умножение на 2 двоичного числа, отображаемого этим словом

Микросхемы памяти. Классификация. Условное графическое обозначение. Наращивание емкости

Микросхемы памяти (или просто память, или запоминающие устройства — ЗУ) предназначены для запоминания, хранения массивов информации, проще говоря, наборов, таблиц, групп цифровых кодов. Каждый код хранится в отдельном элементе памяти, называемом ячейкой памяти

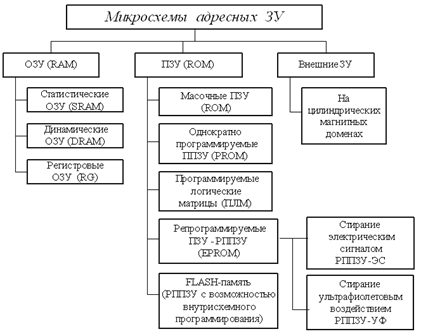

Классификация

В статических ОЗУ в качестве элементов памяти (ЭП) используются статические триггеры на биполярных или МДП-транзисторах. Наибольшее быстродействие имеют ОЗУ на ТТЛШ-элементах, но у них выше энергопотребление.

|

|

|

Динамические ОЗУ сформированы из ЭП на основе полупроводниковых конденсаторов. Поэтому они требуют периодической (через 2 мс) регенерации содержимого. Имеют большую емкость на одну БИС по сравнению с ОЗУ статического типа. На время регенерации доступ к ОЗУ блокируется.

Регистровые ОЗУ характеризуются наивысшим быстродействием. Это могут быть как отдельные микросхемы, так и наборы регистров внутри БИС микропроцессора или контроллеров. Регистровые ОЗУ иногда называют сверхоперативными ЗУ или внутренней памятью процессора.

Масочные ПЗУ характеризуются тем, что информация записывается в них однократно в процессе изготовления путем пережигания перемычек в местах пересечения строк и столбцов в матрице накопителя.

Для однократно программируемых ПЗУ запись информации выполняет пользователь на специальном устройстве – программаторе путем подачи адресов и импульсов записи данных (битов). Электрические сигналы пережигают перемычки в ЭП в матрице накопителя.

ПЛМ представляют собой вариант ПЗУ, в которых запрограммированы (или программируются пользователем) логические функции (правила преобразования) для выходных сигналов по значениям входной информации – адресов ячеек или адресов функций.

|

|

|

Репрограммируемые ПЗУвыполнены на основе специальных МДП-транзисторов, которые изменяют состояние проводимости под воздействием электрического импульса, и сохраняют это состояние длительное время. Программирование РППЗУ должно выполняться не в рабочей вычислительной системе, а с помощью специальных устройств – программаторов ПЗУ. Такие устройства могут сопрягаться с ПЭВМ, что позволяет автоматизировать процесс записи программы в микросхемы памяти. Репрограммируемые ПЗУ отличаются способом стирания информации – с помощью электрических импульсов от программатора или под воздействием специального ультрафиолетового излучения.

В последние годы нашли широкое применение микросхемы Flash-памяти (Flash-ПЗУ). Отличительная особенность таких микросхем – возможность записи информации в процессе работы вычислительной системы, в которой они установлены (те как в ОЗУ), но сохранение информации при отключении питания, как в ПЗУ. Такие микросхемы часто называют «электронным диском на кристалле».

В запоминающих устройствахна ЦМД используется эффект локального перемагничивания микронных областей в тонких магнитных пленках. Микросхемы ЦМД с технологической точки зрения являются микросборками - в корпусе размером 3х3х1 см содержатся пленка на кристалле, система постоянных магнитов и ортогональных катушек. Достоинства ЦМД – высокая помехоустойчивость, помехозащищенность и надежность, высокое быстродействие и емкость (миллионы бит на микросборку), отсутствие электромеханических частей (что характерно для внешних накопителей ПЭВМ). Память на ЦМД используется в бортовых специализированных вычислителях в жестких условиях эксплуатации.

|

|

|

Условные графические изображения микросхем памяти: а – статическое ОЗУ с одноразрядной организацией; б – статическое ОЗУ со словарной организацией и совмещёнными входами-выходами; в – динамическое ОЗУ; г – масочное ПЗУ д – программируемое ПЗУ е – репрограммируемое ПЗУ

На рис. представлены примеры обозначений микросхем статического ОЗУ с одноразрядной организацией (а), со словарной организацией и совмещёнными входами-выходами (б), микросхемы динамического ОЗУ (в), микросхемы МПЗУ (г), ППЗУ (д), РПЗУ (е).

Условное графическое обозначение содержит три поля. В среднем поле помещено обозначение вида микросхемы памяти и данные о её информационной емкости в битах. На левом поле помещены символы, указывающие на назначение выводов и подводимых к ним сигналов. На правом поле помещены обозначения выводов и соответствующих им подводимых или отводимых сигналов, а также обозначение типа выхода (выходов):

Наращивание емкости

Микросхемы ОЗУ допускают наращивание емкости памяти как путем наращивания количества хранимых слов, так и путем наращивания разрядности этих слов. Наиболее простым в аппаратной реализации является второй способ – наращивание разрядности хранимых слов. На практике часто используется комбинированная структура, объединяющая наращивание как разрядности, так и количества хранимых слов. В этом случае формируется некоторое количество однотипных групп микросхем, объединенных в структуру с наращиванием разрядности слов. Далее эти группы объединяются в единую структуру с наращиванием количества хранимых слов. Разрядность слов комбинированной структуры определяется разрядностью слова одной группы микросхем, включенных по схеме наращивания разрядности. Структура с наращиванием количества хранимых слов обладает двумя недостатками. В качестве первого можно отметить более сложную аппаратную реализацию, заключающуюся в введении дополнительных дешифраторов. Второй недостаток обусловлен меньшей производительностью памяти, поскольку обмен информацией осуществляется по одной паре выводов вместо восьми пар выводов структуры с наращиванием разрядности хранимых слов. Однако структура имеет и преимущество, которое заключается в том, что она может использоваться в тех случаях, когда разрядность шины адреса превышает количество адресных входов отдельных микросхем

18. Обобщенная структура микропроцессора. Основные блоки, их значение.

Выборка (чтение) команд является автоматическимпроцессом, происходящим под воздействием импульсов от генератора тактовых импульсов (ГТИ), и не зависит от программиста в смысле механизма реализации, который жестко определяется аппаратной структурой процессора.

Дешифрация команды представляет собой процесс формирования последовательности управляющих сигналов для всех узлов процессора и других блоков вычислителя на основе информации (т.е. кода), содержащегося в команде.

Действия, выполняемые в соответствии с командой, могут представлять собой арифметическую или логическую обработку данных, пересылку данных, формирование адреса следующей команды или изменение режимов работы процессора. В любом случае эти действия определяются программистом в рамках имеющейся в его распоряжении системы команд конкретного процессора. После выполнения действий, задаваемых командой, процессор автоматически переходит к выборке следующей команды из памяти.

Современные микропроцессоры существенно различаются набором функциональных блоков и связями между ними. Тем не менее, в структуре любого процессора можно выделить основные элементы, определяющие специфику процессора как управляющего центра вычислителя. Прежде всего, речь идет о двух блоках: устройстве управления и операционном устройстве.

Устройство управления (УУ) предназначено для реализации выборки команд, их дешифрации, и на основе этого – для управления обменом и обработкой информации путем генерации последовательности управляющих сигналов.

Операционное устройство (ОУ) служит для обработки цифровой информации (арифметические и логические операции, сдвиги, анализ чисел и т.п.).

Основным элементом для хранения информации внутри процессора являются регистры, которые выполняют функцию сверхоперативного ОЗУ с минимальным временем записи и считывания.

Регистр команд РгК (англ. IR - insructionregister) используется для фиксации кода команды после считывания ее из памяти. Как правило, в этом регистре фиксируется лишь код операции(КОП) - часть кода команды, определяющая выполняемое действие и способ адресации операндов (см. ниже).

Регистры операндов служат для хранения данных в процессе их обработки, позволяют избегать постоянных обращений к памяти. В современных процессорах количество регистров операндов может достигать 10-15 штук. По сути, они образуют внутреннюю память процессора. В однокристальных микроконтроллерахколичество регистров операндов доведено до нескольких десятков, и применительно к ним вводится понятие регистрового файла. Некоторые из регистров операндов могут использоваться также для хранения или формирования адресов других операндов, т.е. на их основе реализуется механизм косвенной адресации данных в памяти(см. ниже). Данные, размещенные в регистрах операндов, поступают на обработку в арифметико-логическое устройство (АЛУ). В некоторых типах процессоров один из регистров операндов всегда является и приемником результата операции в АЛУ – такой регистр принято называть регистром-аккумулятором.Процессоры, в которых принята схема выполнения операций в виде:

<аккумулятор> (операция) <операнд> Þ <аккумулятор>,

называются процессорами с аккумуляторно-ориентированной структурой.

Счетчик команд (англ. PC - programmingcounter) - регистр, в котором при выборке или выполнении текущей команды формируется адрес следующей команды. Модификация содержимого регистра PC – это средство управления последовательностью выборки команд из памяти и, следовательно, управления ходом вычислительного процесса (т.е. реализация ветвлений в алгоритмах).

Указатель стека (англ. SP - stackpointer ) - регистр, в котором при выполнении программы хранится адрес границы той области памяти, для которой программист использует принцип последовательного доступа к данным (так называемый протокол работы со стеком).

Регистр адреса - регистр, в котором формируется адрес любого устройства, внешнего по отношению к процессору (ячейки памяти или порта ввода-вывода), перед обращением к этому устройству. Данный регистр необходим, поскольку источником адресной информации могут являться различные регистры процессора. При этом регистр адреса играет роль накапливающего буфера, из которого адресная информация выдается на внешнюю шину адреса.

Регистр признаков (англ. F - flags) - это элемент внутренней памяти, в котором в виде отдельных битов фиксируются признаки, характеризующие результат операции, выполненной в АЛУ (нулевой результат, переполнение разрядной сетки и т.п.).

Арифметико-логическое устройство (АЛУ) - функциональный блок процессора, предназначенный для реализации действий по обработке данных.

Арифметико-логическое устройство (АЛУ) служит для обработки данных. В зависимости от вида выполняемой операции АЛУ оперирует одним или двумя словами и в своем составе имеет:

- четырехразрядные сумматоры – вычитатели;

- логические элементы для выполнения операций: логического умножения, логического сложения, инверсии, исключающее ИЛИ и т.д.;

- два входных порта, один выходной порт, которые являются буферными регистрами, способным хранить одно слово данных.

Два входных порта позволяют АЛУ принимать данные с внутренней шины данных микропроцессора, или из аккумулятора (специального регистра). Выходной порт служит для пересылки данных в аккумулятор.

Основные операции АЛУ:сложение, вычитание, И, ИЛИ, исключающее ИЛИ, инверсия, сдвиг вправо, сдвиг влево, приращение положительное, приращение отрицательное.

АЛУ производятся в виде микросхем с числом разрядов: 4, 6, 8, 16. Чаще всего используются восьмиразрядные АЛУ, которые имеют 8 входов для первого слова, 8 входов для второго слова и 8 выходов, подключенных к восьми проводной шине.

Результат операции, выполненной в АЛУ, заносится в один из регистров или пересылается в память (в зависимости от команды). В регистре признаков автоматически формируются признаки, характеризующие этот результат.

Функционирование процессора всегда синхронизируется от внешнего генератора тактовых импульсов (ГТИ). Именно под влиянием импульсов от ГТИ устройство управления процессора автоматически реализует действия, связанные с выборкой команд из памяти и их дешифрацией.

Выполнение команды всегда занимает некоторое количество периодов тактовой частоты и состоит из последовательности элементарных действий процессора (выборка команды, чтение операнда, вычисление в АЛУ). Эти элементарные действия называют машинными циклами (МЦ). В течение каждого МЦ происходит генерация строго определенной комбинации управляющих сигналов для соответствующих узлов процессора и всей вычислительной системы

19. РОНы микропроцессора Cortex-M3

в ядре Cortex-M3 имеется 13 регистров общего назначения — R0-R12, регистр, используемый для хранения указателя стека, — R13, регистр связи — R14, счётчик команд — R15 и 5 регистров специального назначения.

Первые 13 регистров с точки зрения архитектуры являются абсолютно равноправными, за исключением двух моментов:

§ в командах набора ARM LDRD и STRD, оперирующих сразу парой регистров, указывается всегда регистр с чётным номером, а пару с ним составляет следующий за ним регистр с нечётным номером (заметим, что в аналогичных командах набора Thumb-2 это правило не действует: оба используемых регистра указываются в них явным образом);

§ в почти всех командах набора Thumb и в некоторых командах Thumb-2 могут использоваться регистры R0–R7, но не могут регистры с большими номерами

Регистры общего назначения разделяются на младшие регистры — R0-R7 и старшие регистры — R8-R12. Разница между ними в том, что некоторые 16-тибитные команды набора thumb-2 умеют работать только с младшими регистрами, а со старшими — не умеют.

Регистров R13 вообще-то говоря два, а не один. Первый называется MSP — указатель основного стека, а второй PSP — указатель стека процесса. Однако в каждый момент доступен только один из этих регистров. Какой именно — определяется в одном из регистров специального назначения. Зачем такое надо? Это сделано для возможности организации защиты операционной системы (ага, на этот контроллер можно поставить ОС, если хочется) от кривых прикладных программ. MSP используется обработчиками исключительных ситуаций и всеми программами, использующими привилегированный уровень выполнения (например ядро ОС), а PSP — используется программами, не требующими привилегированного уровня выполнения (например, прикладными программами от которых мы хотим защитить ядро ОС). Указатели стека всегда должны быть выровнены на границу 32-х битного слова, т.е. два их младших бита всегда должны быть сброшены в ноль.

Регистр R14 называется LR (linkregister) — регистрсвязи и используется для запоминания адреса возврата при вызове подпрограмм.

Регистр R15 называется PC (programcounter)— счётчик команд и используется для хранения адреса текущей выполняемой команды

20. Организация и использование стека в микропроцессоре Cortex-M3

Стек - запоминающее устройство с последовательным доступом, работающее по принципу - данные, записанные последними, считываются первыми

В Cortex-M3 имеется два указателя стека со следующими предназначениями:

1)MSP (MainStackPointer)— используется в обработчиках прерываний либо во всей программе.

2)PSP (ProcessStackPointer)— используется только в задачах (процессах) и не может использоваться в обработчиках прерываний. Хотя регистр R13 (указатель стека) один, коды команд (0xF3EF8009) и(0xF3EF8008) различны, хотя и работают с одним регистром.

Эти различия в кодах команд и говорят, с каким указателем стека работать через регистр R13, то есть из какого банка его выбрать (значение MSP либо PSP). Раз у обработчика прерывания свой указатель стека, а узадачи свой, проиллюстрируем более подробно процесс работы со стеком во время переключения контекста с помощью рис.4 и 5.Как видно нарис.4, в режиме потока (задачи) используется указатель PSP, в момент системного вызова происходит сохранение R0–R3, R12, LR, PC и PSR с адреса памяти, на который указывает PSP. Обработчик прерывания работает с указателем MSP, поэтому не влияет на PSP, при этом указатель PSP доступен в обработчике прерываний. Здесь его иможно подменить на значение, ссылающееся на контекст второй задачи, для которой будет произведено восстановление.На рис.5 стрелкой показано изменение значения указателя PSP.В момент времени 1 процессор выполняет задачу No1— SimpleTask1, голубым цветом указано значение указателя стека PSP. В момент возникновения прерывания, начиная с адреса (PSP-0x00000004), происходит автоматическое сохранение регистров R0–R3, R12, LR, PC, PSR.Наступает момент времени No2, в нем используется указатель стека MSP для собственной работы обработчика.

Эти различия в кодах команд и говорят, с каким указателем стека работать через регистр R13, то есть из какого банка его выбрать (значение MSP либо PSP). Раз у обработчика прерывания свой указатель стека, а узадачи свой, проиллюстрируем более подробно процесс работы со стеком во время переключения контекста с помощью рис.4 и 5.Как видно нарис.4, в режиме потока (задачи) используется указатель PSP, в момент системного вызова происходит сохранение R0–R3, R12, LR, PC и PSR с адреса памяти, на который указывает PSP. Обработчик прерывания работает с указателем MSP, поэтому не влияет на PSP, при этом указатель PSP доступен в обработчике прерываний. Здесь его иможно подменить на значение, ссылающееся на контекст второй задачи, для которой будет произведено восстановление.На рис.5 стрелкой показано изменение значения указателя PSP.В момент времени 1 процессор выполняет задачу No1— SimpleTask1, голубым цветом указано значение указателя стека PSP. В момент возникновения прерывания, начиная с адреса (PSP-0x00000004), происходит автоматическое сохранение регистров R0–R3, R12, LR, PC, PSR.Наступает момент времени No2, в нем используется указатель стека MSP для собственной работы обработчика.

Вмомент времени No3 обработчик изменяет указатель PSP со значения 0x20000094 на 0x200000D4. Во время выхода из прерывания возврат производится по новому указателю стека PSP=0x200000D4, начиная с которого процессор восстанавливает регистры R0–R3, R12, LR, PC, PSR.Поскольку это стек задачи SimpleTask2, внем будет храниться значение счетчика команд (PC) для задачи No2 и возврат произойдет уже в задачу No2. Это и будет конечный момент времени No4. Желтым цветом выделено место для сохранения вручную регистров R4–R11в обработчике прерывания.Для упрощения на рис.5 были изображены стеки задач минимальной длины, но так как задача может содержать вызовы функций, глубина стека может быть больше, ведь необходимо хранить информацию, куда вернуться после обработки вызванной функции. Для установки глубины стека в планировщике предусмотрена специальная константа, пока назовем ее «размер_стека». Она будет определять размер стека для каждой из задач. Так как каждой задаче необходим стек, число стеков будет равно числу задач. Было рассмотрено, что обработчик подменил указатель PSP на значение, соответствующее задаче SimpleTask2. Помимо стеков задач необходимо хранить текущие значения указателей PSP, так как указатель PSP может изменять свое значение впределах адресного пространства стека задачи, ведь нужно знать, где именно остановилась каждая задача вмомент ее прерывания и переключения на другую задачу.Для хранения стеков задач организован массив стеков, для хранения указателей— массив указателей стеков, взаимоотношения между массивами отображены на рис.6. В массиве указателей стеков хранятся значения PSP намомент входа в обработчик прерывания. Именно обработчик сохраняет значение PSP (например, для задачи 1) в массив указателей, берет новое значение PSP из массива указателей (например, для задачи 2), завершает прерывание с восстановлением нового контекста. Такая структура хранения информации о задачах используется впланировщике

Дата добавления: 2018-08-06; просмотров: 769; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!