Режим управления выходом регистра.

Белорусский государственный университет информатики и радиоэлектроники

Кафедра ЭВМ

Отчет по лабораторной работе № 4

«Параллельный исдвиговый регистры»

| Проверил: Байрак С. А. |

| Выполнили: студенты группы 05050x ololo |

Минск 2012

Цель работы

- Изучить режимы работы параллельного регистра.

- Изучить режимы работы регистра сдвигов.

Краткие теоретические сведения

Регистр — последовательное логическое устройство, используемое для хранения n-разрядных двоичных слов (чисел) и выполнения преобразований над ними.

Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами.

Фактически любое цифровое устройство можно представить в виде совокупности регистров, соединённых друг с другом при помощи комбинационных цифровых устройств.

Основой построения регистров являются D-триггеры, RS-триггеры.

По типу приёма и выдачи информации различают 3 типа регистров:

- С последовательным приёмом и выдачей информации — сдвиговые регистры.

- С параллельным приёмом и выдачей информации — параллельные регистры.

- С параллельно-последовательным приёмом и выдачей информации.

|

|

|

Параллельные регистры

В параллельных (статических) регистрах схемы разрядов не обмениваются данными между собой. Общими для разрядов обычно являются цепи тактирования, сброса/установки, разрешения выхода или приема, то есть цепи управления. Пример схемы статического регистра, построенного на триггерах типа D с прямыми динамическими входами, имеющего входы сброса и выходы с третьим состоянием, управляемые сигналом EZ.

Сдвигающие (последовательные) регистры

Последовательные (сдвигающие) регистры представляют собою цепочку разрядных схем, связанных цепями переноса. В однотактных регистрах со сдвигом на один разряд вправо слово сдвигается при поступлении синхросигнала. Вход и выход последовательные (DSR – Data Serial Right).

Согласно требованиям синхронизации в сдвигающих регистрах, не имеющих логических элементов в межразрядных связях, нельзя применять одноступенчатые триггеры, управляемые уровнем, поскольку некоторые триггеры могут за время действия разрешающего уровня синхросигнала переключиться неоднократно, что недопустимо. Появление в межразрядных связях логических элементов, и тем более, логических схем неединичной глубины упрощает выполнение условий работоспособности регистров и расширяет спектр типов триггеров, пригодных для этих схем. Многотактные сдвигающие регистры управляются несколькими синхропоследовательностями. Из их числа наиболее известны двухтактные с основным и дополнительным регистрами, построенными на простых одноступенчатых триггерах, управляемых уровнем. По такту С1 содержимое основного регистра переписывается в дополнительный, а по такту С2 возвращается в основной, но уже в соседние разряды, что соответствует сдвигу слова. По затратам оборудования и быстродействию этот вариант близок к однотактному регистру с двухступенчатыми триггерами.

|

|

|

Выполнение работы.

Параллельный регистр.

Параллельный регистр в статическом режиме.

Режим параллельной загрузки и хранения.

При подаче управляющих сигналов Р1=Р2=0 происходит параллельная загрузка, при остальных комбинациях регистр находится в режиме хранения информации.

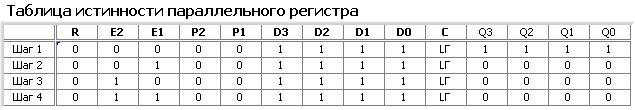

Режим управления выходом регистра.

Считывание информации из регистра происходит при значениях на входах Е1=Е2=0.

Дата добавления: 2018-06-01; просмотров: 651; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!