Регистр С управления и статуса УСАПП - UCSRnC

|

Обратите внимание, что данный регистр не доступен в режиме совместимости с ATmega103.

- Разряд 7 - Резервный бит

Данный бит зарезервирован для будущего использования. Однако для совместимости с будущими микроконтроллерами при записи в регистр UCSRnC в позицию данного бита необходимо записывать лог. 0.

- Разряд 6 - UMSELn: Выбор режима УСАПП

Данный бит позволяет переключаться между синхронным и асинхронными режимами последовательной связи.

Таблица 77. Установки бита UMSELn

|

Разряды 5:4 - UPMn1:0: Режим паритета

Данные бита разрешают и устанавливают тип генерируемого и контролируемого паритета. После разрешения паритета передатчик автоматически генерирует и передает бит паритета в каждой посылке. Приемник генерирует бит паритета для принятых данных и сравнивает его со значением принятого в этой посылке бита паритета, а по результату сравнения устанавливает флаг ошибки паритета UPEn в регистре UCSRnA.

Таблица 78. Установки бит UPMn

|

Разряд 3 - USBSn: Выбор числа стоп-бит

Данный бит определяет сколько стоповых бит вставляет передатчик при генерации посылки. Приемник игнорирует эту настройку.

Таблица 79. Установки бита USBSn

|

Разряды 2:1 - UCSZn1:0: Формат данных

Биты UCSZn1:0 вместе с UCSZn2 в регистре UCSRnB задают количество бит данных в посылке, как для приемника, так и для передатчика.

Таблица 80. Установки бит UCSZn

|

Разряд 0 - UCPOLn: Полярность синхронизации

Данный бит используется только в синхронном режиме. Если используется асинхронный режим, то в данный бит необходимо записать лог. 0. В синхронном режиме бит UCPOLn определяет соотношение между выборкой входящих данных и обновлением передаваемых данных и сигналом тактирования синхронной связи (XCKn).

Таблица 81. Установки бит UCPOLn

|

Регистры скорости связи УСАПП - UBRRnL и UBRRnH

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Регистр UBRRnH не доступен в режиме совместимости с mega103

- Разряды 15:12 -Зарезервированные разряды

Данные разряды зарезервированы для будущего использования. Для совместимости с последующими разработками необходимо записать лог. 0 в эти разряды во время записи в регистр UBRRnH.

- Разряды 11:0 - UBRRn11:0: Регистр скорости связи УСАПП

UBRR - 12-разр. регистр, который задает значение скорости связи УСАПП. Регистр UBRRnH содержит 4 старших разряда, а UBRRnL 8 младших разрядов значения скорости УСАППn. Если во время передачи или приема изменить скорость связи, то сеанс связи будет нарушен. Запись в регистр UBRRnL инициирует обновление предделителя скорости связи.

18. Особенности интерфейса SPI в ATmega128

Интерфейс SPI позволяет организовать последовательную синхронную высокоскоростную передачу данных между ATmega128 и другим периферийным устройством или между несколькими AVR-микроконтроллерами.

Отличительные особенности интерфейса SPI в ATmega128:

- Полнодуплексная, трехпроводная синхронная передача данных

- Ведущая или подчиненная работа

- Передача первым младшего или старшего бита

- Семь программируемых скоростей связи

- Флаг прерывания для индикации окончания передачи данных

- Защитный флаг при повторной записи

- Пробуждение из режима холостого хода (Idle)

- Режим ведущего (мастера) SPI с удвоением скорости (CK/2)

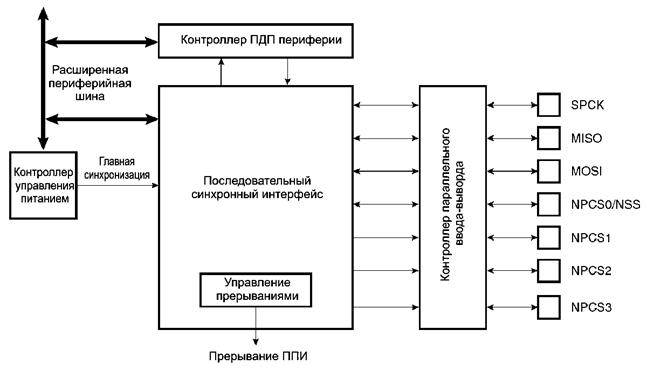

Рисунок 75. Функциональная схема интерфейса SPI

Прим.: Расположение выводов интерфейса SPI представлено на рис. 1 и в таблице 30.

Внешние соединения между ведущим (мастером) и подчиненным ЦПУ через интерфейс SPI показаны на рисунке 76. Система состоит из двух сдвиговых регистров и генератора ведущей синхронизации. Ведущий SPI инициирует сеанс связи подачей низкого уровня на вход SS того подчиненного устройства, с которым необходимо обмениваться данными. Оба респондента (ведущий и подчиненный) подготавливают данные к передаче в своем сдвиговом регистре, при этом на стороне ведущего генерируются также импульсы синхронизации на линии SCK. По линии MOSI всегда осуществляется передача данных от ведущего к подчиненному, а по MISO, наоборот, от подчиненного к мастеру. По окончании передачи каждого пакета данных ведущий SPI должен засинхронизировать подчиненный путем подачи высокого уровня на линию SS (выбор подчиненного интерфейса).

Если SPI настроен как ведущий (мастер), то управление линией SS происходит не автоматически. Данная операция должна быть выполнена программно перед началом сеанса связи. После этого, запись в регистр данных SPI инициирует генерацию синхронизации и аппаратный сдвиг 8-ми разрядов в подчиненное устройство. По окончании сдвига одного байта генератор синхронизации SPI останавливается, при этом устанавливая флаг окончания передачи (SPIF). Если установлен бит SPIE в регистре SPCR, то разрешается прерывание SPI и по окончании передачи байта будет генерирован запрос на прерывание. Мастер может продолжить сдвигать следующий байт, если записать его в регистр SPDR, или подать сигнал окончания пакета путем установки низкого уровня на линии SS. Последний принятый байт сохраняется в буферном регистре. В режиме подчиненного, интерфейс SPI находится в состоянии ожидания, в котором MISO переводится в третье состояние, до тех пор, пока на выводе SS присутствует высокий уровень. В этом состоянии программа может обновлять содержимое регистра данных SPI (SPDR), но при этом входящие импульсы синхронизации не сдвигают данные до подачи низкого уровня на вывод SS. После того как один байт был полностью сдвинут, устанавливается флаг окончания передачи SPIF. Если установлен бит разрешения прерывания SPI (SPIE) в регистре SPCR, то установка флага SPIF приводит к генерации запроса на прерывание. Подчиненный может продолжать размещать новые данные для передачи в регистр SPDR перед чтением входящих данных. Последний принятый байт хранится в буферном регистре.

Рисунок 76. Внешнее соединение ведущего (мастера) и подчиненного SPI

В направлении передачи данных система выполнена как однобуферная, а в направлении приема используется двойная буферизация. Это означает, что передаваемые байты не могут быть записаны в регистр данных SPI, прежде чем полностью завершится цикл сдвига. Во время приема данных необходимо следить, чтобы принятая посылка была считана из регистра данных SPI, прежде чем завершится цикл входящего сдвига новой посылки. В противном случае первый байт будет потерян.

В подчиненном режиме SPI управляющая логика осуществляет выборку входящего сигнала SCK. Чтобы гарантировать корректность выборки тактового сигнала необходимо использовать частоту синхронизации SPI не более fosc/4.

Если работа SPI разрешена, то разрешается альтернативное направление выводов MOSI, MISO, SCK и SS (см. табл. 69).

Таблица 69. Направление выводов SPI(1)

|

Прим.1: См. "Альтернативные функции порта B", где подробно описано как установить направление на выводах порта SPI.

В следующих примерах показаны инициализация SPI как мастера и организация простой передачи данных. В данных примерах DDR_SPI должен быть заменен на имя фактического регистра направления данных, управляющий выводами интерфейса SPI (для ATmega128 DDRB). DD_MOSI, DD_MISO и DD_SCK также должны быть заменены на имена соответствующих бит регистров направления данных, связанных с этими выводами. Например, если MOSI размещен на выв. PB5, то DD_MOSI необходимо заменить на DDB5, а DDR_SPI на DDRB.

|

|

Прим.1: В примерах предполагается, что подключен файл специфических заголовков.

В следующем примере показано как инициализировать SPI как подчиненного и как выполнить простой прием данных.

|

Прим.1: В примерах предполагается, что подключен файл специфических заголовков

19. Ведущий режим, режимы передачи данных интерфейса SPI

Ведущий режим

Если SPI настроен как мастер (установлен бит MSTR в SPCR), то пользователь может задать желаемое направление вывода SS.

Если SS настроен на вывод, то он работает как обычная линия цифрового вывода и не оказывает влияния на систему SPI. Обычно он используется для управления выводом SS подчиненного SPI.

Если SS настроить как вход, то на нем должен присутствовать высокий лог. уровень, чтобы гарантировать работу ведущего SPI. Если SPI настроен как мастер, у которого выв. SS настроен как вход, то подача на этот вход низкого уровня внешней схемой будет интерпретирована как перевод в подчиненный режим по запросу другого ведущего SPI, после чего начнется передача данных. Для того чтобы избежать конфликтной ситуации система SPI выполняет следующие действия:

- SPI переводится в подчиненный режим сбросом бита MSTR в регистре SPCR. В результате SPI становится подчиненным, а MOSI и SCK конфигурируются как входы.

- Устанавливается SPIF в SPSR и, если разрешено прерывание SPI и установлен бит I в регистре SREG, то выполняется процедура обработки прерывания.

Таким образом, если используется передача SPI в режиме мастера с управлением по прерываниям и предусмотрена возможность подачи низкого уровня на вход SS, то при генерации прерывания необходимо всегда проверять состояние бита MSTR. Если MSTR оказался сброшенным, то это означает, что SPI был переведен в подчиненный режим внешним устройством и пользователь должен предусмотреть возобновление ведущего режима SPI программным путем.

Режимы передачи данных

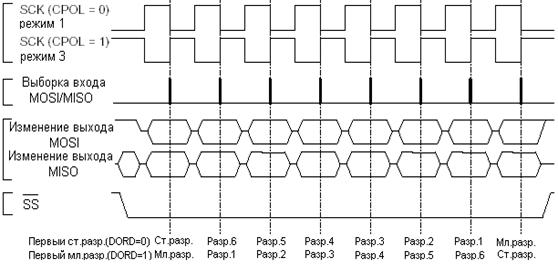

Комбинация бит CPHA и CPOL задает четыре возможных режима последовательной передачи данных. Форматы передачи данных для SPI представлены в таблице 73, а их временные диаграммы показаны на рис. 77 и 78. Биты данных выводятся сдвигом и фиксируются на входе противоположными фронтами синхросигнала SCK, тем самым гарантируя достаточное время на установление сигналов данных. Таким образом, можно обобщить информацию из табл. 70 и 71 и представить ее в следующем виде:

Таблица 73. Функциональные возможности CPOL и CPHA

| Передний фронт | Задний фронт | Режим SPI | |

| CPOL = 0, CPHA = 0 | Выборка нарастающим фронтом | Установка данных падающим фронтом | 0 |

| CPOL = 0, CPHA = 1 | Установка данных нарастающим фронтом | Выборка падающим фронтом | 1 |

| CPOL = 1, CPHA = 0 | Выборка падающим фронтом | Установка данных нарастающим фронтом | 2 |

| CPOL = 1, CPHA = 1 | Установка данных падающим фронтом | Выборка нарастающим фронтом | 3 |

Рисунок 77. Формат передачи данных SPI с CPHA = 0

Рисунок 78. Формат передачи данных SPI с CPHA = 1

20. Последовательный периферийный интерфейс – SPI. Регистр статуса, регистр данных

Схемы последовательного периферийного интерфейса обеспечивают синхронную последовательную связь, обеспечивающую передачу данных во внешние устройства в режиме ведущего и ведомого. В том случае, если в системе присутствует внешний процессор, с помощью этого интерфейса может быть обеспечена межпроцессорная связь.

Аппаратная часть последовательный периферийный интерфейс по существу представляет собой сдвиговый регистр, который последовательно выдвигает биты данных в другие аналогичные интерфейсы прочих устройств. Во время процесса передачи одно из устройств работает как ведущее, обеспечивая контроль над потоком данных, в то время как другие, ведомые устройства, принимают или передают данные под управлением ведущего. Функции ведущего устройства интерфейса могут передаваться от одного процессора другому (мультимастерный протокол по сравнению с одномастерным, когда только один процессор всегда работает в качестве ведущего, а все остальные в качестве ведомых), и ведущее устройство может вести передачу одних и тех же данных нескольким ведомым устройствам одновременно. Тем не менее, в текущий момент времени только одно ведомое устройство может осуществлять передачу данных ведущему.

Ведомое устройство выбирается, когда ведущее выдает сигнал NSS. Если присутствуют одновременно несколько ведомых устройств, ведущее вырабатывает раздельные сигналы выбора для каждого из них (NPSC).

Система SPI состоит из двух линий данных и двух линий управления:

- Из ведущего в ведомое (Master Out Slave In) Эта линия обеспечивает побитную выдачу данных со сдвигом из ведущего и передачу на прием ведомого.

- Из ведомого в ведущее (Master In Slave Out) Эта линия обеспечивает передачу данных с выхода ведомого на вход ведущего. Во время каждой отдельно взятой передачи линию может занимать только одно ведомое устройство.

- Тактовый сигнал последовательной передачи (Serial Clock - SPCK). Состояние этой линии управляется ведущим устройством и регулирует (синхронизирует) передачу бит данных. Ведущее устройство управляет скоростью передачи данных и может задавать различные скорости передачи, каждый период сигнала SPCK соответствует передаче одного бита данных.

- Выбор ведущего (NSS): Эта линия управления позволяет аппаратно включать и выключать ведомые устройства.

Дата добавления: 2018-05-13; просмотров: 317; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!