Реальный и защищенный режимы работы процессора

Математический сопроцессор — сопроцессор для расширения командного множества центрального процессора и обеспечивающий его функциональностью модуля операций с плавающей запятой, для процессоров, не имеющих интегрированного модуля. Модуль операций с плавающей запятой (или с плавающей точкой; англ. floating point unit (FPU)) — часть процессора для выполнения широкого спектра математических операций над вещественными числами. Простым «целочисленным» процессорам для работы с вещественными числами и математическими операциями требуются соответствующие процедуры поддержки и время для их выполнения. Модуль операций с плавающей запятой поддерживает работу с ними на уровне примитивов — загрузка, выгрузка вещественного числа (в/из специализированных регистров) или математическая операция над ними выполняется одной командой, за счёт этого достигается значительное ускорение таких операций. 3. Основой любого метода управления процессами является организация очередей процессов и ресурсов. Задача подбора множества процессов, для которого количество конфликтов из-за ресурсов при их выполнении будет минимальным, называется задачей планирования вычислительных процессов. Она может быть решена оптимально только на некотором множестве начальных состояний процессов. С изменением состояний процессов принятое решение по планированию не будет оптимальным и требует корректировки. Такая корректировка может быть осуществлена на основе динамического (краткосрочного) планирования или диспетчеризации. Основное различие между краткосрочным и долгосрочным планировщиками состоит в частоте их запуска: первый запускается 1 раз в 30-100 мс, второй − 1 раз в несколько минут. Долгосрочный планировщик устанавливает и корректирует очередность готовых процессов с целью создания мультипрограммной смеси, обеспечивающей оптимальную загрузку всех ресурсов системы, а краткосрочный − выбирает очередную задачу из готовых для передачи на выполнение. Обычно в существующих системах долгосрочное планирование отсутствует 4-7. Оперативная память — это важнейший ресурс любой вычислительной системы, поскольку без нее (как, впрочем, и без центрального процессора) невозможно выполнение ни одной программы. В главе 1 мы уже отмечали, что память является разделяемым ресурсом. От выбранных механизмов распределения памяти между выполняющимися процессорами в значительной степени зависит эффективность использования ресурсов системы, ее производительность, а также возможности, которыми могут пользоваться программисты при создании своих программ. Желательно так распределять память, чтобы выполняющаяся задача имела возможность обратиться по любому адресу в пределах адресного пространства той программы, в которой идут вычисления. С другой стороны, поскольку любой процесс имеет потребности в операциях ввода-вывода, и процессор достаточно часто переключается с одной задачи на другую, желательно в оперативной памяти расположить достаточное количество активных задач с тем, чтобы процессор не останавливал вычисления из-за отсутствия очередной команды или операнда. Некоторые ресурсы, которые относятся к неразделяемым, из-за невозможности их совместного использования делают виртуальными. Таким образом, чтобы иметь возможность выполняться, каждый процесс может получить некий виртуальный ресурс. Виртуализация ресурсов делается программным способом средствами операционной системы, а значит, для них тоже нужно иметь ресурс памяти. Поэтому вопросы организации разделения памяти для выполняющихся процессов и потоков являются очень актуальными, ибо выбранные и реализованные алгоритмы решения этих вопросов в значительной степени определяют и потенциальные возможности системы, и общую ее производительность, и эффективность использования имеющихся ресурсов. Сегментная организация памяти. Понятие сегментированной памяти связано с необходимостью разделения хранимых в памяти данных между различными процессами. Страничная память — способ организации виртуальной памяти, при котором единицей отображения виртуальных адресов на физические является регион постоянного размера. Система отображения логических адресов в физические сводится к системе отображения логической страницы в физические и представляет собой таблицу страниц, которая хранится в оперативной памяти. Отображение адресов обычно реализуется аппаратно. Для ссылки на таблицу процессов используются специальные регистры, при переключении процессов необходимо найти таблицу страниц нового процесса, указатель на которую входит в контекст процесса. Существуют 2 других схемы организации управления памятью: сегментная и сегментно-страничная. сегменты в отличие от страниц могут иметь переменные размеры. При сегментной организации виртуальный адрес по-прежнему является двумерным и состоит из двух полей: номера сегмента и смещение внутри сегмента. Однако, в отличие от страничной организации, где линейный адрес преобразован в двумерный ОС для удобства отображения, здесь двухмерность адреса является следствием представления программиста о процессе не в виде линейного массива байтов, а как набор сегментов переменного размера (данные, код, стек).

|

|

|

|

|

|

|

|

|

Реальный и защищенный режимы работы процессора

|

|

|

Широко известно, что первым микропроцессором, на базе которого была создана IBM PC, был Intel 8088. Этот микропроцессор отличался от первого 16-разрядного микропроцессора фирмы Intel -- 8086 -- прежде всего тем, что у него была 8-битовая шина данных, а не 16-битовая (как у 8086). Оба эти микропроцессора предназначались для создания вычислительных устройств, которые бы работали в однозадачном режиме, то есть специальных аппаратных средств для поддержки надежных и эффективных мультипрограммных ОС в них не было.

Однако к тому времени, когда разработчики осознали необходимость включения в микропроцессор специальной аппаратной поддержки для мультипрограммных вычислений, уже было создано очень много программных продуктов. Поэтому для совместимости с первыми компьютерами в последующих версиях микропроцессоров была реализована возможность использовать их в двух режимах -- реальном (real mode -- так назвали режим работы первых 16-битовых микропроцессоров) и защищенном (protected mode -- означает, что параллельные вычисления могут быть защищены аппаратно-программными механизмами).

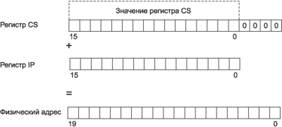

Подробно рассматривать архитектуру первых 16-битовых микропроцессоров i8086/i8088 мы не будем, поскольку этот материал должен изучаться в предыдущих дисциплинах учебного плана. Для тех же, кто с ним не знаком, можно рекомендовать такие книги, как [52, 73], и многие другие. Однако напомним, что в этих микропроцессорах (а значит, и в остальных микропроцессорах семейства i80x86 при работе их в реальном режиме) обращение к памяти с возможным адресным пространством в 1 Мбайт осуществляется посредством механизма сегментной адресации (рис. 3.1). Этот механизм был использован для увеличения количества разрядов, участвующих в указании адреса ячейки памяти, с которой в данный момент осуществляется работа, с 16 до 20 и тем самым увеличения объема памяти.

Конкретизируем задачу и ограничимся рассмотрением определения адреса команды. Для адресации операндов используется аналогичный механизм, только участвуют в этом случае другие сегментные регистры. Напомним, что для определения физического адреса команды содержимое сегментного регистра CS (code segment) умножается на 16 за счет добавления справа (к младшим битам) четырех нулей, после чего к полученному значению прибавляется содержимое указателя команд (регистр IP, instruction pointer). Получается двадцатибитовое значение, которое и позволяет указать любой байт из 220.

Рис. 3.1. Схема определения физического адреса для процессора 8086

В защищенном режиме работы определение физического адреса осуществляется совершенно иначе. Прежде всего используется сегментный механизм для организации виртуальной памяти. При этом адреса задаются 32-битовыми значениями. Кроме этого, возможна страничная трансляция адресов, также с 32-битовыми значениями. Наконец, при работе в защищенном режиме, который по умолчанию предполагает 32-битовый код, возможно исполнение двоичных программ, созданных для работы микропроцессора в 16-битовом режиме. Для этого введен режим виртуальной 16-битовой машины и 20-битовые адреса реального режима транслируются с помощью страничного механизма в 32-битовые значения защищенного режима. Наконец, есть еще один режим -- 16-битовый защищенный, позволяющий 32-битовым микропроцессорам выполнять защищенный 16-битовый код, который был характерен для микропроцессора 80286. Правда, следует отметить, что это последний режим практически не используется, поскольку программ, созданных для него, не так уж и много.

Для изучения этих возможностей рассмотрим сначала новые архитектурные возможности микропроцессоров i80x86.

Дата добавления: 2018-05-12; просмотров: 449; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!