TSM320 сериялы сиг.проц. командаларын орындау

Және 26 билет 1.Сигналдардың цифрлық өңдеуі бар құрылғының құрылымдық сұлбасы Сигналдарды цифрлық өңдеу (СЦӨ) ЭЕМ қолданылуында кешенді ғылыми-техникалық бағыт ретінде негізделеді және телекоммуникация жүйелеріндегі сигналдарды цифрлық өңдеуге арналған арнайы есептеуіш техника құралдары (Internet әлемдік желісін қоса), басқару, мультимедиа, медицина және т.б. ретінде. СЦӨ дискретті сигналдардан шығатын сандық сигналдармен де қатысы бар, олар уақыт бойынша дискретті, күйі бойынша үзіліссіз. Олар функциясымен сипатталады, мұндағы - санақ нөмірі 0,1,2,3…, Т интервалы – дискретизация периоды, ал Т кері шама - дикретизация жиілігі . 2. Жанама адресі бар TMS 320С50 сигналды процессорының командалар форматы TMS320С5х - модифицияланған Гарвардтық архитектурасына негізделетін сигналдық процессорлар. Аппаратты көбейткіш бір командалық цикл ішінде екі 16-разрядты сөздерді 32-разрядты нәтижемен қайта көбейтуді орындайды. Көбейткіш үш элементтен тұрады: өзіндік көбейткіш (multiplaer), PREG нәтижесінің регистрі (product register) және TREG0 уақытша регистрі. 16-разрядты TREG0 көбейткішті сақтайды, 32-разрядты PREG көбейткіш нәтижесін құрайды. Қолданылатын командаларға байланысты көбейткіштің мәні деректер жадысынан, бағдарлама жадысынан немесе тікелей командадан жүктелуі мүмкін. 3.TMS320С50 сигналды процессорының жадысын ұйымдастыру TMS320С5х - архитектурада жадының екі кеңістігі, яғни өзінің адрестер мен деректер шинасы бар бағдарламалар мен деректер үшін қолданылатын кеңістіктер. Бағдарламалар жадысы деректерінің шинасы бойынша бағдарламалық жадыдан командалар коды мен тікелей операндтар жіберіледі. Деректер жадысы деректерінің шинасы бойынша деректер процессордың әртүрлі модульдерінен деректер жадысына және керісінше жіберіледі. Бағдарлама жадысы мен деректер жадысы арасында деректерді алмастыру командалары болады.

|

|

|

Жане 27 билет

1. Сигналды процессорлардағы деректерді көрсету

Сигналды процессорлар (СП) – бұл қазіргі уақыттағы ақпараттық және байланыстық желі мен жүйедегі сигналдарды өңдеуі, түрлендіруі және түзілуі үшін арналған құрылғы. Олардың басты ерекшелігі – үлкен массивті мәліметтерді өңдеуі. Өңдейтін сигналдар мен СП элементті базасы түрі бойынша аналогты және сандық болып бөлінді

|

|

|

Сандық сигналды процессорлар (ССП) арнайы (программаланбайтын) өте үлкен интегралдық сұлба (ӨҮИС) немесе әмбебап ӨҮИС түрінде орындала алады. Арнайы процессорларға жатады, мысалы, Фурьенің жылдам түрлендіргіш процессоры, жиілік синтезаторы, кодер және т.б. Әмбебеп процессорларға жататындар:

1) Логикалық сұлбалар (ПЛИС – программаланатын логикалық интегралдық сұлбалар);

2) Программаланатын сандық сигналды процессорлар шет ел аббревиатурасымен аталатын DSP ( Digital Signal Processor);

3) транспьютерлер.

Әмбебап процессордың арнайы процессорға қарағанда артықшылығы кристалдың жоғары емес бағасы кезінде әртүрлі жүзеге асырылатын мүмкіншілігі болып табылады.

ССП өндірілуі мен архитектурасына бойынша үлкен ақпараттық массивтерді өңдеуді жүргізуге болатын транспьютерге біршама жақын. ТранспьютерRISC(Reduced Instruction Set Computer) архитертурасы бар процессорға ие, яғни қысқартылған команда жинағы барядро, бір секунд ішінде миллионнан асатын команда тезәрекеттілігі (MIPS) және параллель есептеуді қамтамасыз ететін аппаратты заттар. Транспьютердебасқа транспьютерлермен хабар алмасу үшін қызмет ететін төрт жоғарғы жылдамдықты байланыс каналы бар. Бұл төрт канал қиын байланысатын транспьютерлік желіні ұйымдастыра отырып, транспьютерлерді бір-бірімен байланысуға мүмкіндік береді. Транспьютерлер негізінде бөлінген жүйелер құрылады.

|

|

|

ПЛИС ССП-ға және транспьютерлерге қарағанда оңай және арзан, бірақ енгізу-шығару құрылғысы мен көптеген перифериялық құрылғыларды қажет етеді. ССП-ға қарағанда олардың шығарылымы аз.

Микропроцессор дамуының нәтижесі болған программаланатын ССПең көп таралымға ие, бірақ сандық сигналдарды өңдеу тапсырмасы үшін бейімделген архитектурасымен ерекшеленеді. ССП-ға қойылатын негізгі талаптар:

1) арифметикалық операциялардың жылдам орындалуы (жоғары тезәрекеттілік);

2) қазіргі уақыттағы үлкен көлемді есептеуі бар алгоритмді жүзеге асыру кезіндегі жоғары өндірілгіштік (алгоритм өңдеуінде көп уақыт дискретизация периоды).

|

|

|

Бұл талаптар келесідей ССП архитектуралық ерекшеліктерін қолдануы арқасында орындалуда:

1) гарвардтық архитектураны қолдану;

2) конвейерлі жұмыс режимін пайдалану;

3) арнайы көбейткіш құралы бары;

4) арнайы команда енгізілуі;

5) қысқа команда циклын ұйымдастыру

2. Жанама адресі бар ТМS 320С10 сигналды процессордың командалар форматы

ЦСП-ның бірінші буынына TMS320C1x жанұясы жатады. Бұл жанұяның мінездемелік көрсеткіші 16-разрядты TMS320C10К процессоры болып табылады, ол 200 нс-тан көп емес командалық цикл ұзақтығындағы 1 секунд ішінде 5 млн.операцияны орындауға әрекетті. Процессорда екілік толықтыру кодты жылжымалы тіркелген арифметика жүзеге асырылады. Процессор сегіз 16-разрядты енгізу порты мен сегіз 16-разрядты шығару мәліметтерін адрестейді [ 7 ].

Процессор негізіне жоғарғы икемділікпен тезәрекеттілікке жету үшін модифицияланған гарвардты архитектура қойылған, оларды командалар орындалуы мен таңдау процессі уақыты кезінде біріктіруге рұқсат етеді, және де программа жадысы мен мәліметтер жадысы арасындағы байланысты орындайды.

Программа жадысы 1536×16 разрядты көлемі бар тұрақты есте сақтау құрылғысында (ТЕСҚ)жүзеге асырылады және кристалл ішінде (TMS320C10 процессоры) және сыртында (TMS32010 процессоры) орналасуы мүмкін. Максималды тезәрекеттілік сақталуымен 4096×16 разрядты жалпы көлеміне дейін ішкі жадының үлкеюіне мүмкіншілігі бар.

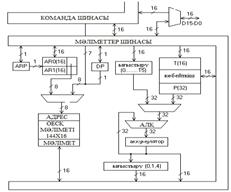

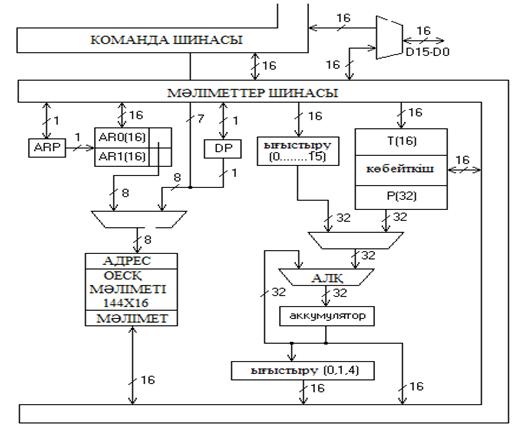

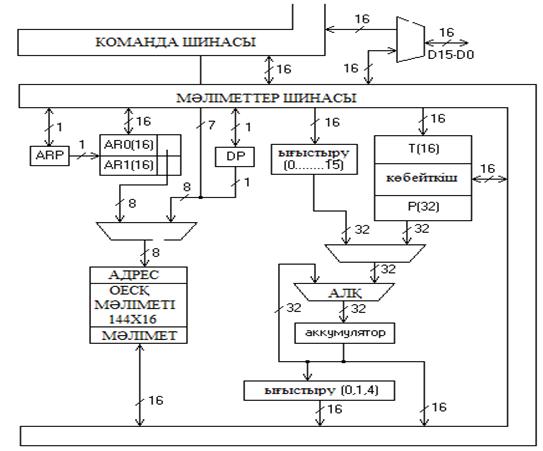

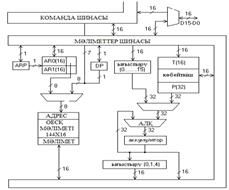

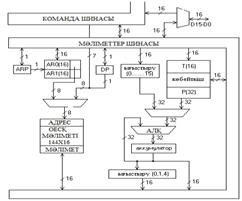

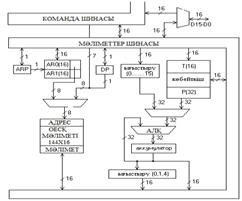

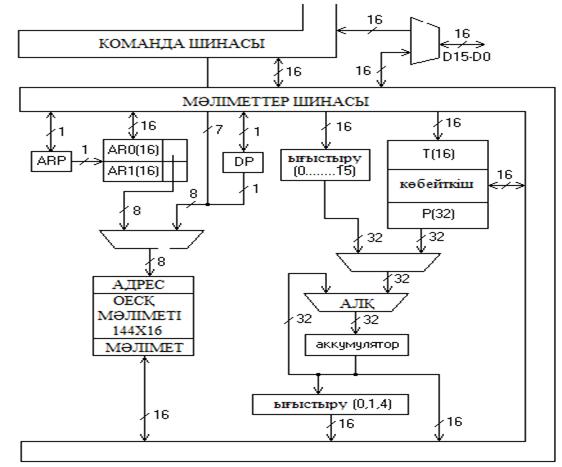

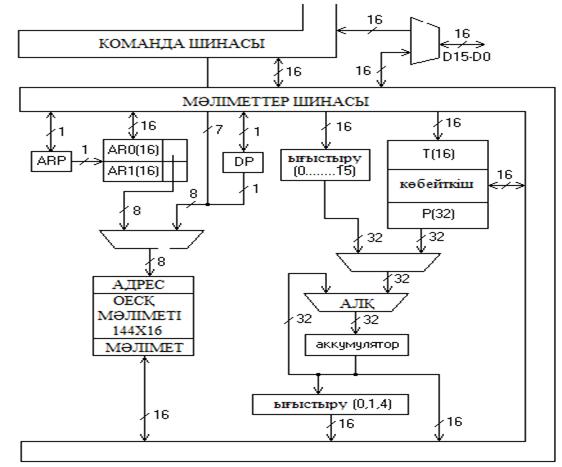

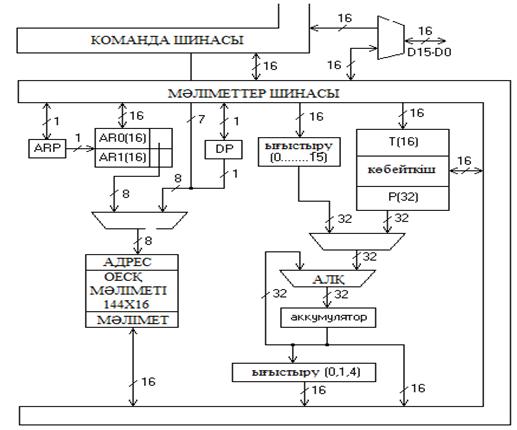

5.1 суретте TMS320C10 процессор операциялық блогының құрылымдық сұлбасы көрсетілген.

5.1 сурет

5.1 суретте көрсетілгендей, процессордың құрамында көлемі 288 байт оперативті есте сақтау құрылғысын (ОЕСҚ) және төрт негізгі арифметикалық түйіні: арифметикалық-логикалық құрылғы (АЛҚ), аккумулятор, көбейткіш және ығысу құрылғысын қамтитын мәліметтер жадысы бар.

Қосалқы адресация режимінде мәліметтер жадысының адресі ретінде сегіз кіші разрядты қосымша регистрдің (ARO немесе AR1) бірі қолданылады. Осы қосымша регистр нұсқаушы қосымша регистр (ARP) көмегімен таңдала- ды. Мәліметтерді уақытша сақтау үшін немесе циклдарды ұйымдастыру үшін ортақ регистр ретінде қосымша 16-разрядты регистрларды қолдануға болады.

, егер [40]

, егер [40]  есептеу үшін бағдарламаның фрагментін құру

есептеу үшін бағдарламаның фрагментін құру

Жане 28 билет

1.Сигналды процессорлардағы сандар мен сигналдарды кванттау

Квантталу – сызықты емес операция, сол себепті сызықты дискретті өрнекпен өрнектелетін сигналдарды өңдеу алгоритміне енгізген кезінде алгоритмді жүзеге асыруда қателіктер пайда болады.

Сандардың квантталуы – бұл оның мәнді разрядты соңғы саны (b) көмегімен көрсетілімі. Мәнді разрядты ескере отырып сандар разрядты- лығы былай анықталады  . Квантталу операциясының сызықты еместігі квантталатын санға А қателігін енгізеді

. Квантталу операциясының сызықты еместігі квантталатын санға А қателігін енгізеді

, (3.1)

, (3.1)

мұндағы А – квантталуға дейінгі екілік сан;

F(A) – квантталудан кейінгі сан.

квантталу қадамы деп екі көрші квантталу деңгейі арасындағы арақашықтықты айтады,

квантталу қадамы деп екі көрші квантталу деңгейі арасындағы арақашықтықты айтады,  Квантталу қадамы кішкентай мәнді разряд салмағымен анықталады:

Квантталу қадамы кішкентай мәнді разряд салмағымен анықталады:  .

.

Сандық өңдеуде модулі бойынша бірліктен аспайтын сандар ғана қарастырылады

(3.2)

(3.2)

Квантталу кезінде сандар жақындауының екі әдісі қолданылады: дөңгелектеу және қиылысу. Дөңгелектеу кезінде квантталудың жақын деңгейі таңдалады, бұл кезде бастапқы k-разрядты сан ( k>b ) жақын b-разрядқа ауыстырылады және  дөңгелектеу қателігі квантталудың жартылай қадамынан аспайды

дөңгелектеу қателігі квантталудың жартылай қадамынан аспайды

(3.3)

(3.3)

k- разрядты санның bмәнді разрядына дейін (k>b)қиылысу кезінде кіші (k - b)разрядты баспатқы мәндер алынып тасталынады.  қиылысу қателігі квантталу қадамынан кіші, бірақ дөңгелектеу қателігінен үлкен

қиылысу қателігі квантталу қадамынан кіші, бірақ дөңгелектеу қателігінен үлкен

<

<  (3.4)

(3.4)

Осыған байланысты аналогты-цифрлық түрлендіруде және сандық процессордағы сигналдарды өңдеуде әдетте дөңгелектеу қолданылады.

2.TMS320C10 сигналды процессорының техникалық сипаттамасын беру.

ЦСП-ның бірінші буынына TMS320C1x жанұясы жатады. Бұл жанұяның мінездемелік көрсеткіші 16-разрядты TMS320C10К процессоры болып табылады, ол 200 нс-тан көп емес командалық цикл ұзақтығындағы 1 секунд ішінде 5 млн.операцияны орындауға әрекетті. Процессорда екілік толықтыру кодты жылжымалы тіркелген арифметика жүзеге асырылады. Процессор сегіз 16-разрядты енгізу порты мен сегіз 16-разрядты шығару мәліметтерін адрестейді. Программа жадысы 1536×16 разрядты көлемі бар тұрақты есте сақтау құрылғысында (ТЕСҚ)жүзеге асырылады және кристалл ішінде (TMS320C10 процессоры) және сыртында (TMS32010 процессоры) орналасуы мүмкін. Максималды тезәрекеттілік сақталуымен 4096×16 разрядты жалпы көлеміне дейін ішкі жадының үлкеюіне мүмкіншілігі бар.

5.1 суретте TMS320C10 процессор операциялық блогының құрылымдық сұлбасы көрсетілген.

5.1 сурет

5.1 суретте көрсетілгендей, процессордың құрамында көлемі 288 байт оперативті есте сақтау құрылғысын (ОЕСҚ) және төрт негізгі арифметикалық түйіні: арифметикалық-логикалық құрылғы (АЛҚ), аккумулятор, көбейткіш және ығысу құрылғысын қамтитын мәліметтер жадысы бар.

АЛҚ32-разрядты сөздердің қосу, азайту және логикалық операцияларын орындауға негізделген. Бір операнды аккумулятордан алынады, екіншісі не көбейткіш өндіретін регистрдан (Р) не 0-15 разрядқа солға ығысу тізбегінің мүмкіндігімен ішкі мәліметтер шинасынан алынады. Операция нәтижесі аккумуляторға енгізіледі. Параллельді ығысу құрылғысы (0,1,4 ығысуы) өндіруші нәтиженің масштабталуы үшін мәліметтер жадысына аккумулятордың үлкен разрядтарымжазылуы кезінде қолданылады.

Мультиплексор (MS) арқылы процессор адрестеудің екі әдісінің бірін қолдана алады: тікелей және қосалқы. Бірінші әдіс кезінде ұяшық жадысының адресі команданың жеті кіші разрядты сөзінен және бетті (DP) көрсететін бір разрядтан құрылады. 5.2 суретте көрсетілгендей, мәліметтер жадысы сұлба бойынша топтарға бөлінеді.

3. z = 9x, егер [10] x. есептеу үшін бағдарламаның фрагментін құру.

3. z = 9x, егер [10] x. есептеу үшін бағдарламаның фрагментін құру.

Жане 29 билет

1.Цифрлық жүйе мен сигнал/шуылдың динамикалық диапазоны.

Сигнал/шуыл қатынасы және оның динамикалық диапазоны сандық жүйеде басты шуылдық мінездемесі болып табылады.  сигнал/шуыл қатынасы – бұл

сигнал/шуыл қатынасы – бұл  жүйенің шығыс сигналы қуатының

жүйенің шығыс сигналы қуатының  жүйе шығысындағы шуыл қуатына қатынасы

жүйе шығысындағы шуыл қуатына қатынасы

[дБ]. (3.10)

[дБ]. (3.10)

динамикалық диапазон –бұл

динамикалық диапазон –бұл  максималды амплитудасының кіріс сигналының

максималды амплитудасының кіріс сигналының  минималды ампитудасына қатынасы, ол

минималды ампитудасына қатынасы, ол

[дБ], (3.11)

[дБ], (3.11)

[дБ], (3.12)

[дБ], (3.12)

кезінде жүйенің шығысында  сигналының белгілі бір қатынасын қамта- масыз етеді.

сигналының белгілі бір қатынасын қамта- масыз етеді.

мұндағы  - динамикалық диапазонның (

- динамикалық диапазонның (  кіріс сигнал амплитудасы кезінде) төменгі шекарадағы шығыс сигналының қуаты.

кіріс сигнал амплитудасы кезінде) төменгі шекарадағы шығыс сигналының қуаты.

Динамикалық диапазонын масштабтау коэффициентін енгізу арқылы бақылау керек.

2.Тураадресі бар TMS 320С10 сигналды процессорының командаларформаты.

ЦСП-ның бірінші буынына TMS320C1x жанұясы жатады. Бұл жанұяның мінездемелік көрсеткіші 16-разрядты TMS320C10К процессоры болып табылады, ол 200 нс-тан көп емес командалық цикл ұзақтығындағы 1 секунд ішінде 5 млн.операцияны орындауға әрекетті. Процессорда екілік толықтыру кодты жылжымалы тіркелген арифметика жүзеге асырылады. Процессор сегіз 16-разрядты енгізу порты мен сегіз 16-разрядты шығару мәліметтерін адрестейді [ 7 ].

Процессор негізіне жоғарғы икемділікпен тезәрекеттілікке жету үшін модифицияланған гарвардты архитектура қойылған, оларды командалар орындалуы мен таңдау процессі уақыты кезінде біріктіруге рұқсат етеді, және де программа жадысы мен мәліметтер жадысы арасындағы байланысты орындайды.

Программа жадысы 1536×16 разрядты көлемі бар тұрақты есте сақтау құрылғысында (ТЕСҚ)жүзеге асырылады және кристалл ішінде (TMS320C10 процессоры) және сыртында (TMS32010 процессоры) орналасуы мүмкін. Максималды тезәрекеттілік сақталуымен 4096×16 разрядты жалпы көлеміне дейін ішкі жадының үлкеюіне мүмкіншілігі бар.

5.1 суретте TMS320C10 процессор операциялық блогының құрылымдық сұлбасы көрсетілген.

5.1 сурет

5.1суретте көрсетілгендей, процессордың құрамында көлемі 288 байт оперативті есте сақтау құрылғысын (ОЕСҚ) және төрт негізгі арифметикалық түйіні: арифметикалық-логикалық құрылғы (АЛҚ), аккумулятор, көбейткіш және ығысу құрылғысын қамтитын мәліметтер жадысы бар.

АЛҚ32-разрядты сөздердің қосу, азайту және логикалық операцияларын орындауға негізделген. Бір операнды аккумулятордан алынады, екіншісі не көбейткіш өндіретін регистрдан (Р) не 0-15 разрядқа солға ығысу тізбегінің мүмкіндігімен ішкі мәліметтер шинасынан алынады. Операция нәтижесі аккумуляторға енгізіледі. Параллельді ығысу құрылғысы (0,1,4 ығысуы) өндіруші нәтиженің масштабталуы үшін мәліметтер жадысына аккумулятордың үлкен разрядтарымжазылуы кезінде қолданылады.

Мультиплексор (MS) арқылы процессор адрестеудің екі әдісінің бірін қолдана алады: тікелей және қосалқы. Бірінші әдіс кезінде ұяшық жадысының адресі команданың жеті кіші разрядты сөзінен және бетті (DP) көрсететін бір разрядтан құрылады. 5.2 суретте көрсетілгендей, мәліметтер жадысы сұлба бойынша топтарға бөлінеді.

Қосалқы адресация режимінде мәліметтер жадысының адресі ретінде сегіз кіші разрядты қосымша регистрдің (ARO немесе AR1) бірі қолданылады. Осы қосымша регистр нұсқаушы қосымша регистр (ARP) көмегімен таңдала- ды. Мәліметтерді уақытша сақтау үшін немесе циклдарды ұйымдастыру үшін ортақ регистр ретінде қосымша 16-разрядты регистрларды қолдануға болады.

Ұяшық жадысының нөмірі

0 бет (DP = 0) 0 - 127

0 бет (DP = 0) 0 - 127

1 бет (DP = 1) 128 – 144

1 бет (DP = 1) 128 – 144

5.2 сурет

Процессорды басқару блогының құрамына (суретте көрсетілмеген) басқару құрылғысы, программалық есептегіш, төрттен көп емес енгізу тереңдікті стекті жады кіреді. Программалық есептегіш пен стек тұтынушы- ларға программа-астыны шақыруға және үзілісті, өтулерді ұйымдастыруға мүмкіндік береді.

Процессордың команда жинағы ССӨ түрлі алгоритмін жүзеге асыруға және бөлек биттерге әсер етуге мүмкіндік береді. Команда жүйесі 60 команда- ны құрайды, оның көбісі бірциклды болып табылады. Команда алты топтан тұрады: аккумулятормен, индексті регистрлермен, нұсқаушы-регистрлермен, көбейткіш блокпен, тармақталуды және басқаруды ұйымдастыру үшін, енгізу- шығару және жадыға хабарлау жұмысы

3. ТMS 320 сериялы сигналды процессорының келесі командаларының әрекетін суреттеңіз:

а) LTA 20; b) MPY 15; c) MPY * + ,04

a) Команда өзіне LT және APAC командаларын біріктіреді

Регистр Т  [20]

[20]

ACC  (ACC)+(p)

(ACC)+(p)

b) Ұяшықтың құрамы Т регистрның құрамына көбейтіледі

MPY 15

Р  [15]

[15]  (Т)

(Т)

Р  [(АR)]

[(АR)]  (Т), жанама адрестеу

(Т), жанама адрестеу

c)

MPY 15

MPY * + ,04

Р  [15]

[15]  (Т)

(Т)

Р  [(АR)]

[(АR)]  (Т), жанама адресту

(Т), жанама адресту

Жане 30 билет

Жане 31 билет

1.TMS320C50 процессорында қолданылатын адрестеудің түрлері.

TMS320С5х -модифицияланған Гарвардтық архитектурасына негізделетін сигналдық процессорлар. Бұл архитектурада жадының екі кеңістігі, яғни өзінің адрестер мен деректер шинасы бар бағдарламалар мен деректер үшін қолданылатын кеңістіктер. Бағдарламалар жадысы деректерінің шинасы бойынша бағдарламалық жадыдан командалар коды мен тікелей операндтар жіберіледі. Деректер жадысы деректерінің шинасы бойынша деректер процессордың әртүрлі модульдерінен деректер жадысына және керісінше жіберіледі. Бағдарлама жадысы мен деректер жадысы арасында деректерді алмастыру командалары болады.В процессорах семейства TMS320C5x возможны четыре основных режима адресации памяти данных:

1) Прямая адресация.

2) Косвенная адресация.

3) Непосредственная адресация.

4) Циклическая адресация.

Прямая адресация.

Вся область памяти данных процессора объёмом 64К разделена на 512 страниц размером 128 16-ти разрядных слов каждая. В режиме прямой адресации, команда содержит только младшие 7 бит адреса ячейки памяти. Это поле при обработке адреса дополняется 9 битами регистра указателя страницы (DP) до полного 16-ти разрядного адреса.

Косвенная адресация.

Восемь вспомогательных регистров (AR0 - AR7) обеспечивают гибкую и удобную косвенную адресацию в процессорах TMS320C5х. В случае косвенной адресации адрес операнда находится в текущем вспомогательном регистре.

Непосредственная адресация

В случае непосредственной адресации операнд содержится непосредственно в слове команды. В процессорах `C5x имеются однословные команды с непосредственной адресацией (8-битовые, 9-битовые и 13-битовые константы) и двухсловные (16-битные константы) длинные команды с непосредственной адресацией.

Циклическая адресация

Циклическая адресация представляет метод адресации, при котором происходит циклическое обращение к ячейкам некоторой области памяти (к ячейкам буфера), т.е. при достижении конца буфера автоматически происходит переход к его началу и наоборот

2.TMS320C10 процессоры басқару блогының құрылымдық сұлбасы, белгіленуі мен түйіндердің жұмысы.Быстрее »»» мало времени!!! О_о

ЦСП-ның бірінші буынына TMS320C1x жанұясы жатады. Бұл жанұяның мінездемелік көрсеткіші 16-разрядты TMS320C10К процессоры болып табылады, ол 200 нс-тан көп емес командалық цикл ұзақтығындағы 1 секунд ішінде 5 млн.операцияны орындауға әрекетті. Процессорда екілік толықтыру кодты жылжымалы тіркелген арифметика жүзеге асырылады. Процессор сегіз 16-разрядты енгізу порты мен сегіз 16-разрядты шығару мәліметтерін адрестейді. Процессор негізіне жоғарғы икемділікпен тезәрекеттілікке жету үшін модифицияланған гарвардты архитектура қойылған, оларды командалар орындалуы мен таңдау процессі уақыты кезінде біріктіруге рұқсат етеді, және де программа жадысы мен мәліметтер жадысы арасындағы байланысты орындайды. Программа жадысы 1536×16 разрядты көлемі бар тұрақты есте сақтау құрылғысында (ТЕСҚ)жүзеге асырылады және кристалл ішінде (TMS320C10 процессоры) және сыртында (TMS32010 процессоры) орналасуы мүмкін. Максималды тезәрекеттілік сақталуымен 4096×16 разрядты жалпы көлеміне дейін ішкі жадының үлкеюіне мүмкіншілігі бар.

TMS320C10 процессоры басқару блогының құрылымдық сұлбасы:

3.z = 7y, егер [11] y есептеуінің бағдарламасының фрагментін құру.

Жане 32 билет

1) ТІРКЕЛГЕН НҮКТЕСІ БАР САНДАРДЫҢ ФОРМАТЫ

Тіркелген нүктелі цифрлық сигналды процессорлардың жіктелуі мен ерекшеліктері

Дәрістің мазмұны:Texas Instruments фирмасының тіркелген нүктелі сигналды процессорлардың буындары, олардың ерекшеліктері.

Дәрістің мақсаты:цифрлық сигналды процессорлары төрт буынының құрылымының ерекшеліктерін оқу, олардың мүмкіндіктерін әртүрлі салада қолдануды бағалау.

Қазіргі заманғы сигналды процессорларда арифметикалық операциялар тіркелген немесе жылжымалы нүктелі арифметиканы пайдаланып орындалады.

Сигналдарды цифрлық өңдеуде тіркелген нүктелі арифметика кең таралған, өйткені оны жүзеге асыру тез, әрі қымбат емес. Бірақ, мұндай формада сандарды көрсетуде олардың диапазоны шектеулі, ал қорытынды жүйе толып кету жағдайына жақын, сондықтан өңделетін деректерді кеңейтуді енгізу қажет.

Жылжымалы нүктелі процессорлар деректерді дәл көрсету кезінде кеңейтілген динамикалық диапазонда жұмыс істейді, бірақ оның архитектурасы әлдеқайда күрделірек, сондықтан олардың кристалының өлшемі үлкен және құны жоғары болады.

Бұдан әрі Texas Instruments фирмасы өндіретін TMS320 жанұялы жылжымалы тіркелген типті сандық сигналды процессорлардың төрт буынының архитектурасы қарастырылады. Процессордың төрт буынға бөлінуі тарихи себептерге, архитектуралық ерекшеліктеріне және есептеу эффектісіне негізделген.

ЦСП-ның бірінші буынына TMS320C1x жанұясы жатады. Бұл жанұяның мінездемелік көрсеткіші 16-разрядты TMS320C10К процессоры болып табылады, ол 200 нс-тан көп емес командалық цикл ұзақтығындағы 1 секунд ішінде 5 млн.операцияны орындауға әрекетті. Процессорда екілік толықтыру кодты жылжымалы тіркелген арифметика жүзеге асырылады. Процессор сегіз 16-разрядты енгізу порты мен сегіз 16-разрядты шығару мәліметтерін адрестейді [ 7 ].

Процессор негізіне жоғарғы икемділікпен тезәрекеттілікке жету үшін модифицияланған гарвардты архитектура қойылған, оларды командалар орындалуы мен таңдау процессі уақыты кезінде біріктіруге рұқсат етеді, және де программа жадысы мен мәліметтер жадысы арасындағы байланысты орындайды.

Программа жадысы 1536×16 разрядты көлемі бар тұрақты есте сақтау құрылғысында (ТЕСҚ)жүзеге асырылады және кристалл ішінде (TMS320C10 процессоры) және сыртында (TMS32010 процессоры) орналасуы мүмкін. Максималды тезәрекеттілік сақталуымен 4096×16 разрядты жалпы көлеміне дейін ішкі жадының үлкеюіне мүмкіншілігі бар.

5.1 суретте TMS320C10 процессор операциялық блогының құрылымдық сұлбасы көрсетілген.

5.1 сурет

5.1 суретте көрсетілгендей, процессордың құрамында көлемі 288 байт оперативті есте сақтау құрылғысын (ОЕСҚ) және төрт негізгі арифметикалық түйіні: арифметикалық-логикалық құрылғы (АЛҚ), аккумулятор, көбейткіш және ығысу құрылғысын қамтитын мәліметтер жадысы бар.

2) TMS320C50 СИГНАЛДЫ ПРОЦЕССОРДЫҢ ЖАДЫСЫН ҰЙЫМДАСТЫРУ

TMS320C50 жанұялы жылжымалы тіркелген типті сандық сигналды процессорлардың төрт буынының архитектурасы қарастырылады. Процессордың төрт буынға бөлінуі тарихи себептерге, архитектуралық ерекшеліктеріне және есептеу эффектісіне негізделген.

ЦСП-ның бірінші буынына TMS320C50 жанұясы жатады. Бұл жанұяның мінездемелік көрсеткіші 16-разрядты TMS320C50 процессоры болып табылады, ол 200 нс-тан көп емес командалық цикл ұзақтығындағы 1 секунд ішінде 5 млн.операцияны орындауға әрекетті. Процессорда екілік толықтыру кодты жылжымалы тіркелген арифметика жүзеге асырылады. Процессор сегіз 16-разрядты енгізу порты мен сегіз 16-разрядты шығару мәліметтерін адрестейді [ 7 ].

Процессор негізіне жоғарғы икемділікпен тезәрекеттілікке жету үшін модифицияланған гарвардты архитектура қойылған, оларды командалар орындалуы мен таңдау процессі уақыты кезінде біріктіруге рұқсат етеді, және де программа жадысы мен мәліметтер жадысы арасындағы байланысты орындайды.

Программа жадысы 1536×16 разрядты көлемі бар тұрақты есте сақтау құрылғысында (ТЕСҚ)жүзеге асырылады және кристалл ішінде (TMS320C10 процессоры) және сыртында (TMS32010 процессоры) орналасуы мүмкін. Максималды тезәрекеттілік сақталуымен 4096×16 разрядты жалпы көлеміне дейін ішкі жадының үлкеюіне мүмкіншілігі бар.

1 суретте TMS320C50 процессор операциялық блогының құрылымдық сұлбасы көрсетілген.

3) КЕЛЕСІ ФРАГМЕНТТЕРДІ ОРЫНДАҒАННАН КЕЙІН, AR0, AR1 ЖӘНЕ ARP МӘНДЕРІ ҚАНДАЙ БОЛАДЫ?КОМАНДАЛАР LARK 3 SACL 8 LAR AR0,8 LAR AR1,8 ADD * +,5,1 ADD * -

Қосалқы адресация режимінде мәліметтер жадысының адресі ретінде сегіз кіші разрядты қосымша регистрдің (ARO немесе AR1) бірі қолданылады. Осы қосымша регистр нұсқаушы қосымша регистр (ARP) көмегімен таңдала- ды. Мәліметтерді уақытша сақтау үшін немесе циклдарды ұйымдастыру үшін ортақ регистр ретінде қосымша 16-разрядты регистрларды қолдануға болады.

Ұяшық жадысының нөмірі

0 бет (DP = 0) 0 - 127

0 бет (DP = 0) 0 - 127

1 бет (DP = 1) 128 – 144

1 бет (DP = 1) 128 – 144

Жанама адресация. Сегіз қосымша регистрлер (AR0 - AR7)TMS320C5х процессорлар ішіндегі ыңғайлы жанама адресацияны қамтамассыз етеді. Жанама адресация кезінде операнд адресі қосымша регстрде орналасады. Қосымша регстрді таңдау үшін регістрге ARP регистрдің 0-7 диапазонындағы мәнін еігізу керек.

Жане 33 билет

1)Сандық жүйелерде сигналдарды өңдеу есептемесі  ,

,  өңделетін сигналмен, әртүрлі теңдіктегі коэффициенттермен немесе ауыспалы функциямен, сол сияқты көбейткіштер мен сумматор- лардағы арифметикалық операциялардың орындалу нәтижесі регистр разрядтылығымен, ұяшық жадысымен, операциялық құрылғылармен сәйкес b-разрядты екілік сандармен көрсетіледі. Мұндай сандар көрсетілімі квантталу деп аталады. Квантталу – сызықты емес операция, сол себепті сызықты дискретті өрнекпен өрнектелетін сигналдарды өңдеу алгоритміне енгізген кезінде алгоритмді жүзеге асыруда қателіктер пайда болады. Мұндай қателіктер квантталу қателігі деп аталады.

өңделетін сигналмен, әртүрлі теңдіктегі коэффициенттермен немесе ауыспалы функциямен, сол сияқты көбейткіштер мен сумматор- лардағы арифметикалық операциялардың орындалу нәтижесі регистр разрядтылығымен, ұяшық жадысымен, операциялық құрылғылармен сәйкес b-разрядты екілік сандармен көрсетіледі. Мұндай сандар көрсетілімі квантталу деп аталады. Квантталу – сызықты емес операция, сол себепті сызықты дискретті өрнекпен өрнектелетін сигналдарды өңдеу алгоритміне енгізген кезінде алгоритмді жүзеге асыруда қателіктер пайда болады. Мұндай қателіктер квантталу қателігі деп аталады.

Квантталу кезінде сандар жақындауының екі әдісі қолданылады: дөңгелектеу және қиылысу. Дөңгелектеу кезінде квантталудың жақын деңгейі таңдалады, бұл кезде бастапқы k-разрядты сан ( k>b ) жақын b-разрядқа ауыстырылады және  дөңгелектеу қателігі квантталудың жартылай қадамынан аспайды

дөңгелектеу қателігі квантталудың жартылай қадамынан аспайды

(3.3)

(3.3)

k- разрядты санның bмәнді разрядына дейін (k>b)қиылысу кезінде кіші (k - b)разрядты баспатқы мәндер алынып тасталынады.  қиылысу қателігі квантталу қадамынан кіші, бірақ дөңгелектеу қателігінен үлкен

қиылысу қателігі квантталу қадамынан кіші, бірақ дөңгелектеу қателігінен үлкен

<

<  (3.4)

(3.4)

2) Қазіргі заманғы сигналды процессорларда арифметикалық операциялар тіркелген немесе жылжымалы нүктелі арифметиканы пайдаланып орындалады.

Texas Instruments фирмасы өндіретін TMS320 жанұялы жылжымалы тіркелген типті сандық сигналды процессорлардың төрт буынының архитектурасы қарастырылады. Процессордың төрт буынға бөлінуі тарихи себептерге, архитектуралық ерекшеліктеріне және есептеу эффектісіне негізделген.

Процессор негізіне жоғарғы икемділікпен тезәрекеттілікке жету үшін модифицияланған гарвардты архитектура қойылған, оларды командалар орындалуы мен таңдау процессі уақыты кезінде біріктіруге рұқсат етеді, және де программа жадысы мен мәліметтер жадысы арасындағы байланысты орындайды.

Программа жадысы 1536×16 разрядты көлемі бар тұрақты есте сақтау құрылғысында (ТЕСҚ)жүзеге асырылады және кристалл ішінде (TMS320C10 процессоры) және сыртында (TMS32010 процессоры) орналасуы мүмкін. Максималды тезәрекеттілік сақталуымен 4096×16 разрядты жалпы көлеміне дейін ішкі жадының үлкеюіне мүмкіншілігі бар.

5.1 суретте TMS320C10 процессор операциялық блогының құрылымдық сұлбасы көрсетілген.

5.1суретте көрсетілгендей, процессордың құрамында көлемі 288 байт оперативті есте сақтау құрылғысын (ОЕСҚ) және төрт негізгі арифметикалық түйіні: арифметикалық-логикалық құрылғы (АЛҚ), аккумулятор, көбейткіш және ығысу құрылғысын қамтитын мәліметтер жадысы бар.

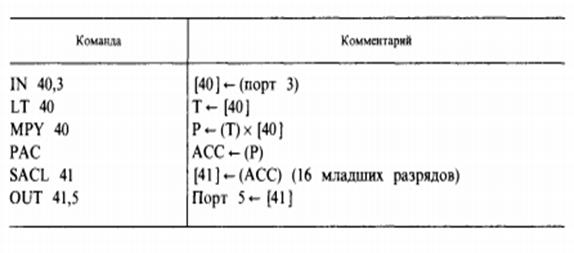

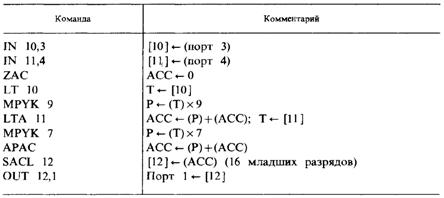

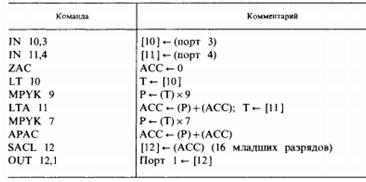

3.Бағдарламаның келесі фрагментін орындау үшін түсініктеме құру:

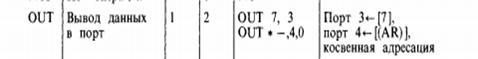

1.Ввод данных из порта IN 30,2 [30]←(Порт 2) косвенная адресация

2.Загрузка регистрТLT 30 Регистр Т←[30] косвенная адресация

3.Содержимое ячейки памяти умножается на содержимое регистраТMPY 30 P←[30]x(T) косвенная адресация

4.Загрузка аккумулятора содержимым регистра PPACACC←(P)

5.Запись в память младших 16 разрядов аккумулятора SACL31 [31] ←(АСС,разряды 15...0) косвенная адресация

6.Вывод данных в порт OUT 31,6 Порт 6←[31] косвенная адресация

Жане 34 билет

Жане 35 билет

1.Белгісі бар және белгісі жоқ бүтін сандарды көрсету.

Сандық сигналды процессорлар (ССП) арнайы (программаланбайтын) өте үлкен интегралдық сұлба (ӨҮИС) немесе әмбебап ӨҮИС түрінде орындала алады.

Көбейткіш операциясы программалық формада еңбекті операция болуы жеткілікті, сондықтан да аппараттық көбейткіш-жинағыш деп аталатын арнайы құрылғыдағы құбылмалы немесе тіркелген жылжымалы аппаратымен ССП-да жүзеге асырылады. Аппараттық көбейткішбір командалық цикл ішінде көбейткіш операциясын орындай алады. Мысалы, тіркелген үтірі бар процессорда мұндай көбейткіш бір такт ішінде (әдетте 25 нс) 2-ге дейінгі толықтыру түрінде көрсетілген екі 16-биттік бөлшек сандарды қабылдайды, және 32-биттік түрде есептеп шығарады.

Арнайы команда қолданатындықтан командалық цикл санын қысқарту- ға болады. Мысалы, LTD командасы бір цикл ішінде үш команданы орындайды: жүктелу (LT), кешігу (DMOV), қосу (APAC). Заманауи ССП-да MACD командасы бар, ол бір командалық цикл ішінде төрт команда- ны орындай алады: жүктелу (LT), кешігу (DMOV), қосу (APAC) және көбейткіш (MPY).

2. TMS320c10 сигналды процессордың жадысын ұйымдастыру

Texas Instruments фирмасы өндіретін TMS320 жанұялы жылжымалы тіркелген типті сандық сигналды процессорлардың төрт буынының архитектурасы қарастырылады. Процессордың төрт буынға бөлінуі тарихи себептерге, архитектуралық ерекшеліктеріне және есептеу эффектісіне негізделген.

ЦСП-ның бірінші буынына TMS320C1x жанұясы жатады. Бұл жанұяның мінездемелік көрсеткіші 16-разрядты TMS320C10К процессоры болып табылады, ол 200 нс-тан көп емес командалық цикл ұзақтығындағы 1 секунд ішінде 5 млн.операцияны орындауға әрекетті. Процессорда екілік толықтыру кодты жылжымалы тіркелген арифметика жүзеге асырылады. Процессор сегіз 16-разрядты енгізу порты мен сегіз 16-разрядты шығару мәліметтерін адрестейді [ 7 ].

Программа жадысы 1536×16 разрядты көлемі бар тұрақты есте сақтау құрылғысында (ТЕСҚ)жүзеге асырылады және кристалл ішінде (TMS320C10 процессоры) және сыртында (TMS32010 процессоры) орналасуы мүмкін. Максималды тезәрекеттілік сақталуымен 4096×16 разрядты жалпы көлеміне дейін ішкі жадының үлкеюіне мүмкіншілігі бар.

TSM320 сериялы сиг.проц. командаларын орындау

Қосалқы адресация режимінде мәліметтер жадысының адресі ретінде сегіз кіші разрядты қосымша регистрдің (ARO немесе AR1) бірі қолданылады. Осы қосымша регистр нұсқаушы қосымша регистр (ARP) көмегімен таңдала- ды. Мәліметтерді уақытша сақтау үшін немесе циклдарды ұйымдастыру үшін ортақ регистр ретінде қосымша 16-разрядты регистрларды қолдануға болады.

Ұяшық жадысының нөмірі

0 бет (DP = 0) 0 - 127

0 бет (DP = 0) 0 - 127

1 бет (DP = 1) 128 – 144

1 бет (DP = 1) 128 – 144

Восемь вспомогательных регистров (AR0 - AR7) обеспечивают гибкую и удобную косвенную адресацию в процессорах TMS320C5х. В случае косвенной адресации адрес операнда находится в текущем вспомогательном регистре. Для выбора текущего вспомогательного регистра необходимо загрузить в регистр указателя вспомогательного регистра (ARP) значение в диапазоне от 0 до 7. После выполнения любой команды с косвенной адресацией в ARP может быть загружено новое значение. Если в ARP загружается новая величина, то старая величина загружается в буфер вспомогательного регистра состояния ST1.

Косвенная адресация может быть использована во всех командах, кроме команд с непосредственными операндами или без операндов.

Жане 36 билет

1.Белгісі бар және белгісі жоқ бөлшек сандарды көрсету.

2.Микропроцессорларда қолданылатын Нейман және Гарвард архитектуралық фондарына салыстырмалы сипаттама беру.

В чистой архитектуре фон Неймана процессор в каждый момент времени может либо читать инструкцию, либо читать/записывать единицу данных из/в памяти. Оба действия одновременно происходить не могут, поскольку инструкции и данные используют один и тот же поток (шину).

В компьютере с использованием гарвардской архитектуры процессор может читать инструкции и выполнять доступ к памяти данных одновременно, без использования кэш-памяти. Таким образом, компьютер с гарвардской архитектурой при определенной сложности схемы быстрее, чем компьютер с архитектурой фон Неймана, поскольку шины инструкций и данных расположены на разных, не связанных между собой физически, каналах.

Исходя из физического разделения шин команд и данных, разрядности этих шин (следовательно, и адресные пространства) могут иметь различные значения ифизически не могут пересекаться друг с другом.

| Фоннеймановская архитектура | Гарвардская архитектура |

Гарвард архитектурасын 70-ші жылдарғадейінқолданбаған, себебі МП-ныңөндірушілерібасқарудыңавтономдыжүйелерiнiңөңдеушiлерiнақтылыартықшылықтардыбергенiнтүсiнбедi. Бұданбасқа, Гарвард архитектурасы параллель операциялардыңiскеасыруыбағдарламаныңорындауыжоғарыдылдамдықты Фон-Нейманменсалыстырғандамүмкіндікесебіненпарраллельқамтамасызетеді. Келесiкоманданыңiрiктеуiорындауменалдыңғыбiруақытта бола алады, жәнекоманданыңiрiктеуi процессор уақытшатоқтатуғақажетiжоқ. Бұлоперациялардыңiскеасыруыныңәдiсiциклдержәнебағдарламаның сын көзiменбөлiмшелерiнiңорындаууақытынанықтауғажайғанарақмүмкiндiкберетiнтакттердiңбiрдейсанғаәртүрлiкомандаларыныңорындауықамтамасызетугемүмкiндiкбередi.

3.TSM320 сериялы сигналды процессорының келесі командаларының әрекетін суреттеңіз:

1.Ввод данных из портаIN 25,6[25]←(ПОРТ 6)

2.Ввод данных из порта IN *-,7,0 [(AR)]←(ПОРТ 7), КОСВЕННАЯ АДРЕСАЦИЯ

3.СЛОЖЕНИЕ СОДЕРЖИМОГО РЕГИСТРА Р С СОДЕРЖИМЫМ АККУМУЛЯТОРАAPACACC←(P)+(ACC)

Жане 37 билет

1 Сигналдарды өңдеудің процессорларының жіктелуі.

Сигналдарды цифрлық өңдеу (СЦӨ) ЭЕМ қолданылуында кешенді ғылыми-техникалық бағыт ретінде негізделеді және телекоммуникация жүйелеріндегі сигналдарды цифрлық өңдеуге арналған арнайы есептеуіш техника құралдары (Internet әлемдік желісін қоса), басқару, мультимедиа, медицина және т.б. ретінде.

Сигналды процессорлар (СП) – бұл қазіргі уақыттағы ақпараттық және байланыстық желі мен жүйедегі сигналдарды өңдеуі, түрлендіруі және түзілуі үшін арналған құрылғы. Олардың басты ерекшелігі – үлкен массивті мәліметтерді өңдеуі. Өңдейтін сигналдар мен СП элементті базасы түрі бойынша аналогты және сандық болып бөлінді.

Сандық сигналды процессорлар (ССП) арнайы (программаланбайтын) өте үлкен интегралдық сұлба (ӨҮИС) немесе әмбебап ӨҮИС түрінде орындала алады. Арнайы процессорларға жатады, мысалы, Фурьенің жылдам түрлендіргіш процессоры, жиілік синтезаторы, кодер және т.б. Әмбебеп процессорларға жататындар:

1) Логикалық сұлбалар (ПЛИС – программаланатын логикалық интегралдық сұлбалар);

2) Программаланатын сандық сигналды процессорлар шет ел аббревиатурасымен аталатын DSP ( Digital Signal Processor);

3) транспьютерлер.

2 TMS320С50 сигналды процессорына қысқаша техникалық сипаттама беру.

TMS320С50 - модифицияланған Гарвардтық архитектурасына негізделетін сигналдық процессорлар. Бұл архитектурада жадының екі кеңістігі, яғни өзінің адрестер мен деректер шинасы бар бағдарламалар мен деректер үшін қолданылатын кеңістіктер. Бағдарламалар жадысы деректерінің шинасы бойынша бағдарламалық жадыдан командалар коды мен тікелей операндтар жіберіледі. Деректер жадысы деректерінің шинасы бойынша деректер процессордың әртүрлі модульдерінен деректер жадысына және керісінше жіберіледі. Бағдарлама жадысы мен деректер жадысы арасында деректерді алмастыру командалары болады.

TMS320C50 процессорларында параллельдіктің жоғарғы деңгейі болады. Әзірге деректер арифметико-логикалық құрылғыда (ALU) өңделіп жатқанда, қосымша регистрлердің арифметикалық құрылғысында осы регистрлердің инкремент немесе декременті жүргізілуі мүмкін.

TMS320C50 процессорының құрылымдық сұлбасында процессор 32-разрядты ALU мен аккумулятор (ACC) пайдаланып, арифметикалық командаларды орындайды, ол 16-разрядты операндтармен (тікелей немесе жадыдан) немесе/және 32-разрядты көбейткіштен немесе аккумулятордан операцияланады.

3 TSM320 сериялы сигналды процессорының келесі командаларының әрекетін суреттеңіз::

LAR AR1 * - , 0 ; b) LARK ARO, 55; c) LARP 0.

1) Жады ұяшығындағы берілгендерді көрсетілген қосымша регистрға жазады

LAR AR1, *-,0 AR1 <-(AR) жанама адресация

2) Командада берілген 8разрядты дұрыс константаны қосымша регистрге енгізу

LARK AR0,55 Кіші разряд AR0<- 55, үлкен разрядтары нөлге айналады

3) Берілгендерді тікелей қосымша регистрге енгізу

LARP 0 ARP<-0

Жане 38 билет

1.TMS320C10 цифрлық сигналды процессордың архитектурасы және құрылымы.

ЦСП-ның бірінші буынына TMS320C1x жанұясы жатады. Бұл жанұяның мінездемелік көрсеткіші 16-разрядты TMS320C10К процессоры болып табылады, ол 200 нс-тан көп емес командалық цикл ұзақтығындағы 1 секунд ішінде 5 млн.операцияны орындауға әрекетті. Процессорда екілік толықтыру кодты жылжымалы тіркелген арифметика жүзеге асырылады. Процессор сегіз 16-разрядты енгізу порты мен сегіз 16-разрядты шығару мәліметтерін адрестейді [ 7 ].

Процессор негізіне жоғарғы икемділікпен тезәрекеттілікке жету үшін модифицияланған гарвардты архитектура қойылған, оларды командалар орындалуы мен таңдау процессі уақыты кезінде біріктіруге рұқсат етеді, және де программа жадысы мен мәліметтер жадысы арасындағы байланысты орындайды.

Программа жадысы 1536×16 разрядты көлемі бар тұрақты есте сақтау құрылғысында (ТЕСҚ)жүзеге асырылады және кристалл ішінде (TMS320C10 процессоры) және сыртында (TMS32010 процессоры) орналасуы мүмкін. Максималдытезәрекеттілік сақталуымен 4096×16 разрядты жалпы көлеміне дейін ішкі жадының үлкеюіне мүмкіншілігі бар.

5.1 суретте TMS320C10 процессор операциялық блогының құрылымдық сұлбасы көрсетілген.

5.1 сурет

5.1 суретте көрсетілгендей, процессордың құрамында көлемі 288 байт оперативті есте сақтау құрылғысын (ОЕСҚ) және төрт негізгі арифметикалық түйіні: арифметикалық-логикалық құрылғы (АЛҚ), аккумулятор, көбейткіш және ығысу құрылғысын қамтитын мәліметтер жадысы бар.

АЛҚ32-разрядты сөздердің қосу, азайту және логикалық операцияларын орындауға негізделген. Бір операнды аккумулятордан алынады, екіншісі не көбейткіш өндіретін регистрдан (Р) не 0-15 разрядқа солға ығысу тізбегінің мүмкіндігімен ішкі мәліметтер шинасынан алынады. Операция нәтижесі аккумуляторға енгізіледі. Параллельді ығысу құрылғысы (0,1,4 ығысуы) өндіруші нәтиженің масштабталуы үшін мәліметтер жадысына аккумулятордың үлкен разрядтарымжазылуы кезінде қолданылады.

2.Сигналдарды цифрлық өңдеу үшін қандай арнайы командалар қолданылады.

Арнайы команда қолданатындықтан командалық цикл санын қысқарту-ға болады. Мысалы, LTD командасы бір цикл ішінде үш команданы орындайды: жүктелу (LT), кешігу (DMOV), қосу (APAC). Заманауи ССП-да MACD командасы бар, ол бір командалық цикл ішінде төрт команда-ны орындай алады: жүктелу (LT), кешігу (DMOV), қосу (APAC) және көбейткіш (MPY).

Бірінші жән екінші ұрпақтың ССӨ процессоры команда жүйесі бойынша бірігеді және архитектура жағынан да ортақ байланысы бар, бірақ та екінші ұрпақтың процессоры үлкен функционалды мүмкіндігі мен аз қуат тұтынуын игереді. Одан қалса, оларда үлкен көлемді құрылу жадысы (TMS320C50 процессорында екі еселі ОЕСҚ көлемі 20 Кбайт, ал ТЕСҚ-4 Кбайт) және ССӨ алгоритмін эффектілі орындауда қолдау үшін көп арнайы командасы бар. Мысалы, арнайы команда құрамына көбейткіш командасы және мәлімет ығысу бар (MACD) жинағышы кіреді, оны қайталау командасымен (RPT) біріктіру кезінде белгілі бір уақытты үнемдейтін КИХ-сүзгішін жүзеге асыруға мүмкіндік береді. Биттерді инверттелуімен адрестеу мүмкіншілігі Фурьенің жылдам түрленуі (ФЖТ) кезінде пайдалы. Нәтижесінде екінші ұрпақтың процессорының есептегіш өндірісі бірінші ұрпақ процессорының өндірісіне қарағанда 4-6 есе жоғары.

3. Келесі фрагментті орындағаннан кейін, AR0, AR1 және ARP мәндері қандай болады?

Команда LARP 0; LARK AR0,5 ; LARK AR1,9 ; ADD * +,0,1 ; ADD * -;

LARP 0 ARP←0;ARP=0

LARK AR0,5AR0←5; AR0=5

LARK AR1,9 AR1←9; AR1=9

ADD * +,0,1сложитьсодержимоеакумуляторасодержимымячейкипамяти, адрес которойопределяетсясодеримымтекущеговспомогательногорегистра.В указательвспомогательногорегистрапослевыполнениякомандыдополнительногозагружаетсяеденица, т.е. дляследующейкомандытекущимвспомогательнымрегистромбудетAR1.

ADD * -сложитьсодержимоеакумуляторасодержимымячейкипамяти, адрес которойопределяетсясодеримымтекущеговспомогательногорегистра.В указательвспомогательногорегистрапослевыполнениякомандыдополнительногоуменьшаетсянаеденицу,

Жане 39 билет

1.Texas Instrumens фирмасының цифрлық сигналды процессорларының сипаттамалары.

Қазіргі заманғы сигналды процессорларда арифметикалық операциялар тіркелген немесе жылжымалы нүктелі арифметиканы пайдаланып орындалады.

Сигналдарды цифрлық өңдеуде тіркелген нүктелі арифметика кең таралған, өйткені оны жүзеге асыру тез, әрі қымбат емес. Бірақ, мұндай формада сандарды көрсетуде олардың диапазоны шектеулі, ал қорытынды жүйе толып кету жағдайына жақын, сондықтан өңделетін деректерді кеңейтуді енгізу қажет.

Жылжымалы нүктелі процессорлар деректерді дәл көрсету кезінде кеңейтілген динамикалық диапазонда жұмыс істейді, бірақ оның архитектурасы әлдеқайда күрделірек, сондықтан олардың кристалының өлшемі үлкен және құны жоғары болады.

Бұдан әрі Texas Instruments фирмасы өндіретін TMS320 жанұялы жылжымалы тіркелген типті сандық сигналды процессорлардың төрт буынының архитектурасы қарастырылады. Процессордың төрт буынға бөлінуі тарихи себептерге, архитектуралық ерекшеліктеріне және есептеу эффектісіне негізделген.

ЦСП-ның бірінші буынына TMS320C1x жанұясы жатады. Бұл жанұяның мінездемелік көрсеткіші 16-разрядты TMS320C10К процессоры болып табылады, ол 200 нс-тан көп емес командалық цикл ұзақтығындағы 1 секунд ішінде 5 млн.операцияны орындауға әрекетті. Процессорда екілік толықтыру кодты жылжымалы тіркелген арифметика жүзеге асырылады. Процессор сегіз 16-разрядты енгізу порты мен сегіз 16-разрядты шығару мәліметтерін адрестейді [ 7 ].

Процессор негізіне жоғарғы икемділікпен тезәрекеттілікке жету үшін модифицияланған гарвардты архитектура қойылған, оларды командалар орындалуы мен таңдау процессі уақыты кезінде біріктіруге рұқсат етеді, және де программа жадысы мен мәліметтер жадысы арасындағы байланысты орындайды.

Программа жадысы 1536×16 разрядты көлемі бар тұрақты есте сақтау құрылғысында (ТЕСҚ)жүзеге асырылады және кристалл ішінде (TMS320C10 процессоры) және сыртында (TMS32010 процессоры) орналасуы мүмкін. Максималды тезәрекеттілік сақталуымен 4096×16 разрядты жалпы көлеміне дейін ішкі жадының үлкеюіне мүмкіншілігі бар.

2.Сигналды процессордың өнімділігін жоғарылататын бес принциптің сипаттамасы.

Сандық сигналды процессорлар (ССП) арнайы (программаланбайтын) өте үлкен интегралдық сұлба (ӨҮИС) немесе әмбебап ӨҮИС түрінде орындала алады. Арнайы процессорларға жатады, мысалы, Фурьенің жылдам түрлендіргіш процессоры, жиілік синтезаторы, кодер және т.б. Әмбебеп процессорларға жататындар:

4) Логикалық сұлбалар (ПЛИС – программаланатын логикалық интегралдық сұлбалар);

5) Программаланатын сандық сигналды процессорлар шет ел аббревиатурасымен аталатын DSP ( Digital Signal Processor);

6) транспьютерлер.

ССП өндірілуі мен архитектурасына бойынша үлкен ақпараттық массивтерді өңдеуді жүргізуге болатын транспьютерге біршама жақын. Транспьютер RISC(Reduced Instruction Set Computer) архитертурасы бар процессорға ие, яғни қысқартылған команда жинағы барядро, бір секунд ішінде миллионнан асатын команда тезәрекеттілігі (MIPS) және параллель есептеуді қамтамасыз ететін аппаратты заттар. Транспьютердебасқа транспьютерлермен хабар алмасу үшін қызмет ететін төрт жоғарғы жылдамдықты байланыс каналы бар. Бұл төрт канал қиын байланысатын транспьютерлік желіні ұйымдастыра отырып, транспьютерлерді бір-бірімен байланысуға мүмкіндік береді. Транспьютерлер негізінде бөлінген жүйелер құрылады.

ПЛИС ССП-ға және транспьютерлерге қарағанда оңай және арзан, бірақ енгізу-шығару құрылғысы мен көптеген перифериялық құрылғыларды қажет етеді. ССП-ға қарағанда олардың шығарылымы аз.

Микропроцессор дамуының нәтижесі болған программаланатын ССПең көп таралымға ие, бірақ сандық сигналдарды өңдеу тапсырмасы үшін бейімделген архитектурасымен ерекшеленеді. ССП-ға қойылатын негізгі талаптар:

1) арифметикалық операциялардың жылдам орындалуы (жоғары тезәрекеттілік);

2) қазіргі уақыттағы үлкен көлемді есептеуі бар алгоритмді жүзеге асыру кезіндегі жоғары өндірілгіштік (алгоритм өңдеуінде көп уақыт дискретизация периоды).

Бұл талаптар келесідей ССП архитектуралық ерекшеліктерін қолдануы арқасында орындалуда:

1) гарвардтық архитектураны қолдану;

2) конвейерлі жұмыс режимін пайдалану;

3) арнайы көбейткіш құралы бары;

4) арнайы команда енгізілуі;

5) қысқа команда циклын ұйымдастыру.

3.TSM320 сериялы сигналды процессорының келесі командаларының әрекетін суреттеңіз:

a) ADD 8,4; b) SUB 12,2; c) ADD * -,3,1.

а) ADD 8, 4 – аккумулятор ішіндегі деректі , 8 жады ұяшығымен қосып, соны алдын ала сол жаққа 4 разрядқа жылжыту.

б) SUB 12, 2 - аккумулятор ішіндегі деректeн 12 жады ұяшығындағы деректі алып тастап, сол жаққа 2 разрядқа жылжыту.

с) ADD *-, 3,1 - аккумулятор ішіндегі дерекке қосымша регистр ішіндегісімен қосылады және қосымша регистр ішіндегі мән бірге кемиді. Команда орындалған соң көрсеткіш регистрге 1 қосылады және алынған мән 3 разрядқа солға жылжиды.

Жане 40 билет

1. TMS32010С5x процессорының орталық процессорлық құрылғысының құрылымы.

Орталық процессор TMS32010C5x бар конвейерлік регистро-бағдарланған архитектураны. Компоненттері БҰ болып табылады:

арифметикалық-логикалық модуль

• 32-разрядты барабанное құрылғы ығысу

• ішкі шиналар

• қосымша модульдер регистровой-сырын меңгеруде

• тіркеу файл CPU

Көбейткіш операциялар 32-разрядты деректер пішімінде тіркелген нүктесі және 40-разрядты деректер форматында өзгермелі нүктесі, әрі көбейту есебінен жүргізіледі бір такт (25 нс) түріне қарамастан, деректер және параллельді деректерді өңдеуге басқа функционалдық блоктарда микропроцессор (мысалы, ALU).

АЛУ бір такт операциялар 32-разрядты бүтін және логикалық және 40-разрядты деректер форматында өзгермелі нүктесі, оның ішінде операциялар түрлендіру форматы. Микропроцессор аппараттық қолдайды бөлу операцияларын шығару және шаршы тамыры. Құрылғы барабанды ығысу мүмкіндік береді бір такт орындауға ығысу деректер солға немесе оңға позициялар саны 1-ден 32. Екі қосымша модуль регистровой-сырын меңгеруде (AddressGeneration 0 AddressGeneration 1) жұмыс істейді параллель умножителем және АЛУ және жасай аласыз, екі мекен-жайы бір такте. Процессордың қолдау салыстырмалы базалық, база-индекстік, циклдық және бит-реверсивті адрестеу.

2. Тура адрестеуі бар TMS32010 сигналды процессорының командалар форматы. Командалар мысалдары.

Уақыттық циклы 25 нс көп емес TMS32010 жанұясы екінші ұрпақтың ССӨ процессоры болып табылады. Бірінші жән екінші ұрпақтың ССӨ процессоры команда жүйесі бойынша бірігеді және архитектура жағынан да ортақ байланысы бар, бірақ та екінші ұрпақтың процессоры үлкен функционалды мүмкіндігі мен аз қуат тұтынуын игереді. Одан қалса, оларда үлкен көлемді құрылу жадысы (TMS320C50 процессорында екі еселі ОЕСҚ көлемі 20 Кбайт, ал ТЕСҚ-4 Кбайт) және ССӨ алгоритмін эффектілі орындауда қолдау үшін көп арнайы командасы бар. Мысалы, арнайы команда құрамына көбейткіш командасы және мәлімет ығысу бар (MACD) жинағышы кіреді, оны қайталау командасымен (RPT) біріктіру кезінде белгілі бір уақытты үнемдейтін КИХ-сүзгішін жүзеге асыруға мүмкіндік береді. Биттерді инверттелуімен адрестеу мүмкіншілігі Фурьенің жылдам түрленуі (ФЖТ) кезінде пайдалы. Нәтижесінде екінші ұрпақтың процессорының есептегіш өндірісі бірінші ұрпақ процессорының өндірісіне қарағанда 4-6 есе жоғары.

TMS32010 жанұясымен мінезделетін үшінші ұрпақтың жылжымалы тіркелген ССӨ процессорының өндірісі (секунд ішінді 66 млн. команда) қосымша команданы эффекттілі қолдануы есебінен алдыңғы ұрпақтың процессорына қарағанда жақсысы болып табылады. Екінші ұрпақтың процессорымен салыстырғанда үшінші ұрпақ процессоры үш ішкі мәліметтер шинасымен жән бір программа шинасымен ерекшеленеді. Процессордың мұндай ішкі ұйымдастырылуы команданың параллель орындалуына жоғарғы дәрежеде қамтамасыз етуге мүмкіндік береді. Сол себепті жанұяға жоғары мамандандырылған команда жүйесі және ішкі жадының ұлғайған көлемі қасиетті.

3. TSM320 сериялы сигналды процессорының келесі командаларының әрекетін суреттеңіз:

а) ADD* + ,9,1; b) SUB* ,4,0; c) SUB 20,6

а) ADD* + ,9,1ACC⃪(ACC) –[(AR)] × 29, косвенная адресация

b) SUB* ,4,0ACC⃪(ACC) –[(AR)] × 24, косвенная адресация

c) SUB 20,6ACC⃪(ACC) –(20)× 26

Жане 41 билет

Жане 42 билет

1. TMS320C5x процессорының жадысын ұйымдастыру.

TMS320C50 процессорының өзіндік кристаллына жазылған Жадысы 3 түрден тұрады (Program Memory)

1) массалық – бағдарламаның бағдарламалық жадысы ROM, ол (MP/MC) басқару биті қарастырылған жұмыс режимін өзгертуге арналған;

2) берілгендер жадысы немесе бағдарламалар/SARAM берілгендер, олар бір оқу жазу операциясын толық машиналық циклда қарайды, 2К немесе 1К сөздер арасында тәуелсізблоктардан тұрады; жады конфигурациясы OVLY және RAM биттері арқылы PMST регистрінде өзгертіледі;

3) DARAM берілгендер жадысы бір оқу жазу операциясын толық машиналық циклде деректер шинасымен ешқандай кедергісіз қарастырады;жады конфигурациясы (CNF) биттары арқылы (ST1) күй регистрі арқылы өзгертіледі.

2. Арнайы аппараттық көбейткіш-жинағыштың мысалын келтіріңіз.

Операции алгебраического сложения/вычитания чисел в дополнительном коде как беззнаковых чисел выполняются в АЛУ по правилам обычной двоичной арифметики.

Операция умножения выполняется в аппаратно реализованном специализированном узле — умножителе. Умножитель реализует алгоритм умножения двоичных чисел в дополнительном коде.

При умножении целых чисел результат содержится во всех 32 разрядах. Если необходимо ограничиться при умножении целых чисел одним словом (например, для запоминания в ячейке ЗУ), то умножать нужно числа, величина которых не превышает 28, и результат будет находиться в младшем слове регистра P.

При умножении дробных чисел в формате Q15 старшее слово 32- разрядного регистра P, в котором находится результат, является его округленным значением в формате Q14 (с двумя знаковыми разрядами) с отброшенными младшими значащими разрядами.

Таким образом, в зависимости от того, какие числа перемножаются, результат может находиться или в старшем, или в младшем слове регистра P.

3. TSM320 сериялы сигналды процессорының келесі командаларының әрекетін суреттеңіз:

OUT 20,3; b) OUT * - , 2,0; c) PAC.

Жане 43 билет

1.TMS320C5x процессорының шеткі құрылғылары.

Барлық TMS320C5x сериясының процессорлары бірыңғай құрылымға ие, бірақ олардың бір – бірінен айырмашылығы ЦПУ – мен байланысқан, кристалда орналасқан шеткі құрылғылар. Суретте көрсетілгендей шеткі құрылғылар құрамына келесілер кіреді:

- программалы басқарылатын күту такттерінің генераторы;

- программалы жады банктерінің ауыстырғышы;

- параллельді енгізі\шығару порттары;

- аппараттық таймер және тактті импульстер генераторы.

2.TMS320С10 сигналды процессорының негізгі сипаттамалары.

TMS320С10 - модифицияланған Гарвардтық архитектурасына негізделетін сигналдық процессорлар. Бұл архитектурада жадының екі кеңістігі, яғни өзінің адрестер мен деректер шинасы бар бағдарламалар мен деректер үшін қолданылатын кеңістіктер. Бағдарламалар жадысы деректерінің шинасы бойынша бағдарламалық жадыдан командалар коды мен тікелей операндтар жіберіледі. Деректер жадысы деректерінің шинасы бойынша деректер процессордың әртүрлі модульдерінен деректер жадысына және керісінше жіберіледі. Бағдарлама жадысы мен деректер жадысы арасында деректерді алмастыру командалары болады.

TMS320C10 процессорларында параллельдіктің жоғарғы деңгейі болады. Әзірге деректер арифметико-логикалық құрылғыда (ALU) өңделіп жатқанда, қосымша регистрлердің арифметикалық құрылғысында осы регистрлердің инкремент немесе декременті жүргізілуі мүмкін.

TMS320C10 процессорының құрылымдық сұлбасы 7 суретте келтірілген, онда процессор 32-разрядты ALU мен аккумулятор (ACC) пайдаланып, арифметикалық командаларды орындайды, ол 16-разрядты операндтармен (тікелей немесе жадыдан) немесе/және 32-разрядты көбейткіштен немесе аккумулятордан операцияланады. Аккумулятор ALU-дан түсетін нәтижелерді сақтау үшін, сонымен қатар ALU-ға екінші операндты енгізу үшін пайдаланылады. 32-разрядты АСС үлкен сөзге (ACCH) - 31:16 биттер және 15:0 биттері бар (ACCL) кіші сөзге бөлінеді. Аккумулятордың ішіндегіні тез уақытша сақтау үшін 32-разрядты аккумулятордың буфері (ACCB) болады.

3.TSM320 сериялы сигналды процессорының келесі командаларының әрекетін суреттеңіз:

a) LTA 20; b) MPY 15; c) MPY * + ,0.

a) LTA 20; Бұл команда APAC және LT командаларын құрайды. APAC – акккумулятор мәнімен Р регистрінің мәнін қосу. LT – Т регистріне жазу. LTA 20 – T-ға 20 мәнін жазамыз, шыққан мәнге P мәнін қосамыз.

b) MPY 15; Жады ұяшығының ішіндегі мән Т регистрінің мәніне көбейтіледі.

c) MPY * + ,0.- қосалқы регистр мәніне Т регистр мәнін көбейтеміз.

Жане 44 билет

1.TMS320C3x процессорының жадысын ұйымдастыру

Процессордың құрылымдық схемасы

Процессордың құрылымы келесідей.Прпоцессор 32 разрядты шина командасы мен деректер және 24разрядты шина адресты 2 блок ОЗУ 1К 32-разрядты созден тұратын,32разрядты көбейту өзгермелі нүктесімен,64 көлемді кэш-жады 32разрядты созден,жоғары дәлдіктегі операцияларға арналған 8регистр, екі генератордың мекен-жайы және тіркеу файлы,әртүрлі әдісті адрестеулерді орындайды. 40-разрядты АЛҚ процессоры бүтін сандармен, сондай-ак өзгермелі форматтагы сандармен жұмыс істейді. Арнайы құралған контроллер Тжж деректер алмасу жады мен есептеуді бір уақытта істеуге мүмкіндік береді. ТМS320С30 мультипроцессор интерфейсінде мыналар бар: екі сыртқы интерфейстік порттар, екі тізбекті порттар, кеңейтілген үзілісті жүйе оның негізінде құрастыру жүйесін жеңілдетеді. ТМS320С30 өзінің жоғары өнімділігі және есептеу жүйелерін қарапайым пайдалануының арқасында бас процессор ретінде немесе ретінде арнайы соппроцессор қолданылуы мүмкін

Микропроцессордың перифериялық құрылғылары мен ұксас отбасы.

Процессорлар – 'СЗх өкілі көбінесе тізбектелген порттар санымен('С31 и 'С32 -1, 'С30 – 2) және DMA каналдарымен ( 'С32 - 2, 'С30 и 'С31 -1)ерекшеленеді.

2)TMS 32010 сигналды процессорының модификацияланған гарвардтық архитектурасының сипаттамасы

Процессор негізіне жоғарғы икемділікпен тезәрекеттілікке жету үшін модифицияланған гарвардты архитектура қойылған, оларды командалар орындалуы мен таңдау процессі уақыты кезінде біріктіруге рұқсат етеді, және де программа жадысы мен мәліметтер жадысы арасындағы байланысты орындайды.

Программа жадысы 1536×16 разрядты көлемі бар тұрақты есте сақтау құрылғысында (ТЕСҚ)жүзеге асырылады және кристалл ішінде (TMS320C10 процессоры) және сыртында (TMS32010 процессоры) орналасуы мүмкін. Максималды тезәрекеттілік сақталуымен 4096×16 разрядты жалпы көлеміне дейін ішкі жадының үлкеюіне мүмкіншілігі бар.

5.1 суретте TMS320C10 процессор операциялық блогының құрылымдық сұлбасы көрсетілген.

5.1 сурет

3)Келесі фрагментті орындағаннан кейін, аккумулятордың ішіндегісі қалай болады?

Дата добавления: 2018-05-02; просмотров: 872; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!