Элементная база делителя частоты импульсов

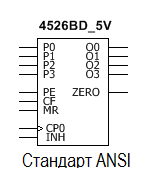

Делитель частоты с коэффициентом деления на 16 выполнен на на микросхеме 4256BP_5V (программируемый вычитающий четырехразрядный счетчик-делитель), приведенной на рис. 17.

Рис. 17. Вычитающий счетчик-делитель 4256BP_5V в стандарте ANSI

Назначение входов и выходов микросхемы описано в табл. 5 и табл. 6.

Табл. 5. Обозначения и назначение входов микросхемы

| Обозначение входов | Назначение входов |

| CF | Для подключения выхода предшествующей микросхемы при наращивании разрядности программируемого счетчика-делителя. |

| CP0 | Для ввода импульсов, соответственно, через единичный вход или через раздельные входы для вычитания и суммирования |

| INH | Для запрета вычитания в программируемом счетчике-делителе. |

| MR | Для асинхронного сброса устройства в исходное нулевое состояние. |

| P0, P1,P2, P3 | Для ввода от 0 до 3-го разряда кода в регистр или счетчик. |

| PE | Для разрешения параллельного ввода исходного кода. |

Табл. 6. Обозначения и назначение вsходов микросхемы

| Обозначение выходов | Назначение выходов |

| O0, O1, O2, O3 | Выходы разрядов реверсивного счетчика или дешифратора кодов десятичных цифр |

| ZERO | Выход, сигнализирующий об обнулении программируемого счетчика-делителя |

Схемотехника делителя частоты импульсов

Схема делителя частоты изображена на рис. 18.

Рис. 18. Функциональная схема делителя частоты импульсов

При построении данного делителя частоты использован принцип ограничения счета изменением начального кода. При использовании выходов параллельного переноса (в данном случае выход ZERO) код загрузки должен быть на 1 меньше нужного коэффициента деления, например, при заданном коэффициенте деления 16 код загрузки – 15.

|

|

|

Код загрузки 15 обеспечивается путем подачи логической единицы входы для ввода разряда кода в счетчик. А входы INH и MR заземляются для обеспечения уровня логического нуля. На вход РЕ, разрешающего параллельные ввод кода, подается сигнал с выхода Q3, обеспечивающий регулировку работы схемы (в зависимости от сигнала разрешается либо разрешается счет микросхемы).

Отладка делителя частоты импульсов

Для того чтобы убедиться в работоспособности собранного делителя подадим на вход для ввода импульсов сигнал с частотой кратной коэффициенту деления. Для измерения выходной частоты на выход Q3 подключен частотомер. Схема делителя частоты показана на рис. 19.

Рис. 19. Схема делителя частоты при отладке

Чертеж схемы делителя частоты в стандарте ANSI

Чертеж электрической принципиальной схемы делителя частоты, соответствующий схеме программы NI Multisim в стандарте ANSI, приведен на третьем листе чертежей курсового проекта.

|

|

|

Перечень компонент электрической схемы и их отечественных аналогов приведен в общей таблице спецификации компонент таких схем.

Усилитель токов (Сх14)

Дата добавления: 2018-04-15; просмотров: 420; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!