Время преобразования и система тактирования АЦП.

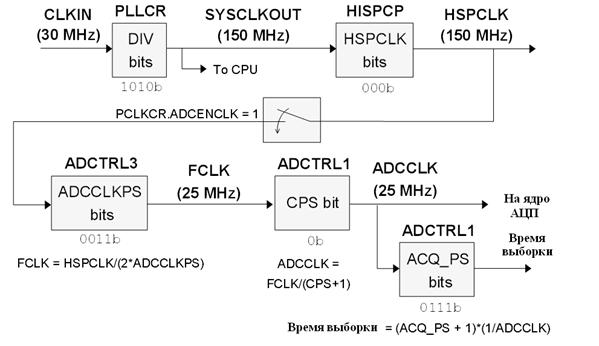

Рассмотрим настройку тактирования АЦП на примере. Тактирование АЦП осуществляется от высокоскоростного прескалера периферии HSPCLK (см. рис. 5.3).

Рис. 5.3. Пример конфигурации модуля тактирования АЦП.

Максимальная частота на выходе HSPCLK составляет 150 МГц. Максимальная частота тактирования АЦП FCLK согласно документации составляет 25 МГц. ADCCLKPS служит для формирования требуемой частоты FCLK из HSPCLK. Бит CPS позволяет при необходимости понизить частоту в два раза. Полученная ADCCLK подается на ядро АЦП и на устройство выборки-хранения. Битами ACQ_PC можно задать необходимое время захвата сигнала. За это время сигнал на УВХ должен установиться с заданной точностью. Время захвата зависит от сопротивления источника сигнала, характеристик сигнала, требуемой точности и рассчитывается для каждого случая отдельно. В лабораторных работах сигнал подается с потенциометра, высокая точность не требуется, поэтому время выборки может быть задано любое.

Минимальное время преобразования для первого канала в последовательности составляет 200 мкс, для последующих - 80 мкс.

Формат регистров модуля АЦП

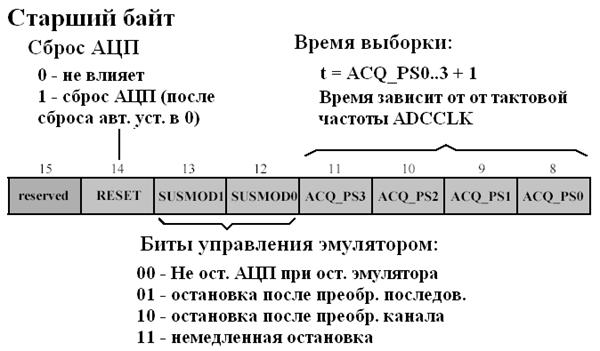

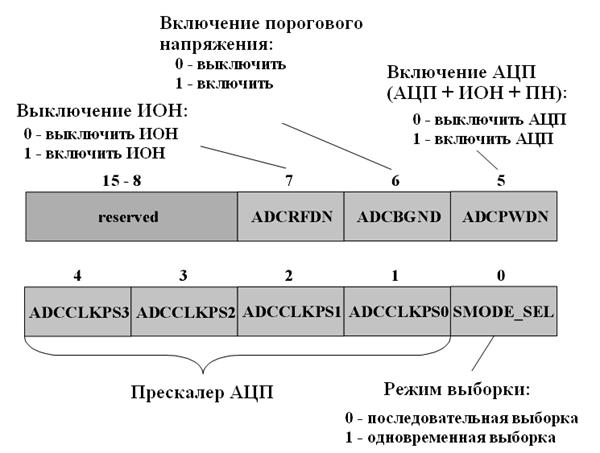

Рис. 5.4. Регистр 1 управления АЦП (ADCTRL1)

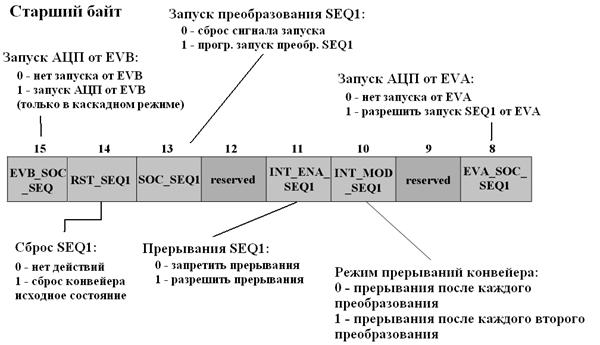

Рис. 5.5 Регистр 2 управления АЦП (ADCTRL2)

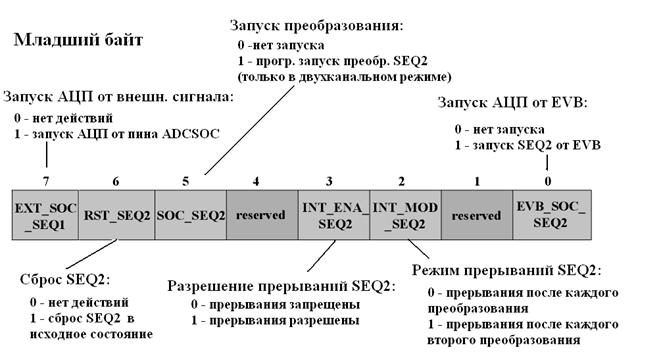

Рис. 5.6 Регистр 3 управления АЦП (ADCTRL3)

Делитель частоты ядра. Периферийная частота процессора, HSPCLK, делится на 2* ADCCLKPS[3:0], за исключением, когда ADCCLKPS[3:0] = 0000, в этом случае HSPCLK не делится. Полученная частота дополнительно делится на ADCTRL1[7]+1.

|

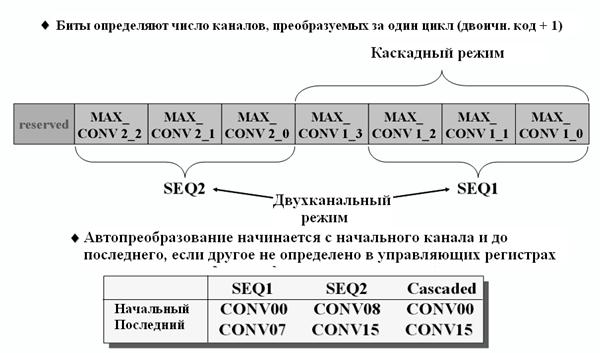

Регистр числа каналов для преобразования (ADCMAXCONV)

Рис.5.7. Формат регистра ADCMAXCONV

Рис. 5.8 Регистр статуса автопоследовательности (ADCASEQASR)

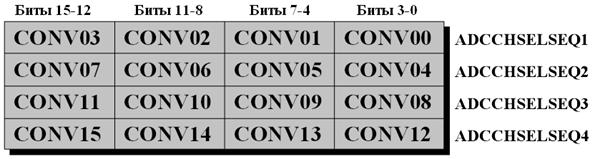

Каждый набор из 4-х бит CONVnn, выбирает один из 16 аналоговых входов АЦП для последовательного автоматического преобразования.

| Значение CONVnn | Выбираемый канал АЦП |

| 0000 | ADCINA0 |

| 0001 | ADCINA1 |

| 0010 | ADCINA2 |

| 0011 | ADCINA3 |

| 0100 | ADCINA4 |

| 0101 | ADCINA5 |

| 0110 | ADCINA6 |

| 0111 | ADCINA7 |

| 1000 | ADCINB0 |

| 1001 | ADCINB1 |

| 1010 | ADCINB2 |

| 1011 | ADCINB3 |

| 1100 | ADCINB4 |

| 1101 | ADCINB5 |

| 1110 | ADCINB6 |

| 1111 | ADCINB7 |

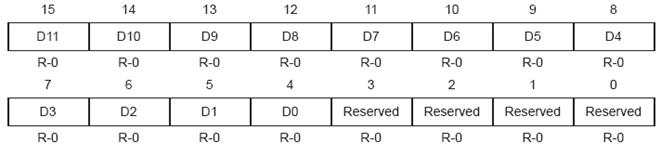

Буферный регистр результата АЦП (ADCRESULTn)

Рис. 5.9. Формат регистра ADCRESULTn

В каскадном режиме начиная с регистра ADCRESULT8 по регистр ADCRESULT15 содержат результаты преобразования с девятого по шестнадцатый. Значения всех регистров ADCRESULTn выровнены по левому краю.

|

|

|

Дата добавления: 2018-04-15; просмотров: 322; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!