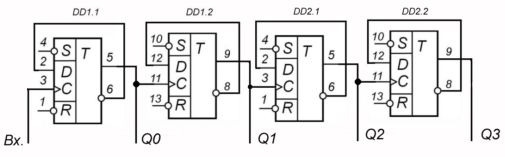

СИНХРОННЫЙ СЧЕТЧИК С ПАРАЛЛЕЛЬНЫМ ПЕРЕНОСОМ

В синхронном счетчике импульсы поступают на тактовые входы всех триггеров одновременно. Ниже на рисунке ниже приведен трехразрядный счетчик с модулем счета M = 8. Справа приведено условное обозначение промышленно выпускаемого счетчика, дополненного входами Di для параллельной синхронной загрузки начального кода перепадом сигнала на входе C(+1) при ~L = 0, а также входом сброса ~R.

Перенос из i-го разряда в (i+1)-ый производится по формуле CRi = Qi*..*Q1*Q0*(CE*PE) с помощью элементов "И". Входы CE (разрешение счета) и PE (разрешение переноса) на данном этапе рассмотрения могут быть объединены вместе (CE = PE = 1). Входы J и K триггеров соединены, поэтому возможно только два режима их работы - память (J = K= 0) и счет (J = K = 1). Триггер "i" изменит свое состояние только тогда, когда CR(i-1) = J = K = 1, т.е. при единичных значениях выходов всех предыдущих триггеров, что отвечает правилу 1. Во всех остальных случаях CR(i-1) = J = K = 0 и значение Qi не изменится. Быстродействие синхронного счетчика значительно выше, из-за того, что триггеры переключаются одновременно и сигнал CRi появится на JK входах через интервал tзд.р.счетч. = tзд.р.триггера + tзд.р.элемента"И", который не зависит от числа триггеров. Частота счета Fmax< 1/(tзд.р.сч. + tуст). Максимальная частота деления Fmax.деления = Fmax.счета.

Вопрос 28

Сегодня я не буду распространяться о пользе и незаменимости счетчиков в цифровой технике – если вы читаете эту статью, то уже наверняка в этом не сомневаетесь. Поэтому перейдем сразу к делу. Поскольку все цифровые системы работают только с нулями и единичками, то и система счисления у них двоичная, где каждая цифра в числе может принимать лишь 2 значения – «0» или «1». Я не буду сильно вникать в двоичное счисление, просто взглянем на табличку и попробуем уловить связь и отличия двоичной и десятичной систем. Считать будем от 0 до 16:

|

|

|

| Десятичная | Двоичная |

| 0 | 0000 |

| 1 | 0001 |

| 2 | 0010 |

| 3 | 0011 |

| 4 | 0100 |

| 5 | 0101 |

| 6 | 0110 |

| 7 | 0111 |

| 8 | 1000 |

| 9 | 1001 |

| 10 | 1010 |

| 11 | 1011 |

| 12 | 1100 |

| 13 | 1101 |

| 14 | 1110 |

| 15 | 1111 |

Хорошо видно, что для записи числа «15» в десятичной системе нам понадобилось всего 2 разряда (единицы, десятки), в то время как в двоичной мы использовали аж четыре разряда. Более того, в десятичной системе разряд десятков прослужит нам вплоть до числа «99», тогда как для отображения чисел больше 15 в двоичной системе потребуется дополнительный пятый разряд. Но зато в двоичной системе мы оперировали только цифрами «1» и «0».

А теперь вспомним триггер – ведь от как раз такими цифрами и оперирует – «0» – низкий уровень, «1» – высокий уровень. Теперь отвлечемся и взглянем на двухразрядный делитель частоты из предыдущей статьи:

|

|

|

Начнем подавать на его вход импульсы и смотрим на результат:

| количество импульсов на входе С | Выход Q1 | Выход Q0 |

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 2 | 1 | 0 |

| 3 | 1 | 1 |

| 4 | 0 | 0 |

Все верно, первый разряд (Q0) делит входную частоту на 2, следующий (Q1) еще на 2, все это мы разобрали в прошлый раз, но интересно не это. Сравните таблицы – наша в точности повторяет первые строки из таблицы систем счисления. Получается наш делитель… считает! Вот только до трех. При четвертом импульсе на входе наши триггеры устанавливаются в «0» и дальше процесс повторится. Почему? Не хватает разрядов? Берем еще один корпус К555ТМ2 и добавляем еще два:

Вопрос 29

Комбинационной схемой  называется схема из логических (переключательных) элементов, реализующая булеву функцию или совокупность булевых функций. В общем случае КС можно представить схемой, приведенной на рис. 11.1, где

называется схема из логических (переключательных) элементов, реализующая булеву функцию или совокупность булевых функций. В общем случае КС можно представить схемой, приведенной на рис. 11.1, где  — входы КС, а

— входы КС, а  — ее выходы.

— ее выходы.

Под логическим (переключательным) элементом чаще всего понимают техническое устройство, реализующее одну элементарную булеву функцию.

|

|

|

Прикладная теория цифровых автоматов не рассматривает физические явления, лежащие в основе разработки и функционирования логических элементов. Обычно логический элемент понимается как «черный ящик» и учитывается только реализуемая элементом булева функция. Примеры логических элементов конъюнкции, дизъюнкции, И — НЕ, ИЛИ - НЕ, реализующих соответствующие булевые функции двух переменных, представлены на рис. 11.2.

Под глубиной (числом уровней) КС понимается максимальное число логических элементов, расположенных на пути следования сигнала от входов КС к ее выходу. Глубина КС оказывает существенное влияние на быстродействие КС, так как каждый логический элемент обладает внутренней задержкой распространения сигнала. Одно- и двухуровневые КС обладают максимальным быстродействием. Однако они не всегда могут быть использованы, поскольку число входов реальных логических элементов в интегральном исполнении ограничено.

Если КС реализует одну булеву функцию, то она называется одновыходовой КС (рис. 11.3). Если КС реализует совокупность булевых функций, то она называется многовыходовой КС.

Комбинационным схемам соответствуют схемы без обратных связей (под обратной связью понимается соединение выхода некоторого логического элемента со своим входом, возможно» через цепочку других логических элементов (рис. 11.4)).

|

|

|

Логические элементы, используемые для построения КС, характеризуются определенными техническими параметрами, среди которых нас будут интересовать коэффициент объединения по входу  коэффициент объединения по выходу V (коэффициент разветвления) и задержка сигнала

коэффициент объединения по выходу V (коэффициент разветвления) и задержка сигнала  в логическом элементе.

в логическом элементе.

Система функций, реализуемая выбранной для синтеза схем совокупностью логических элементов, всегда должна быть функционально полной, т. е. допускать реализацию любой булевой функции на основе принципа суперпозиции. Если в качестве системы функций выбраны функции И, ИЛИ, НЕ, то считают, что реализован булев базис. Проектирование КС в булевом базисе

Рис. 11.1

Рис. 11.2

Рис. 11.3

Рис. 11.4

наиболее просто, так как методы минимизации булевых функций в основном ориентированы на него. Поэтому, как правило, на первом этапе КС проектируется в булевом базисе с последующим переходом в заданный базис. Если выбраны функции НЕ — И или НЕ - ИЛИ, то считают, что реализуется универсальный или монофункциональный базис. Для удобства проектирования в различных системах элементов возможна реализация и смешанного базиса.

Конструктивно логические элементы объединяются в единые корпуса — интегральные микросхемы (ИМС). В общем случае, под интегральной микросхемой понимается микроэлектронное изделие, имеющее высокую плотность упаковки элементов и соединений между ними; при этом все элементы выполнены нераздельно и электрически соединены между собой таким образом, что с точки зрения спецификации, испытаний, поставки и эксплуатации изделие рассматривается как единое целое. В одном корпусе ИМС могут быть один, два и более логических элементов. Это обстоятельство накладывает ограничение на качество проектирования КС, а именно: коэффициент использования логических элементов в корпусах не должен быть низким. Например, если при проектировании КС применяется ИМС, содержащая в своем корпусе три логических элемента, то Оптимальный вариант структуры КС Должен использовать все три элемента. Последним иногда пренебрег гают, учитывая в первую очередь требования технологического порядка.

Число логических элементов, объединяемых в один корпус ИМС, характеризует степень интеграции логических элементов. Степень иитеграции влияет ни надежность, габаритные размеры, энергопотребляемость проектируемых КС, Различают ИМС малой, средней, большой и сверхбольшой степени интеграции, По критериям принятым в 70х годах обычно при оценке степени интеграции ИМС учитывается число логических двухвходовых элементов И, реализуемых  одном кристалле ИМС: малые интегральные схемы — до 10 элементов, средние интегральные схемы — до 100 элементов, большие интегральные схемы (БИС) — до 1000 элементов и сверхбольшие интегральные схемы (СБИС) — более 1000 логических двухвходовых элементов И, размещаемых на одном кристалле ИМС.

одном кристалле ИМС: малые интегральные схемы — до 10 элементов, средние интегральные схемы — до 100 элементов, большие интегральные схемы (БИС) — до 1000 элементов и сверхбольшие интегральные схемы (СБИС) — более 1000 логических двухвходовых элементов И, размещаемых на одном кристалле ИМС.

В настоящее время в связи с общим повышением уровня технологии более часто используют другие оценки: до 100 000 вентилей — БИС, более 100 000 вентилей — СБИС.

Коэффициент объединения  по входу логического элемента ИМС задает максимальное число логических элементов, выходы которых могут быть объединены на входе данного элемента.

по входу логического элемента ИМС задает максимальное число логических элементов, выходы которых могут быть объединены на входе данного элемента.

Коэффициент объединения  по выходу (коэффициент разветвления) логического элемента ИМС задает максимальное число входов логических элементов, которые могут быть соединены с выходом данного логического элемента без нарушения режима его работы.

по выходу (коэффициент разветвления) логического элемента ИМС задает максимальное число входов логических элементов, которые могут быть соединены с выходом данного логического элемента без нарушения режима его работы.

Если некоторый логический элемент КС оказался перегруженным по выходу (после окончания проектирования  то необходимо произвести эквивалентное преобразование структуры КС с целью его разгрузки. Это преобразование сводится либо к введению в КС специальных усилителей-формирователей, либо к (Дублированию данного логического элемента.

то необходимо произвести эквивалентное преобразование структуры КС с целью его разгрузки. Это преобразование сводится либо к введению в КС специальных усилителей-формирователей, либо к (Дублированию данного логического элемента.

Рис. 11.5

Задержка  логического элемента характеризует промежуток времени между моментами установления сигналов на входах и выходах логического элемента. Распространение сигнала по КС в зависимости от задержек логических элементов, через которые он проходит, характеризует быстродействие КС, Прохождение сигналов по различным путям в КС вызывает появление различных задержек, что может послужить причиной неустойчивого функционирования КС.

логического элемента характеризует промежуток времени между моментами установления сигналов на входах и выходах логического элемента. Распространение сигнала по КС в зависимости от задержек логических элементов, через которые он проходит, характеризует быстродействие КС, Прохождение сигналов по различным путям в КС вызывает появление различных задержек, что может послужить причиной неустойчивого функционирования КС.

Современные средства вычислительной техники собираются из ИМС, типовых как по физическим принципам функционирования, так и по выполняемым логическим функциям.

Основные требования к комплекту ИМС следующие:

1) ИМС комплекта должны обеспечивать возможность построения различных устройств и систем обработки цифровой информации;

2) число различных типов ИМС должно быть оптимальным, чтобы обеспечивалась простота эксплуатации сложных систем и взаимозаменяемость их частей;

3) в комплекте должны быть предусмотрены ИМС, которые не выполняют логических функций, а согласуют нагрузочные характеристики логических элементов и обеспечивают формирование электрических сигналов;

4) ИМС комплекта должны быть технологичными в изготовлении и удобными для проверки их электрических параметров;

5) комплект ИМС должен быть функционально полным;

6) комплект ИМС должен содержать специальные ИМС, предназначенные для построения управляющих цепей, запоминающих устройств, цепей связи запоминающих и логических устройств, согласования электромеханических устройств (реле, переключателей, механизмов перфорации и печати) и логических устройств, связи различных устройств с устройствами ввода-вывода информации, индикации информационных состояний и генерации высокостабильных тактовых сигналов.

Вопрос 30

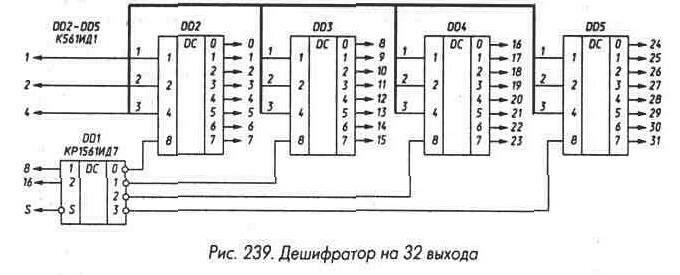

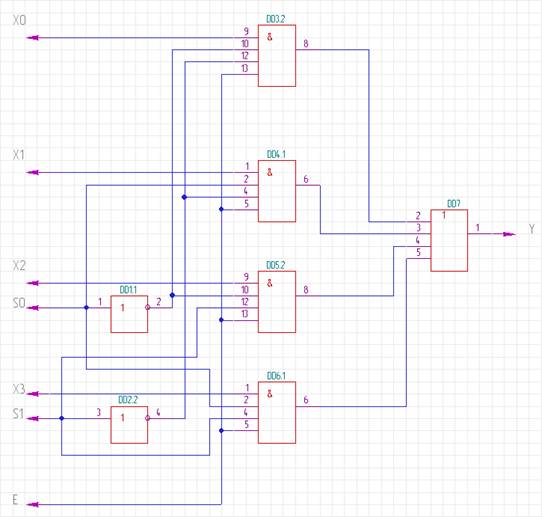

В компьютеризированных системах управления, ЭВМ и цифровой технике одними из важнейших элементов построения электронных микросхем являются дешифраторы.

Так, дешифратор (или декодер) – это логическое комбинационное устройство, служащее для преобразования двойного двоичного кода в сигнал управления в десятичной системе исчисления на одном из выходов.

Принцип работы дешифратора

Обычно дешифратор имеет n-входов и 2n выходов, при этом n — разрядность дешифрируемого кода. Определенной комбинации на входе соответствует активный сигнал на одном из выходов, или при сигнале «00» — мы имеем «1» на нулевом выходе схемы; при «01» имеем — «1» на первом выходе, сигнал «10» трансформируется в 1 – на втором выходе и т.д. Другими словами, эти элементы схем могут преобразовывать двоичный код в различные системы исчисления (это может быть десятичная, шестнадцатеричная и пр.), поскольку все зависит от конкретной задачи, выполняемой микросхемой.

В стандартные типы дешифраторов входят модели на 4, 8 и 16 выходов, при этом на выходе — 2, 3 и 4 разрядов входного кода. Входы дешифраторов называют часто адресными, и на схемах нумеруют 1,2,4,8, при этом цифра соответствует весу двоичного кода. Сигнал на выходе 1,2,4,8 устанавливает номер активного выхода. С1,С2 – входы разрешения (или стробирования), которые работают с условием «и». Сигнал на этом входе сообщает о моменте срабатывания дешифратора. Также их можно использовать для увеличения разрядности логических устройств.

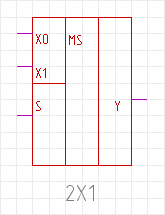

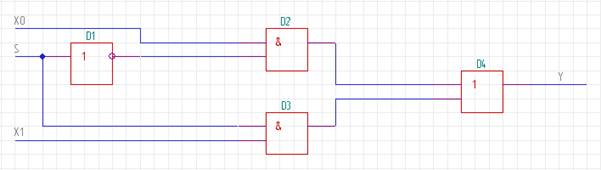

Мультиплексорами называются устройства, которые позволяют подключать несколько входов к одному выходу. Демультиплексорами называются устройства, которые позволяют подключать один вход к нескольким выходам.

Устройство

Рис. 1.1. Мультиплексор на 2 входа

Файл:MS-4x1.PNG

Рис. 1.2. Мультиплексор на 4 входа

Схематически мультиплексор можно изобразить в виде коммутатора, обеспечивающего подключение одного из нескольких входов (их называют информационными) к одному выходу устройства. Коммутатор обслуживает управляющая схема, в которой имеются адресные входы и, как правило, разрешающие (стробирующие).

Рис. 1.3. Функциональная схема мультиплексора на 2 входа

Рис. 1.4. Функциональная схема мультиплексора на 4 входа

Сигналы на адресных входах определяют, какой конкретно информационный канал подключен к выходу. Если между числом информационных выходов n{\displaystyle n\!\,} и числом адресных входов m{\displaystyle m\!\,} действует соотношение n=2m{\displaystyle n=2^{m}\!\,}, то такой мультиплексор называют полным. Если n<2m{\displaystyle n<2^{m}\!\,}, то мультиплексор называют неполным.

Разрешающие входы используют для расширения функциональных возможностей мультиплексора. Они используются для наращивания разрядности мультиплексора, синхронизации его работы с работой других узлов. Сигналы на разрешающих входах могут разрешать, а могут и запрещать подключение определенного входа к выходу, то есть могут блокировать действие всего устройства.

Вопрос 31

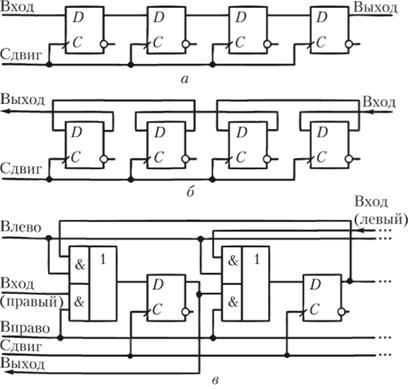

Регистром называют устройство, осуществляющее прием, хранение и выдачу двоичных чисел в определенном коде. В отличие от запоминающих устройств в регистрах информация хранится не более нескольких тактов. Запоминающими элементами в регистрах служат триггеры, число которых равно числу разрядов хранимых чисел. Схемы регистров служат для ввода и вывода хранимых чисел, преобразования их кодов, сдвига кодов на то или иное число разрядов. Регистры подразделяют на параллельные (регистры памяти), последовательные (регистры сдвига) и параллельно-последовательные (например, ввод – в параллельном коде, а вывод – в последовательном, и наоборот).

В регистрах памяти числа вводят и выводят в параллельном коде, в регистрах сдвига – в последовательном (разряд за разрядом), поэтому в регистрах памяти число вводится (выводится) за один такт, а в регистрах сдвига – за п тактов, где п – разрядность чисел.

По способу ввода–вывода различают регистры однофазного и парафазного типа. В однофазных ввод (и вывод) возможен только в прямом или обратном коде, в парафазных – как в прямом, так и в обратном кодах. Вид осуществляемого ввода (вывода) определяется сигналами управления.

Исходным состоянием регистра является нулевое. После ввода двоичного числа Х1 триггеры переходят в состояния, соответствующие значениям разрядов числа X1 которое хранится до момента передачи его другому устройству либо до ввода в регистр другого числа Х2.

В последовательных регистрах при каждом сдвигающем (обычно синхронизирующем) импульсе происходит сдвиг кода хранимого числа влево или вправо на один разряд. При этом число выводится в последовательном коде разряд за разрядом, начиная с младшего (при сдвиге вправо) или старшего (при сдвиге влево). В информационной технике регистры сдвига применяют для преобразования последовательного кода в параллельный (и обратно), для умножения и деления многоразрядных чисел, построения распределителей импульсов, преобразователей кодов и т.д.

В параллельных регистрах схемы разрядов не обмениваются данными между собой. Общими для разрядов обычно являются цепи синхронизации (тактирования), сброса (установки), разрешения выхода (выдачи данных) или приема, т.е. цепи управления.

Для современнойсхемотехники характерно построение регистров именно на D-триггерах, преимущественно с динамическим управлением. Многие регистры имеют выходы с третьим состоянием, а некоторые – мощные выходные каскады и относятся к числу буферных. Такие регистры способны работать на большую емкостную или низкоомную активную нагрузку. Это обеспечивает их работу непосредственно на магистраль.

Регистровые файлы

Из параллельных регистров составляют блоки регистровой памяти – регистровые файлы. Такие блоки обеспечивают хранение нескольких слов с возможностью независимой и одновременной записи одного слова и чтения другого. Управляющие входы обеспечивают выбор того или иного регистра и разрешают запись в него слова данных (напомним, что в литературе, посвященной цифровой схемотехнике, под "словом" понимается двоичное число).

Размерность регистровой памяти можно наращивать, составляя из нескольких ИС блок памяти. При наращивании числа хранимых слов выходы отдельных ИС с тремя состояниями соединяются в одной точке. При наращивании разрядности слова входы разрешения и адресации нескольких ИС соединяют параллельно, тогда выходы ИС в совокупности дают единое информационное слово.

Регистры сдвига

Последовательные (сдвигающие) регистры представляют собой цепочку триггеров, связанных цепями переноса.

В однотактных регистрах со сдвигом на один разряд вправо (рис. 3.36, а) слово сдвигается при поступлении синхронизирующего сигнала. При каждом импульсе сдвига происходит перезапись содержимого предыдущего триггера в последующий и запись очередного разряда в крайний левый триггер. В результате за четыре такта в регистр будет занесено четырехразрядное слово. Причем первый (по времени поступления) разряд будет занесен в крайний правый регистр.

Рис. 3.36. Схемы регистров сдвига вправо (а), влево (б) и реверсивного (в)

В регистре со сдвигом влево (рис. 3.36, б) заполнение его данными происходит справа налево. В реверсивном регистре (рис. 3.36, в) имеются связи триггеров с обоими соседними разрядами. С помощью команд "влево" и "вправо" разрешается прохождение сигнала на вход триггера либо через один, либо через другой конъюнктор. Через нижний конъюнктор проходит сигнал с выхода левого триггера, а через верхний – с выхода правого триггера (на рисунке не показан). Естественно, что команды "влево" и "вправо" одновременно подаваться не могут.

Вопрос 32

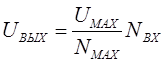

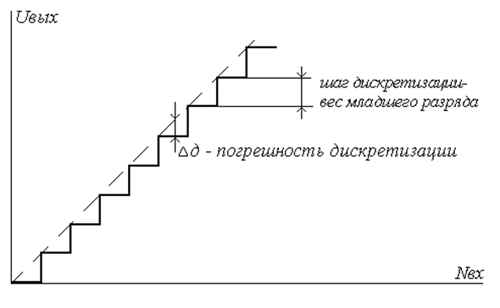

Цифро-аналоговый преобразователь (ЦАП) - это устройство для преобразования цифрового кода в аналоговый сигнал по величине, пропорциональной значению кода.

ЦАП применяются для связи цифровых управляющих систем с устройствами, которые управляются уровнем аналогового сигнала. Также, ЦАП является составной частью во многих структурах аналого-цифровых устройств и преобразователей.

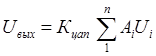

ЦАП характеризуется функцией преобразования. Она связывает изменение цифрового кода с изменением напряжения или тока. Функция преобразования ЦАП выражается следующим образом

, где

, где

Uвых - значение выходного напряжения, соответствующее цифровому коду Nвх, подаваемому на входы ЦАП.

Uмах - максимальное выходное напряжение, соответствующее подаче на входы максимального кода Nмах

Величину Кцап, определяемую отношением  , называют коэффициентом цифроаналогового преобразования. Несмотря на ступенчатый вид характеристики, связанный с дискретным изменением входной величины (цифрового кода), считается, что ЦАП являются линейными преобразователями.

, называют коэффициентом цифроаналогового преобразования. Несмотря на ступенчатый вид характеристики, связанный с дискретным изменением входной величины (цифрового кода), считается, что ЦАП являются линейными преобразователями.

Если величину Nвх представить через значения весов его разрядов, функцию преобразования можно выразить следующим образом

, где

, где

i - номер разряда входного кода Nвх; Ai - значение i-го разряда (ноль или единица); Ui – вес i-го разряда; n – количество разрядов входного кода (число разрядов ЦАП).

Вес разряда определяется для конкретной разрядности, и вычисляется по следующей формуле

, где

, где

UОП -опорное напряжение ЦАП

Принцип работы большинства ЦАП - этосуммирование долей аналоговых сигналов (веса разряда), в зависимости от входного кода.

Вопрос 33

Операти́внаяпа́мять (англ. RandomAccessMemory, RAM, память с произвольным доступом) или операти́вноезапомина́ющееустро́йство (ОЗУ); комп. жарг. па́мять, операти́вка — энергозависимая часть системы компьютерной памяти, в которой во время работы компьютера хранится выполняемый машинный код (программы), а также входные, выходные и промежуточные данные, обрабатываемые процессором.

Обмен данными между процессором и оперативной памятью производится:

· непосредственно;

· через сверхбыструю память 0-го уровня — регистры в АЛУ, либо при наличии аппаратного кэша процессора — через кэш.

Содержащиеся в современной полупроводниковой оперативной памяти данные доступны и сохраняются только тогда, когда на модули памяти подаётся напряжение. Выключение питания оперативной памяти, даже кратковременное, приводит к искажению либо полному разрушению хранимой информации.

Энергосберегающие режимы работы материнской платы компьютера позволяют переводить его в режим сна, что значительно сокращает уровень потребления компьютером электроэнергии. В режиме гибернации питание ОЗУ отключается. В этом случае для сохранения содержимого ОЗУ операционная система (ОС) перед отключением питания записывает содержимое ОЗУ на устройство постоянного хранения данных (как правило, жёсткий диск). Например, в ОС WindowsXPсодержимое памяти сохраняется в файл hiberfil.sys, в ОС семейства Unix — на специальный swap-раздел жёсткого диска.

В общем случае, ОЗУ содержит программы и данные ОС и запущенные прикладные программы пользователя и данные этих программ, поэтому от объёма оперативной памяти зависит количество задач, которые одновременно может выполнять компьютер под управлением ОС.

Оперативное запоминающее устройство, ОЗУ — техническое устройство, реализующее функции оперативной памяти.

ОЗУ может изготавливаться как отдельный внешний модуль или располагаться на одном кристалле с процессором, например, в однокристальных ЭВМ или однокристальных микроконтроллерах.

Вопрос 34

Аналого-цифровой преобразователь (АЦП, англ. Analog-to-digitalconverter, ADC) — устройство, преобразующее входной аналоговый сигнал в дискретный код (цифровой сигнал). Обратное преобразование осуществляется при помощи ЦАП (цифро-аналогового преобразователя, DAC).

Как правило, АЦП — электронное устройство, преобразующее напряжение в двоичный цифровой код. Тем не менее, некоторые неэлектронные устройства с цифровым выходом, следует также относить к АЦП, например, некоторые типы преобразователей угол-код. Простейшим одноразрядным двоичным АЦП является компаратор.

Дата добавления: 2018-04-05; просмотров: 616; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!