Минимизация булевых выражений

Московский государственный технический университет

имени Н. Э. Баумана

И.А. Васильев, Е.С. Люминарская

ИССЛЕДОВАНИЕ И ПРОЕКТИРОВАНИЕ КОМБИНАЦИОННЫХ ЛОГИЧЕСКИХ УСТРОЙСТВ В ПРОГРАММНОЙ СРЕДЕ MULTISIM

Учебно-методическое пособие для подготовки к лабораторной работе по курсу «Электротехника и электроника»

Москва

(С) 2017 МГТУ им. Н.Э. БАУМАНА

УДК 621.3

ББК 31.2

Рецензент

кандидат технических наук, доцент

О.И. Мисеюк

| Васильев И.А., Люминарская Е.С. | |

| Исследование и проектирование комбинационных устройств в программном комплексе Multisim: учебно-методическое пособие для подготовки к лабораторной работе по курсу «Электротехника и электроника» / И.А. Васильев, Е.С. Люминарская — издательство МГТУ им. Н.Э. Баумана, 2017. – 29 с.: ил. | |

| ISBN Изложены краткие сведения о логических элементах и цифровых схемах логических цепей. Дано описание лабораторной работы. Приведен порядок выполнения работы. Для студентов 3 и 4 курсов факультетов РК, МТ, СМ, Э МГТУ им. Н.Э. Баумана, изучающих дисциплину «Электротехника и электроника». Рекомендовано учебно-методической комиссией НУК ФН МГТУ им. Н.Э. Баумана.

| |

УДК 621.3

ББК 31.2

©Васильев И.А., Люминарская Е.С., 2017

© МГТУ им. Н.Э. Баумана, 2017

Оглавление

Предисловие ………………………………………………………………………4

1. Основные теоретические сведения……………………………………………5

|

|

|

1.1. Логические элементы, таблицы истинности,

булевы выражения…………………………………………………………….5

1.2. Запись булевых выражений по таблицам истинности…………………8

1.3. Минимизация булевых выражений…………………………………….9

1.4. Перевод логической функции в базис И-НЕ………………………….12

2. Методические указания по работе в программной среде MULTISIM……..14

3. Задание и порядок выполнения работы……………………………………..19

3.1.Исследование двухвходовых логических элементов………………….19

3.2. Исследование четырехвходового логического устройства…………..20

3.3. Проектирование комбинационного логического устройства в программной среде Multisim……..................................................................21

Требования к отчету……………………………………………………………..25

Заключение……………………………………………………………………….26

Вопросы для самоконтроля……………………………………………………..26

Литература……………………………………………………………………….27

Приложение 1…………………………………………………………………….28

Приложение 2…………………………………………………………………….29

ПРЕДИСЛОВИЕ

Основу всех современных устройств цифровой электроники составляют цифровые схемы логических цепей, составными частями которых являются логические элементы. Изучение простейших логических элементов и более сложных комбинационных логических устройств открывает путь к пониманию принципов работы цифровых приборов.

|

|

|

Выполнение данной лабораторной работы предусмотрено учебным планом дисциплины «Электротехника и электроника» для студентов 3 и 4 курсов факультетов РК, МТ, Э, СМ.

Целью лабораторной работы является исследование и проектирование логических устройств, приобретение навыков разработки указанных устройств в программной среде Multisim.

При исследовании двухвходового и четырехвходового логических элементов необходимо для заданной схемы получить таблицу истинности, записать булево выражение, минимизировать его по карте Карно и записать в базисе И-НЕ. При синтезе комбинационного устройства по заданной таблице истинности необходимо получить выражение в базисе И-НЕ и построить логическую схему.

Приобретаемые умения – анализ и синтез логических схем, построение принципиальной схемы комбинационного логического устройства в программном комплексе Multisim.

Приобретаемые знания – основы функционирования базовых логических элементов; реализация основных и других функций на элементе И-НЕ; запись булевых выражений по таблицам истинности; способы минимизации булевых выражений.

|

|

|

Лабораторная работа

«Исследование и проектирование комбинационных логических устройств в программной среде Multisim »

Цель работы: исследование и проектирование логических устройств, приобретение навыков разработки указанных устройств в программной среде Multisim.

ОСНОВНЫЕ ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ

Логические элементы, таблицы истинности, булевы выражения

Логические элементы – это элементарные цифровые устройства, которые используются для обработки информации в цифровой последовательности сигналов высокого – «1» и низкого – «0» уровней.

Техническое выполнение логических элементов осуществляться на реле, транзисторах, диодах и др. В настоящее время широкое распространение получили логические элементы в виде цифровых интегральных микросхем.

Функциональные свойства логических элементов и устройств описываются таблицей истинности и булевым уравнением. В таблице истинности логического элемента указываются все возможные значения сигнала на выходе для любой комбинации сигналов на входе. Таким образом, таблица истинности дает исчерпывающую характеристику работы логического элемента, т.е. описывает логическую функцию. Логическая функция, представленная символами алгебры Буля, выражается булевым уравнением.

|

|

|

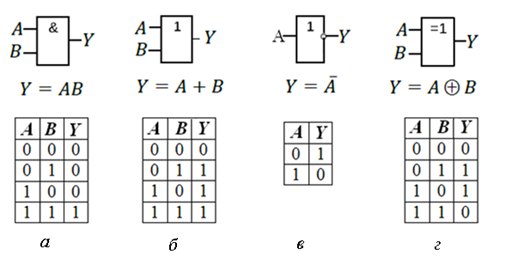

На принципиальной схеме логический элемент принято изображать прямоугольником, внутри которого ставится символ указателя функции. С левой стороны прямоугольника линиями показываются входы, с правой стороны – выход элемента.

Базовыми логическими элементами являются: И, ИЛИ, НЕ, исключающее ИЛИ (их условные обозначения по ГОСТу приведены в приложении 1). С помощью этих элементов можно реализовать логические функции любой сложности. Может лишь потребоваться большее или меньшее количество логических элементов.

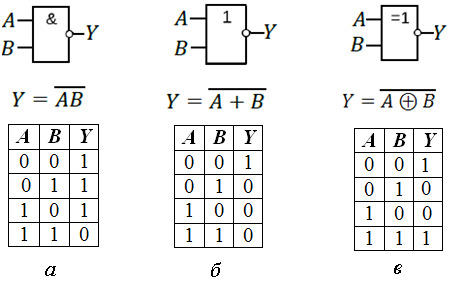

На рис. 1 представлены принципиальные схемы, булевы выражения и таблицы истинности для элементов: И – «конъюнктор»,  ; ИЛИ – «дизъюнктор» ,

; ИЛИ – «дизъюнктор» ,  ; НЕ – инвертор,

; НЕ – инвертор,  ; исключающее ИЛИ,

; исключающее ИЛИ,

Рис.1. Логические элементы:

a – И; б– ИЛИ; в – НЕ; г– исключающее ИЛИ

К более сложным логическим элементам относятся такие элементы как И-НЕ, ИЛИ-НЕ, исключающее ИЛИ-НЕ. Данные элементы являются комбинацией базовых логических элементов.

Рис.2. Логические элементы:

a – И-НЕ; б – ИЛИ-НЕ; исключающее ИЛИ-НЕ

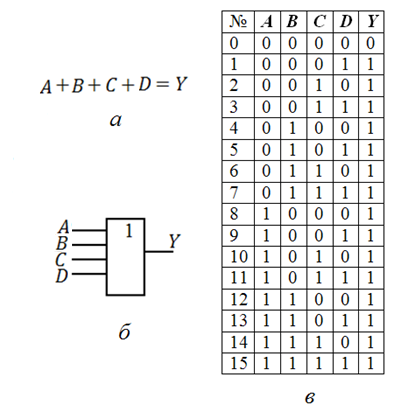

На практике часто применяются логические элементы с количеством входов больше двух. На рис. 3 приведены булево выражение, принципиальная схема и таблица истинности элемента ИЛИ с четырьмя входами. Из таблицы истинности видно, что из-за наличия четырех входов число возможных комбинаций  возрастает до 16.

возрастает до 16.

Рис.3. Логический элемент ИЛИ с четырьмя входами:

a –булево выражение, б –принципиальная схема, в –таблица истинности

1.2 Запись булевых выражений по таблицам истинности

Булевы выражения встречаются в двух основных формах – дизъюнктивной нормальной форме (ДНФ) и конъюнктивной нормальной форме (КНФ). ДНФ представляет собой сумму произведений, КНФ – произведение сумм.

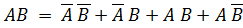

Обратимся к таблице истинности, показанной на рис. 4. Запишем булево выражение для заданной таблицы в ДНФ. В таблице курсивом выделены те строки, в которых комбинации переменных на входе дают единицу на выходе. Представим все указанные единицы в виде произведения всех четырех элементов. Например, при заданных значениях элементов в строке №1 выражение  равно 1. Для оставшихся строк 3, 5, 7, 8, 9 аналогичные выражения имеют вид

равно 1. Для оставшихся строк 3, 5, 7, 8, 9 аналогичные выражения имеют вид  . Далее полученные выражения свяжем логической функцией ИЛИ. В результате для приведенной таблицы истинности получим следующее булево выражение

. Далее полученные выражения свяжем логической функцией ИЛИ. В результате для приведенной таблицы истинности получим следующее булево выражение

(1)

(1)

| № | A | B | C | D | Y |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 |

| 2 | 0 | 0 | 1 | 0 | 0 |

| 3 | 0 | 0 | 1 | 1 | 1 |

| 4 | 0 | 1 | 0 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 | 1 |

| 6 | 0 | 1 | 1 | 0 | 0 |

| 7 | 0 | 1 | 1 | 1 | 1 |

| 8 | 1 | 0 | 0 | 0 | 1 |

| 9 | 1 | 0 | 0 | 1 | 1 |

| 10 | 1 | 0 | 1 | 0 | 0 |

| 11 | 1 | 0 | 1 | 1 | 0 |

| 12 | 1 | 1 | 0 | 0 | 0 |

| 13 | 1 | 1 | 0 | 1 | 0 |

| 14 | 1 | 1 | 1 | 0 | 0 |

| 15 | 1 | 1 | 1 | 1 | 0 |

Рис.4. Таблица истинности для построения булева выражения

Иногда приходится выполнять процедуру, обратную рассмотренной, т.е. по булеву выражению восстанавливать таблицу истинности. Запишем таблицу истинности для выражения

(2)

(2)

В данном примере единицу на выходе должны давать комбинации входных сигналов  и

и  . Выражение

. Выражение  при

при  , а выражение

, а выражение  при

при  . Необходимо отметить, что для комбинации входных сигналов

. Необходимо отметить, что для комбинации входных сигналов  единица на выходе получается вне зависимости от сигнала на входе

единица на выходе получается вне зависимости от сигнала на входе  . Следовательно, логическая единица для данной комбинации записывается не в одну, а в две строки таблицы с разными значениями сигнала В. Таблица истинности для выражения (2) представлена на рис. 5.

. Следовательно, логическая единица для данной комбинации записывается не в одну, а в две строки таблицы с разными значениями сигнала В. Таблица истинности для выражения (2) представлена на рис. 5.

| № | A | B | C | Y |

| 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 2 | 0 | 1 | 0 | 1 |

| 3 | 0 | 1 | 1 | 0 |

| 4 | 1 | 0 | 0 | 0 |

| 5 | 1 | 0 | 1 | 0 |

| 6 | 1 | 1 | 0 | 0 |

| 7 | 1 | 1 | 1 | 1 |

Рис. 5. Таблица истинности, построенная на основе булевого выражения

Минимизация булевых выражений

Логическое устройство, построенное на базе исходного булевого выражения, не является оптимальным с точки зрения количества используемых элементарных элементов. Минимизация булева выражения может быть достигнута при анализе таблицы истинности с помощью теорем булевой алгебры или на основе использования карт Карно.

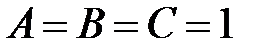

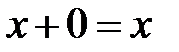

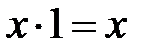

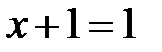

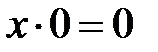

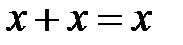

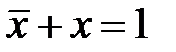

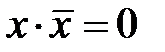

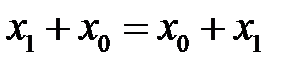

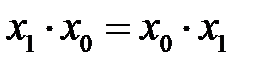

Рассмотрим минимизацию булевых выражений с помощью теорем булевой алгебры. Эти теоремы отражают связи, существующие между операциями, выполненными над логическими переменными. Основные теоремы представляются следующими выражениями:

1.  ,

,  ;

;

2.  ,

,  ;

;

3.  ,

,  ;

;

4.  ,

,  (3)

(3)

5.  ,

,  ;

;

6.  ;

;  ;

;

7.  .

.

Выражения №6 приведенных формул называют законами де Моргана.

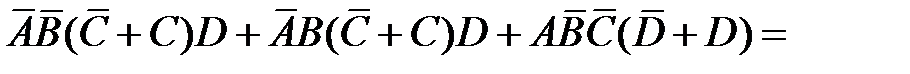

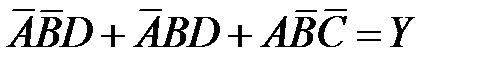

Для минимизации выражения (1) последовательно используем выражения 5, 7, 4, 1

.

.

В результате получим следующую булеву функцию

.

.

Проводим повторную группировку

.

.

Таким образом, после минимизации булева функция (1) принимает следующий вид

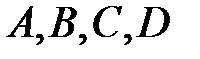

Теперь рассмотрим минимизацию выражения (1) с помощью карт Карно. Карты Карно представляют собой систему графического представления и упрощения булевых выражений.

В карте Карно переменные по горизонтали и вертикали располагаются согласно коду Грея. В коде Грея соседние элементы отличаются только в одном бите. Код Грея для одной переменной A имеет вид 0 1. Для двух переменных AB код Грея – AB = 00 10 11 10, что соответствует булевому выражению

В общем случае число квадрантов карт равно числу возможных комбинаций переменных. Выражение (1) имеет четыре элемента  . Таблица истинности для четырех элементов включает 16 возможных комбинаций, которые на рисунке 4 представлены 16 квадрантами карты. Нанесем на карту шесть единиц, которые соответствуют шести слагаемым в заданном булевом выражении. Соседние единицы объединим в группы по две и четыре единицы (рис.6.)

. Таблица истинности для четырех элементов включает 16 возможных комбинаций, которые на рисунке 4 представлены 16 квадрантами карты. Нанесем на карту шесть единиц, которые соответствуют шести слагаемым в заданном булевом выражении. Соседние единицы объединим в группы по две и четыре единицы (рис.6.)

Рис.6. Карта Карно

Количество слагаемых в минимизированном булевом выражении равно числу образовавшихся групп. В верхнем контуре попарно убираем  и

и  ,

,  и

и  . В итоге верхний контур дает член

. В итоге верхний контур дает член  . Из нижнего контура убираем

. Из нижнего контура убираем  и

и  . После этого в нем остается член

. После этого в нем остается член  . В результате упрощенное булево выражение (1) в ДНФ принимает вид

. В результате упрощенное булево выражение (1) в ДНФ принимает вид

.

.

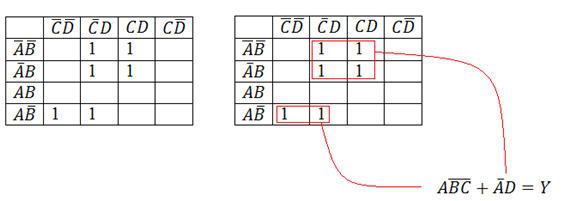

При минимизации булевых выражений по карте Карно необходимо объединять в контуры не только соседние, но и крайние члены карты. Например, для булевого выражения

карта Карно и минимизированное булево выражение имеют следующий вид

Рис.7. Карта Карно

Для упрощения булевых выражений с двумя, тремя и четырьмя переменными применяют одинаковые процедуры. Необходимо отметить, чем больше единиц объединяется в контуре, тем больше переменных можно опустить.

Дата добавления: 2022-06-11; просмотров: 79; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!