Последовательный периферийный интерфейс SPI

ИНТЕРФЕЙСЫ МИКРОКОНТРОЛЛЕРОВ.

Цель СР - углубить знания в области используемых в современных МК интерфейсов

Последовательный интерфейс UART/USART

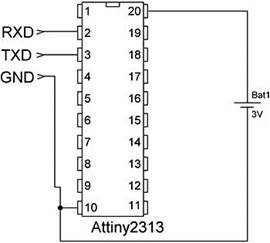

Универсальный асинхронный или универсальный синхронно/асинхронный приемопередатчик (Universal Synchronous/Asynchronous Receiver and Transmitter — UART или USART) — удобный и простой последовательный интерфейс для организации информационного канала обмена микроконтроллера с внешним миром. Способен работать в дуплексном режиме (одновременная передача и прием данных). Он поддерживает протокол стандарта RS-232, что обеспечивает возможность организации связи с персональным компьютером. Изначально использовался в компьютерах для большинства периферийных устройств, таких как плоттер, удаленный принтер, мышь, внешний модем и т. д. До настоящего времени для последовательной связи IBM PC-совместимых компьютеров используются адаптеры с интерфейсом RS-232С (новое название EIA-232D). В современном IBM PC-совместимом компьютере может использоваться до четырех последовательных портов, имеющих логические имена соответственно COM1, COM2, COM3 и COM4. Основой последовательного адаптера является микросхема UART (Universal Asynchronous Receiver/Transmitter) — универсальный асинхронный приемопередатчик. Обычно используется микросхема UART 16550A. Она имеет 16-символьный буфер на прием и на передачу и, кроме того, может использовать несколько каналов прямого доступа в память DMA -habrahabr.ru/post/37455/. При передаче микросхема UART преобразует параллельный код в последовательный и передает его побитно в линию, обрамляя исходную последовательность битами старта, останова и контроля. При приеме данных UART преобразует последовательный код в параллельный (разумеется, опуская служебные символы). Непременным условием правильной передачи (приема) является одинаковая скорость работы приемного и передающего UART, что обеспечивается стабильной частотой кварцевого резонатора. Основным преимуществом последовательной передачи является возможность пересылки данных на большие расстояния, как правило, не менее 30 метров. В IBM PC-совместимых персональных компьютерах из 25 сигналов, предусмотренных стандартом RS-232, используются в соответствии с EIA только 9; таким образом, в данном интерфейсе как правило применяются 9-контактные разъемы типа DB-Shell.В современных компьютерах UART и СОМ порт уже не применяются напрямую, но они получили вторую жизнь для связи с различными нестандартными внешними устройствами в числе которых вошли и устройства на микроконтроллерах. Аппаратная часть при этом стала значительно проще для связи микроконтроллеров друг с другом подключение UART осуществляется по трём линиям: RXD – приём, TXD – передача и GND – общий (минус).

|

|

|

|

|

|

Рис. 1. Схема подключения микроконтроллера Attiny2313

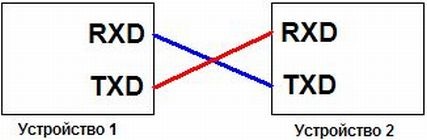

Подключать UART надо, так сказать "наоборот" RXD к TXD, а TXD к RXD как на картинке ниже:

Рис. 2 Схема соединения 2х устройств (общий минус не показан)

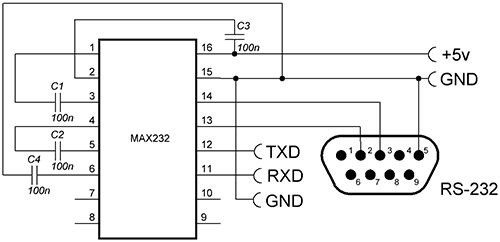

С помощью UART также можно можно связать микроконтроллер и компьютер, но есть одна проблема: у UART интерфейса логические уровни 0 и +5 вольт, а в компьютере логические уровни в интерфейсе RS-232 могут быть от -25 до -3 вольт и от +3 до +25 вольт. Для этого применяют специальный преобразователь уровней на микросхеме MAX232:

Рис. 3. Преобразователь уровней

Все сигналы UART передаются специально выбранными уровнями, обеспечивающими высокую помехоустойчивость связи. Отметим, что данные передаются в инверсном коде (логической единице соответствует низкий уровень, логическому нулю — высокий уровень.

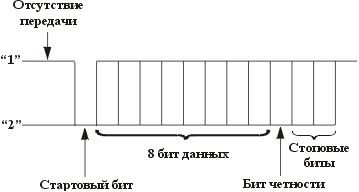

Формат передаваемых данных показан на рисунке 4. Собственно данные (5, 6, 7 или 8 бит) сопровождаются стартовым битом, битом четности и одним или двумя стоповыми битами. Получив стартовый бит, приемник выбирает из линии биты данных через определенные интервалы времени. Очень важно, чтобы тактовые частоты приемника и передатчика были одинаковыми, допустимое расхождение — не более 10%). Скорость передачи по RS-232C может выбираться из ряда: 110, 150, 300, 600, 1200, 2400, 4800, 9600, 19200, 38400, 57600, 115200 бит/с.

|

|

|

Рис.4. Формат данных

Последовательный периферийный интерфейс SPI

Последовательный периферийный трехпроводный интерфейс SPI (Serial Peripheral Interface) предназначен для организации обмена данными между двумя устройствами. С его помощью может осуществляться обмен данными между микроконтроллером и различными устройствами, такими, как цифровые потенциометры, ЦАП/АЦП, FLASH-ПЗУ и др. С помощью этого интерфейса удобно производить обмен данными между несколькими микроконтроллерами AVR. Кроме того, через интерфейс SPI может осуществляться программирование микроконтроллера. Изначально он был придуман компанией Motorola, а в настоящее время используется в продукции многих производителей. Его наименование является аббревиатурой от 'Serial Peripheral Bus', что отражает его предназначение — шина для подключения внешних устройств. Шина SPI организована по принципу 'ведущий-подчиненный'. В качестве ведущего шины обычно выступает микроконтроллер, но им также может быть программируемая логика, DSP-контроллер или специализированная ИС. Подключенные к ведущему шины внешние устройства образуют подчиненных шины. В их роли выступают различного рода микросхемы, в т.ч. запоминающие устройства (EEPROM, Flash-память, SRAM), часы реального времени (RTC), АЦП/ЦАП, цифровые потенциометры, специализированные контроллеры и др.

|

|

|

Главным составным блоком интерфейса SPI является обычный сдвиговый регистр, сигналы синхронизации и ввода/вывода битового потока которого и образуют интерфейсные сигналы. Таким образом, протокол SPI правильнее назвать не протоколом передачи данных, а протоколом обмена данными между двумя сдвиговыми регистрами, каждый из которых одновременно выполняет и функцию приемника, и функцию передатчика. Непременным условием передачи данных по шине SPI является генерация сигнала синхронизации шины. Этот сигнал имеет право генерировать только ведущий шины и от этого сигнала полностью зависит работа подчиненного шины.

Электрическое подключение. Существует три типа подключения к шине SPI, в каждом из которых участвуют четыре сигнала.

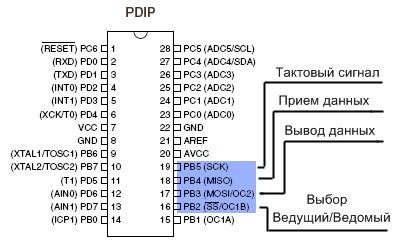

Рис. 5. Расположение выводов интерфейса SPI на микроконтроллере AtMega8

Самое простое подключение, в котором участвуют только две микросхемы, показано на рисунке 6. Здесь, ведущий шины передает данные по линии MOSI синхронно со сгенерированным им же сигналом SCLK, а подчиненный захватывает переданные биты данных по определенным фронтам принятого сигнала синхронизации. Одновременно с этим подчиненный отправляет свою посылку данных. Представленную схему можно упростить исключением линии MISO, если используемая подчиненная ИС не предусматривает ответную передачу данных или в ней нет потребности. Одностороннюю передачу данных можно встретить у таких микросхем как ЦАП, цифровые потенциометры, программируемые усилители и драйверы. Таким образом, рассматриваемый вариант подключения подчиненной ИС требует 3 или 4 линии связи. Чтобы подчиненная ИС принимала и передавала данные, помимо наличия сигнала синхронизации, необходимо также, чтобы линия SS была переведена в низкое состояние. В противном случае, подчиненная ИС будет неактивна. Когда используется только одна внешняя ИС, может возникнуть соблазн исключения и линии SS за счет жесткой установки низкого уровня на входе выбора подчиненной микросхемы. Такое решение крайне нежелательно и может привести к сбоям или вообще невозможности передачи данных, т.к. вход выбора микросхемы служит для перевода ИС в её исходное состояние и иногда инициирует вывод первого бита данных.

Рис. 6. Простейшее подключение к шине SPI

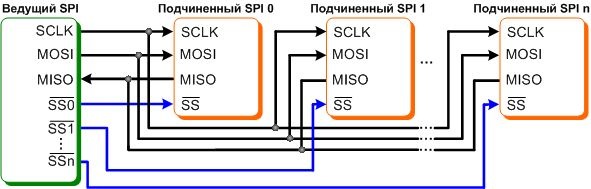

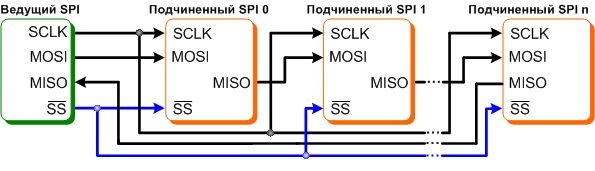

При необходимости подключения к шине SPI нескольких микросхем используется либо независимое (параллельное) подключение (рис. 7), либо каскадное (последовательное) (рис. 8).

Рис. 7. Независимое подключение к шине SPI

Рис. 8. Каскадное подключение к шине SPI

Независимое подключение более распространенное, т.к. достигается при использовании любых SPI-совместимых микросхем. Здесь, все сигналы, кроме выбора микросхем, соединены параллельно, а ведущий шины, переводом того или иного сигнала SS в низкое состояние, задает, с какой подчиненной ИС он будет обмениваться данными. Главным недостатком такого подключения является необходимость в дополнительных линиях для адресации подчиненных микросхем (общее число линий связи равно 3+n, где n-количество подчиненных микросхем). Каскадное включение избавлено от этого недостатка, т.к. здесь из нескольких микросхем образуется один большой сдвиговый регистр. Для этого выход передачи данных одной ИС соединяется со входом приема данных другой, как показано на рисунке 8. Входы выбора микросхем здесь соединены параллельно и, таким образом, общее число линий связи сохранено равным 4. Однако использование каскадного подключения возможно только в том случае, если его поддержка указана в документации на используемые микросхемы. Чтобы выяснить это, важно знать, что такое подключение по-английски называется 'daisy-chaining'. Протокол передачи.

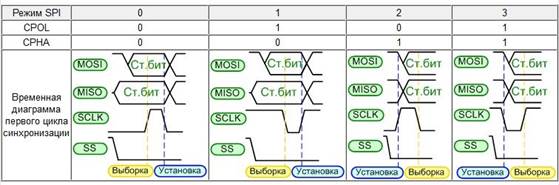

Протокол передачи по интерфейсу SPI предельно прост и, по сути, идентичен логике работы сдвигового регистра, которая заключается в выполнении операции сдвига и, соответственно, побитного ввода и вывода данных по определенным фронтам сигнала синхронизации. Установка данных при передаче и выборка при приеме всегда выполняются по противоположным фронтам синхронизации. Это необходимо для гарантирования выборки данных после надежного их установления. Если к этому учесть, что в качестве первого фронта в цикле передачи может выступать нарастающий или падающий фронт, то всего возможно четыре варианта логики работы интерфейса SPI. Эти варианты получили название режимов SPI и описываются двумя параметрами:

CPOL — исходный уровень сигнала синхронизации (если CPOL=0, то линия синхронизации до начала цикла передачи и после его окончания имеет низкий уровень (т.е. первый фронт нарастающий, а последний — падающий), иначе, если CPOL=1, — высокий (т.е. первый фронт падающий, а последний — нарастающий)); CPHA — фаза синхронизации; от этого параметра зависит, в какой последовательности выполняется установка и выборка данных (если CPHA=0, то по переднему фронту в цикле синхронизации будет выполняться выборка данных, а затем, по заднему фронту, — установка данных; если же CPHA=1, то установка данных будет выполняться по переднему фронту в цикле синхронизации, а выборка — по заднему). Информация по режимам SPI обобщена в таблице.

Ведущая и подчиненная микросхемы, работающие в различных режимах SPI, являются несовместимыми, поэтому, перед выбором подчиненных микросхем важно уточнить, какие режимы поддерживаются ведущим шины. Аппаратные модули SPI, интегрированные в микроконтроллеры, в большинстве случаев поддерживают возможность выбора любого режима SPI и, поэтому, к ним возможно подключение любых подчиненных SPI-микросхем (относится только к независимому варианту подключения). Кроме того, протокол SPI в любом из режимов легко реализуется программно.

Дата добавления: 2021-12-10; просмотров: 33; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!