Архитектура микропроцессоров Intel. Система команд МП серии i80x86.

МП – микроэлектронное программно-управляемое устройство, обрабатывающее цифровую информацию и управляющее процессом обработки информации

Структурная схема элементарной МПС:

Схема отражает магистрально-модульный принцип организации микропроцессорных устройств и систем. Отдельные блоки являются функционально законченными модулями со встроенными схемами управления. Модули связаны коллективными шинами – магистралями; обмен информацией для различных модулей разделен во времени. Микропроцессор работает под воздействием схемы синхронизации и начальной установки, часто выполняемой в виде отдельного кристалла. Периферийные устройства соединены с магистралями через ППА (программируемый периферийный адаптер, обслуживает устройства с параллельным интерфейсом) и ПСА (программируемый связной адаптер, обслуживает устройства с последовательным интерфейсом)

Порт – регистр УВВ, связывающий МП с одним внешним устройством

Интерфейс – совокупность аппаратных средств и управляющих программ для взаимодействия элементов МПС между собой и с внешними устройствами

Стандартный интерфейс – общая схема сопряжения средств обработки информации МП или микро-ЭВМ с внешними устройствами, имеющая унифицированные систему подключения, каналы связи и протокол обмена

Микро-ЭВМ имеет магистрально-модульную конфигурацию, то есть набирается из отдельных модулей, связанных посредством магистралей

Типы магистралей:

- магистраль адреса (МА): информация о номере ячейки памяти, порта интерфейса или ПУ, с которым МП обменивается данными

- магистраль управления (МУ): сигналы, определяющие характер и последовательность действий различных узлов МПС, направление и вид информации, передаваемой по МА и МД; используется также для передачи признаков состояния МП и ПУ

- магистраль данных (МД): обмен информацией внутри МПС и вне ее, определяет формат обрабатываемых данных

Разделение потоков данных производится с помощью буферных регистров с переключающими логическими вентилями

Адресное пространство МПС определяется разрядностью МА (это совокупность адресов в ОЗУ, к которым может обращаться МП)

CISC (Complete Instruction Set Computer – процессор с полным набором команд). CISC-процессоры выполняют большой набор команд (200-300) с развитыми возможностями адресации. Большое количество команд усложняет процесс программирования. Команды CISC-процессоров неоднородны по своей структуре и длине, их сложно декодировать, что увеличивает расход аппаратных ресурсов. Регистры CISC-процессоров могут иметь разное функциональное назначение

RISC (Reduced Instruction Set Computer – процессор с сокращенным набором команд). В основе RISC-архитектуры лежит принцип универсальности: структура команд упрощена, инструкции имеют фиксированную длину, регистры однородны по функциональному назначению. Для процессора это означает простоту реализации блока дешифраторов и соответственно более высокую скорость исполнения инструкций. Количество команд – около 50, каждая команда выполняется за один такт процессора

RISC-процессор выполняет 4-5 команд вместо одной, которую выполняет CISC-процессор. При этом команды RISC выполняются в 10 раз быстрее. Учитывая преимущество производительности RISC, можно было бы предположить, что такие процессоры стали доминировать над CISC, но этого не произошло. Компания Intel стала разрабатывать и выпускать процессоры смешанной архитектуры. Для программистов они по-прежнему обладают CISC-архитектурой, но их ядро имеет RISC-подобную систему команд (это процессорыIntel начиная с i486). Это значит, что ядро процессора выполняет самые простые команды за один цикл, а по обычной технологии CISC интерпретируются более сложные команды. В результате обычные команды выполняются быстро, а более сложные и редкие – медленно. Подобную архитектуру имеют Intel Pentium 4, Celeron, AMD Athlon, AMD Duron, VIA Cyrix. К «чистым» CISC-процессорам относятся Intel 80286 и 80386, а также семейства Itanium. Они обладают несравнимо более высоким быстродействием, что говорит о перспективности использования сокращенного набора команд.

Особенности функционирования процессора.

Большинство современных процессоров для персональных компьютеров, в общем, основаны на той или иной версии циклического процесса последовательной обработки информации, изобретённого Джоном фон Нейманом.

Д. фон Нейман придумал схему постройки компьютера в 1946 году. Важнейшие этапы этого процесса приведены ниже. В различных архитектурах и для различных команд могут потребоваться дополнительные этапы. Например, для арифметических команд могут потребоваться дополнительные обращения к памяти, во время которых производится считывание операндов и запись результатов. Отличительной особенностью архитектуры фон Неймана является то, что инструкции и данные хранятся в одной и той же памяти.

Этапы цикла выполнения:

1. Процессор выставляет число, хранящееся в регистре счётчика команд, на шину адреса, и отдаёт памяти команду чтения;

2. Выставленное число является для памяти адресом; память, получив адрес и команду чтения, выставляет содержимое, хранящееся по этому адресу, на шину данных, и сообщает о готовности;

3. Процессор получает число с шины данных, интерпретирует его как команду (машинную инструкцию) из своей системы команд и исполняет её;

4. Если последняя команда не является командой перехода, процессор увеличивает на единицу (в предположении, что длина каждой команды равна единице) число, хранящееся в счётчике команд; в результате там образуется адрес следующей команды;

5. Снова выполняется п. 1.

Данный цикл выполняется неизменно, и именно он называется процессом (откуда и произошло название устройства).

Во время процесса процессор считывает последовательность команд, содержащихся в памяти, и исполняет их. Такая последовательность команд называется программой и представляет алгоритм работы процессора. Очерёдность считывания команд изменяется в случае, если процессор считывает команду перехода - тогда адрес следующей команды может оказаться другим. Другим примером изменения процесса может служить случай получения команды останова или переключение в режим обработки прерывания.

Режимы работы Intel:

Все процессоры (МП) фирмы Intel., начиная 80286, имеют два существенно отличающихся режима работы, между которыми программным путем обеспечивается достаточно быстрое переключение:

1) Real Mode – реальный режим. В этом режиме возможна адресация до 1 Мб физической памяти. Режим Real Mode поддерживается ОС MS DOS.

2) Protected Mode – защищенный режим. В этом режиме процессор позволяет адресовать до 4 Гб физической памяти и до 16 Тб виртуальной памяти для каждой запущенной на выполнение задачи. Режим Protected Mode поддерживается ОС WINDOWS.

Оба режима основаны на представлении памяти для программиста в виде сегментированной структуры. Сегмент, как отмечалось в предыдущей лекции – это часть (блок) памяти. Каждый сегмент имеет свой адрес. Разработчиками МП предложено несколько типов сегментов, отличающихся назначением. Программа на языке Ассемблер состоит из определения (описания) сегментов и их содержимого. Программист определяет (создает) сегменты и присваивает им имена, а программа – транслятор преобразует каждое имя в номер (адрес) сегмента.

Но физическая память имеет линейную организацию.

Методы адресации.

Адресное пространство.

§ Простая — указание объекта с помощью идентификатора или числа, не имеющего внутренней структуры.

§ Расширенная — доступ к запоминающему устройству с адресным пространством, бо́льшим диапазона адресов, предусмотренного форматом команды.

§ Виртуальная — принцип, при котором каждая программа рассматривается как ограниченное непрерывное поле логической памяти, а адреса этого поля — как виртуальные адреса.

§ Ассоциативная (англ. associative addressing) — точное местоположение данных не указывается, а задаётся значение определённого поля данных, идентифицирующее эти данные.

§ Статическая — соответствие между виртуальными и физическими адресами устанавливается до начала и не меняется в ходе выполнения программы.

§ Динамическая — преобразование виртуальных адресов в физические осуществляется в процессе выполнения программы. Программа при этом не зависит от места размещения в физической памяти и может перемещаться в ней в процессе выполнения.

§ Явная — адресация путём явного задания адресов в программе.

§ Неявная — один или несколько операндов или адресов операндов находятся в фиксированных для данной команды регистрах или ячейках памяти и не требуют явного указания в команде.

§ Абсолютная — адресная часть команды содержит абсолютный адрес.

§ Символическая — адресная часть команды содержит символический адрес.

§ Непосредственная, прямая — адресная часть команды содержит непосредственный (прямой) адрес; адресация путём указания прямых адресов.

§ Косвенная — адресная часть команды содержит косвенный адрес; адресация посредством косвенных адресов.

§ Регистровая — задание адресов операндов в регистрах.

§ Базисная — вычисление адресов в машинных командах относительно содержимого регистра, указанного в качестве базового.

§ Базовая — схема вычисления исполнительного адреса, при которой этот адрес является суммой базового адреса и смещения.

§ Относительная — адресная часть команды содержит относительный адрес.

§ Индексная — формирование исполнительного адреса осуществляется путём добавления к базовому адресусодержимого индексного регистра.

§ Автодекрементная, автоинкрементная (англ. autodecremental, autoincremental addressing — содержимое регистра индекса изменяется (уменьшается или увеличивается) на некоторое число.

§ Постдекрементная, предекрементная, постинкрементная, преинкрементная — автодекрементные и автоинкрементные адресации, при которых уменьшение/увеличение происходит после/до выборки операнда.

§ Стековая (англ. stack addressing) — адресация посредством регистра — указателя стека.

§ Самоопределяющаяся (англ. self-relative addressing) — адресная часть команды содержит самоопределяющийся адрес.

§ Адресация относительно счётчика команд (англ. program counter relative addressing) — адреса в команде указываются в виде разностиисполнительных адресов и адреса исполняемой команды. Такой способ адресации не требует настройки (см. также: Позиционно-независимый код).

§ Микропроцессор, как и всякий алгоритмический исполнитель, имеет определенную систему команд (СК). Количество, назначение, формат команд пользователь (программист) изменить не может, но он может применять эти команды в любом порядке, определяемом логикой решения задачи.

§ Значительная часть команд из упомянутой СК предназначена для обработки данных. Сюда относятся сложение, вычитание, умножение, деление, пересылка данных, сдвиги двоичных кодов и многое другое (эти и другие команды будут рассмотрены далее с соответствующими примерами). Данные, подлежащие обработке в той или иной конкретной команде, принято называть операндами. Операнды могут располагаться в различных местах, в частности, в одном из РОН, в сегменте данных оперативной памяти, в стеке и т.д., и обращение к ним может быть произведено весьма разнообразными способами. Это разнообразие и составляет суть методов адресации.

1.7.Решение задач:

1. Имеется натуральное число n , состоящее из 5 цифр. Требуется вывести все возможные комбинации, полученные в результате перестановки местами этих цифр.

Блок – схема:

2.Составить программу, которая вычисляет выражение y=(3x3-15x2)x+12x2-5

Блок – схема:

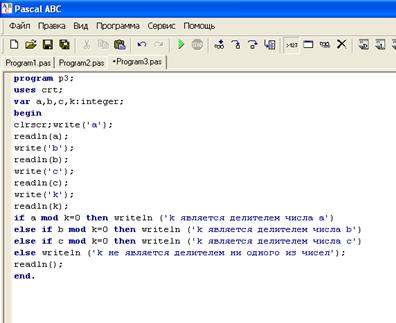

3.Определить, делителем каких чисел a,b,c является число k.

Блок – схема:

4.Написать программу, которая подсчитывает количество часов, минут и секунд в данном числе суток.

Блок – схема:

5.Составить программу, определяющую, является ли число простым

Блок – схема:

6.Двоичное число, введенное пользователем программы преобразовать в десятичное число

Блок – схема:

Дата добавления: 2018-02-18; просмотров: 1637; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!